Fターム[5M024AA08]の内容

Fターム[5M024AA08]に分類される特許

1 - 7 / 7

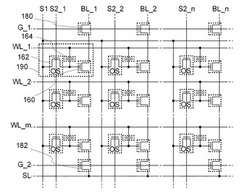

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】多値書き込みを行う半導体装置、及び半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体である酸化物半導体材料を用いることで、長期間にわたって情報を保持することが可能である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

半導体メモリ装置

【課題】本発明は、半導体メモリ装置のパワーダウン装置のパワーダウンモード又はセルフリフレッシュモードにおいて、漏れ電流を減少させるための半導体メモリ装置を提供する。

【解決手段】本発明は、バルク端子に第1の電圧が印加されるMOSトランジスタ;及び、前記MOSトランジスタのソース端子に接続され、パワーダウンモードイネーブル信号及びセルフリフレッシュモードイネーブル信号を受信して、パワーダウンモード又はセルフリフレッシュモードでは、前記ソース端子に第2の電圧を印加し、その他のモードでは、前記ソース端子に第1の電圧を印加する電流制御部を含む。

(もっと読む)

半導体記憶装置、及びそのセンスアンプ回路

【課題】高集積、低消費電力・高速動作を両立した半導体記憶装置を提供する。

【解決手段】複数のプルダウン回路と一つのプルアップ回路から構成されるセンスアンプ回路を有する。また、複数のプルダウン回路の中、その一つにおいて、プルダウン回路を構成するトランジスタは、他方のプルダウン回路を構成するトランジスタよりも、チャネル長やチャネル幅といった定数が大きいことを特徴とする。さらに、複数のプルダウン回路のうち、トランジスタの定数が大きいプルダウン回路を先に活性化し、その後もう一つのプルダウン回路とプルアップ回路を活性化して読み出しを行う。さらに、データ線と先行駆動するプルダウン回路は、NMOSトランジスタで接続されており、前期NMOSトランジスタを活性化、非活性化することで、前記プルダウン回路の活性化、非活性化を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】 素子構造の微細化・低駆動電圧化によって顕在化したMOSFETの閾値のバラつきによる、DRAMのリフレッシュ不良を抑制する。

【解決手段】 DRAMにおいて、セルトランジスタのバックゲートに印加するバックバイアス電位の設定値を記録する第1の手段と、第1の手段に記録された前記バックバイアス電位の設定値に基づいてバックバイアス電位を生成して、生成したバックバイアス電位を前記バックゲートに供給する第2の手段とを有し、セルトランジスタと同一構造で且つ同一工程で同時に製作されたMOSFETの閾値が、セルトランジスタが具備すべき目標値より大きい場合に、前記目標値に対するバックバイアス電位より浅い値が第2の手段に記録されてなる。

(もっと読む)

セルフリフレッシュを用いた低消費電力の半導体集積回路

ダイナミックランダムアクセスメモリが、同じ論理制御信号を生成する論理的に同じ回路を有する。各組の制御信号は、異なる電気パラメータを有することができる。1つの回路は、高速性能に対して最適化され、もう1つの回路は、低消費電力に対して最適化されうる。論理的に同じ回路は、ワード線アドレスプリデコーダ回路を含むことができ、高速プリデコーダ回路が、通常動作モード中にイネーブルにされ、より遅い低出力プリデコーダ回路が、セルフリフレッシュ動作のためにイネーブルにされる。セルフリフレッシュ動作中、高速回路は、その漏れ電流を最小限に抑えるために、電源から減結合されうる。  (もっと読む)

(もっと読む)

1 - 7 / 7

[ Back to top ]