Fターム[5M024AA27]の内容

Fターム[5M024AA27]に分類される特許

1 - 20 / 73

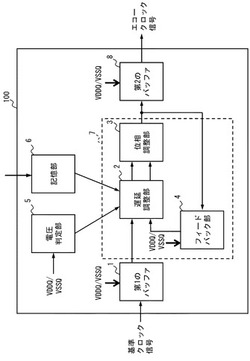

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】半導体装置に含まれるスプリッター回路10は、入力信号INTを受けて反転信号IB1を出力するインバータINV1と、反転信号IB1を受けて非反転信号IT1(第1の出力信号)を出力するインバータINV2が縦続接続される信号パスPASS1を含む。また、スプリッター回路10は、入力信号INTを受けて反転信号IB3(第2の出力信号)を出力するインバータINV3を含む信号パスPASS2を含む。また、インバータINV3と補助インバータINVCは出力信号線を共有する。インバータINV3と補助インバータINVCは、共に、入力信号INTの反転信号を電源とする。

(もっと読む)

半導体装置及びその制御方法

【課題】出力バッファ回路のインピーダンスを切り替えるためのタイミングマージンを拡大する。

【解決手段】制御期間T1においてはプルアップバッファ回路100をオン、プルダウンバッファ回路200をオフとし、制御期間T2においてはリードデータDQに基づいてプルアップバッファ回路100及びプルダウンバッファ回路200の一方をオン、他方をオフとする。制御期間T1においてはプルアップバッファ回路100のインピーダンスをインピーダンスコードODTCに基づいて設定し、制御期間T2においてはプルアップバッファ回路100及びプルダウンバッファ回路200の前記一方のインピーダンスをインピーダンスコードRONCに基づいて設定する。制御期間T3中にプルアップバッファ回路100のインピーダンスをコードODTCに基づく値からコードRONCに基づく値に変化させる。

(もっと読む)

半導体装置およびそれを利用した情報処理システム

【課題】半導体装置において、温度変化によるデータのラッチタイミングの調整によって生ずるシステムのビジー期間を抑制しなければならない。

【解決手段】タイミング制御回路116は、任意の温度でデータDQiとストローブ信号がキャリブレーションによってマッチングされたストローブ信号DQS,DQSBを受信し、内部ストローブ信号IDQS、IDQSBを生成し、ラッチ回路118に出力する。ラッチ回路118は、内部ストローブ信号IDQS、IDQSBのエッジのタイミングでデータDQiをラッチする。タイミング制御回路116は、温度検知回路124と内部ストローブ信号IDQS、IDQSBの伝送経路に間挿され、温度検知回路124からの温度信号Tにしたがって、前記マッチングを維持するように内部ストローブ信号IDQS、IDQSBの時間変動を抑制する可変遅延回路122を含む。

(もっと読む)

半導体装置

【課題】DLL回路がロックしないという現象の発生を防止する。

【解決手段】カウンタ回路202と、カウンタ回路202のカウント値CNTに応じた遅延量を内部クロック信号LCLKに与えるディレイライン201とを有する。まず、カウンタ回路202は第1のカウント値にセットされ、判定信号PDに基づいてそのカウント値CNTが周期的に更新される。その結果、内部クロック信号LCLKの位相が所望の位相に到達しなかった場合、カウンタ回路202は、第1のカウント値とは異なる第2のカウント値にセットされ、DLL回路200がリスタートされる。これにより、DLL回路がロックしなかった場合であっても自動的にリスタートされることから、DLL回路がロックしないという現象が防止される。

(もっと読む)

コマンド/アドレス・カリブレーションを採用するメモリ装置

【課題】コマンド/アドレス・カリブレーション方法、それを採用するメモリ装置及びメモリシステムを提供する。

【解決手段】該メモリ・コントローラは、クロック信号と、第1コマンド/アドレス信号とを伝送し、該メモリ装置は、クロック信号と共にモードレジスタ信号を受信し、内部クロック信号に応答し、コマンド/アドレスバスを介して受信される第1コマンド/アドレス信号によって、第2コマンド/アドレス信号を発し、メモリ・コントローラで、第1コマンド/アドレス信号と第2コマンド/アドレス信号とを比較し、パス/フェイル信号を発し、パス信号の中間を、コマンド/アドレス信号のウインドウ中間と判断し、クロック信号の立ち上がりエッジ/立ち下がりエッジに、コマンド/アドレス信号のウインドウ中間が位置するように、コマンド/アドレス信号を発してメモリ装置に提供する。

(もっと読む)

メモリインタフェース回路

【課題】データストローブ信号に発生するグリッジを有効に除去し、正確なデータ転送を可能にするメモリインタフェース回路を提供する。

【解決手段】システムクロック信号CLKに同期したマスク制御信号RENをある遅延調整値αだけ遅延させた信号を用いてデータラッチに使用するようにデータストローブ信号DQSをマスクする第1のマスク回路103と、遅延調整値αに一定の余裕度tを持たせてマスク制御信号RENを遅延させた信号を用いてデータストローブ信号DQSをマスクする第2のマスク回路104と、第1のマスク回路103の出力におけるエッジ回数のカウント値と第2のマスク回路104の出力におけるエッジ回数のカウント値とを比較して、両カウント値の一致を確認しつつ遅延調整値αを変更し、不一致が起こった場合には遅延調整値αを戻すように動作する比較回路1112とを設ける。

(もっと読む)

半導体装置

【課題】複数のメモリチップが積層された半導体装置においてリードライトバスの本数及び配線長を削減する。

【解決手段】積層された複数のメモリチップCC0〜CC7を備え、各メモリチップは複数のメモリバンクBank0〜Bank7と、各メモリバンクにそれぞれ割り当てられた複数のリードライトバスRWBS0〜RWBS7と、リードライトバスにそれぞれ割り当てられ当該メモリチップを貫通して設けられた複数の貫通電極TSV1とを備える。積層方向から見て互いに同じ位置に設けられた貫通電極TSV1はチップ間において共通接続される。メモリチップのそれぞれは、アクセスが要求されたことに応答して積層方向から見て互いに異なる位置に設けられたメモリバンクを同時に活性化し、これにより、平面位置の異なる貫通電極TSV1を介してデータの入出力を同時に行う。

(もっと読む)

半導体装置

【課題】センスアンプのセンスマージンを拡大する。

【解決手段】2つの素子分離領域3に隣接して各ウェル1,2にドライバトランジスタ4a,5a,4b,5bをそれぞれ配置し、各ウェル1,2にドライバトランジスタ4a,5a,4b,5bよりも素子分離領域3a,3bから離れた位置にクロスカップルされた2つの一対のセンストランジスタ6a乃至9a、6b乃至9bをそれぞれ配置する。これにより、センストランジスタ6a乃至9a、6b乃至9bと夫々対応する素子分離領域3a,3bと間に一定以上の距離が確保されることから、素子分離領域3a,3bからの距離によってトランジスタのしきい値が変化する現象の影響が低減され、その結果、夫々クロスカップルされた一対のトランジスタの特性を正確に一致させることが可能となる。

(もっと読む)

受信回路、システム装置及び半導体記憶装置

【課題】タイミングエラーの発生を抑制することのできる受信回路を提供する。

【解決手段】受信回路40は、データ列DQの先頭のデータをラッチするためのセットアップタイム及びホールドタイムを満たすタイミングでデータストローブ信号DQSの先頭の立ち上がりエッジが発生するように、データストローブ信号DQSに第1の遅延量を与える第1遅延回路42を含む。受信回路40は、データ列DQの3番目のデータをラッチするためのセットアップタイム及びホールドタイムを満たすタイミングでデータストローブ信号DQSの2番目の立ち上がりエッジが発生するように、データストローブ信号DQSに第2の遅延量を与える第2遅延回路43を含む。受信回路40は、第1遅延信号DQS1の先頭立ち上がりエッジでラッチした先頭データと、第2遅延信号DQS2の2番目の立ち上がりエッジでラッチした3番目のデータを選択する選択回路S1を含む。

(もっと読む)

タイミング回路および出力タイミング信号を発生する方法

【課題】入力タイミング信号に依存して出力タイミング信号を発生するように、タイミング回路および対応する方法を提供する。

【解決手段】タイミング回路は、入力タイミング信号を受信し、その入力に依存して出力を発生するように構成される。各回路構成要素は、その入力レベルの遷移に応答してその出力レベルを切り替え、その出力レベルを切り替える際に遅延を呈し、該遅延は、その出力レベルの第1のスイッチングと第1の遅延と、第2のスイッチングと第2の遅延とを含む。第1のスイッチングは、第2のスイッチングに対して逆方向であり、第1および第2の遅延は、そのスイッチング動作を繰り返し実施するにつれて、大きさの変化を呈する。この大きさの変化は、それぞれ、第1の遅延および第2の遅延について逆方向であり、出力信号のタイミングに対するそれぞれの影響を互いに打ち消し合うように、該第1の遅延および該第2の遅延の両方に依存する。

(もっと読む)

メモリシステム及びその制御方法

【課題】メモリデバイス間における遅延時間のばらつきを解消する。

【解決手段】データ端子20dがメモリコントローラ30に共通接続されたメモリデバイス21〜24を備える。メモリデバイス21〜24のそれぞれは、リードコマンドに応答してメモリセルアレイ100から読み出されたリードデータDataをデータ端子20dに出力するデータ出力回路120と、データ出力回路120によるリードデータDQの出力タイミングを調整する出力タイミング調整回路130とを備える。メモリコントローラ30は、メモリデバイス21〜24にそれぞれ設定コマンドを発行することにより、リードコマンドを発行してからリードデータDQを受信するまでの遅延時間がメモリデバイス21〜24間において一致するよう、出力タイミング調整回路130による調整量を設定する。

(もっと読む)

半導体システムのデータ送受信装置および方法

【課題】データの送受信中でも内部クロックをストロボ信号によりトラッキングしてすべてのデータをその有効ウィンドウの範囲内でサンプリングすることができ、よって、データ伝達の信頼性を高めることが可能な、高速で動作する半導体システムのデータ送受信装置および方法を提供すること。

【解決手段】本半導体メモリ装置はストロボ信号の入力を受けてトラッキングクロックを生成するストロボ信号受信部220と、クロックの入力を受けて内部クロックを生成するクロック受信部240と、内部クロックに応じて並列データの入力を受けて内部データを生成する複数のデータ受信部200_0と、データの送受信の間、内部クロックの位相が変動するのを補償するために、トラッキングクロックに応じて内部クロックをトラッキングして内部クロックの位相を調整する位相制御部260を備える。

(もっと読む)

半導体装置

【課題】データストローブ信号のスルーレートを変更することなくデータストローブ信号のクロスポイントの電位を調整可能な半導体装置を提供する。

【解決手段】半導体装置は、外部クロックに基づき第1内部クロックを発生する発生回路と、第1内部クロックに基づき第2及び第3内部クロックを生成する分割回路であり第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを調整するエッジ調整回路を含む分割回路と、エッジ調整回路にエッジ調整信号を供給する調整情報保持部と、第2内部クロックに応じて第1データストローブ信号を発生し第3内部クロックに応じて第1データストローブ信号と位相が異なる第2データストローブ信号を発生する出力回路を備え、エッジ調整回路はエッジ調整信号に応じて第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを可変に調整する。

(もっと読む)

メモリ制御装置及びマスクタイミング制御方法

【課題】リードデータの受信を確実に行うことができるメモリ制御装置とマスクタイミング制御方法を提供する。

【解決手段】ストローブ信号に同期してデータを受信する同期式のメモリ制御装置において、ストローブ信号をマスク信号を用いてマスクする回路と、ストローブ信号を複数の遅延単位で遅延させそのストローブ信号のデータをラッチするタイミング測定回路と、マスク信号を発生するマスク生成回路とを備え、タイミング測定回路は、ストローブ信号がマスクされた信号の最初の立ち上がりエッジで各遅延されたストローブ信号のデータをラッチし、マスク生成回路は、メモリ回路のコマンド制御回路からの信号に応じてマスク信号の生成を制御し、マスク生成回路は複数の遅延単位で構成した遅延回路を含み、内部クロックに同期してマスク信号の開始タイミングを調整し、遅延回路により選択した遅延単位の遅延量を経た信号をマスク信号として出力する。

(もっと読む)

メモリインタフェース回路、半導体装置、メモリインタフェース方法

【課題】定期的なスキュー調整を不要とし、任意の時期にスキュー調整を要求する信号を出力する。

【解決手段】メモリインタフェース回路は、遅延回路と、検査回路と、判定回路とを具備する。遅延回路は、メモリ回路から入力する信号に遅延を与えて出力する。検査回路は、遅延回路の遅延量を調整して設定し、遅延回路の遅延量を調整値算出回路によって設定された値から所定の量増減し検査する。判定回路は、信号に基づいて取り出すデータに関するリードエラーの発生を検知して制御回路にスキューの再調整を要求する。

(もっと読む)

半導体装置、その装置を備える半導体システム、及びそのシステムの動作方法。

【課題】半導体装置コントローラと半導体装置との間でデータが入出力される時、データの位相が変動することと関係なく、半導体装置コントローラと半導体装置との間で常に安定的にデータが入出力できるシステム、そのシステムに用いる半導体装置、及びそのシステムの動作方法を提供すること。

【解決手段】半導体装置は、印加されるライトクロックとライトデータとを補正する回路及び方法に関するもので、データ入出力コマンドに応答してノーマルデータ(ソースクロックのセンターに同期する)を入出力するノーマルデータ入出力部11と、所定のコマンドに応答してデータ復旧情報信号(前記ソースクロックのエッジに同期する)の入力を受けて所定の時間の後に出力するデータ復旧情報信号入出力部100とを備える。

(もっと読む)

アドレス制御回路及び半導体メモリ装置

【課題】ライト動作でスキューの発生を最小化できるアドレス制御回路及び半導体メモリ装置を開示する。

【解決手段】リード動作実行のための第1のバースト区間で、アドレスからリードカラムアドレスを生成するリードカラムアドレス制御回路と、ライト動作実行のための第2のバースト区間で、前記アドレスからライトカラムアドレスを生成するライトカラムアドレス制御回路と、を含むアドレス制御回路を提供する。

(もっと読む)

半導体装置

【課題】出力端子から出力する信号のスルーレートが他の出力端子から出力するデータに依存して変動しないように自動調整する機能を有する半導体装置を提供する。

【解決手段】複数の出力端子と、複数の出力端子にそれぞれ対応して設けられ対応する出力端子に接続された複数の出力回路と、を備え、複数の出力端子のうち特定の出力端子に接続された特定の出力回路は、複数の出力回路のうち、特定の出力回路以外の出力回路の状態遷移に基づいてスルーレートを自動的に調整する。

(もっと読む)

半導体装置

【課題】予備の貫通電極を用いて貫通電極の不良を救済する場合に、置換の前後における信号パスの長さの差を短縮する。

【解決手段】ドライバ回路101〜108を有する半導体チップIFと、レシーバ回路201〜208を有する半導体チップCCと、半導体チップCCに設けられた貫通電極301〜309とを備える。半導体チップIFは、i番(iは1〜nの整数)のドライバ回路の出力端をi番からi+m番の貫通電極のいずれかに排他的に接続する出力切り替え回路120を有し、半導体チップCCは、i番(iは1〜nの整数)のレシーバ回路の入力端をi番からi+m番の貫通電極のいずれかに排他的に接続する入力切り替え回路220を有する。これにより、置換前の信号パスと置換後の信号パスとの間にほとんど配線長差が生じないことから、信号品質が高められる。

(もっと読む)

1 - 20 / 73

[ Back to top ]