Fターム[5M024AA56]の内容

Fターム[5M024AA56]に分類される特許

1 - 20 / 35

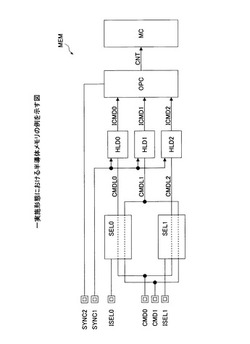

半導体メモリ、半導体メモリの動作方法、システムおよび半導体メモリの製造方法

【課題】少ない数のコマンド端子を用いて、半導体メモリを効率よくアクセスする。

【解決手段】半導体メモリMEMは、選択信号に応じて選択される1つが動作し、複数の第1コマンド端子CMD0、CMD1にそれぞれ供給される複数の第1コマンド信号を受け、受けた第1コマンド信号を出力する複数の第1選択部SEL0、SEL1と、第1選択部の出力に接続され、第1コマンド端子の数より多く、少なくとも1つが第1選択部の複数に共通に接続され、第1選択部の1つから出力される第1コマンド信号を、第1同期信号SYNC1に応答して保持し、第2コマンド信号として出力する複数の保持部HLD0、HLD1、HLD2と、第2コマンド信号に応じた動作制御信号CNTを、第1同期信号に比べて発生頻度が低い第2同期信号SYNC2に応答して出力する動作制御部OPCと、動作制御信号に応じてアクセスされるメモリセルMCとを有している。

(もっと読む)

半導体装置および集積型半導体装置

【課題】積層型半導体装置における全ての半導体チップのテストを行うにあたり、テスト装置側でチップ選択端子に対して割り当てるべき端子数を削減する。

【解決手段】集積型半導体装置100のチップ200において、制御信号出力部210は、制御信号入力端子302Aからの外部制御信号TRGIの入力に応じて、チップ識別子保持部250に対してチップ識別子の保持を指示する。チップ識別子保持部250は指示に応じて、アドレス入力端子303Aから入力されるチップ識別子の値を保持する。また、チップ識別子の保持タイミングを指示した後の所定タイミングで次段チップ制御信号TRGOを出力する。次段チップ制御信号TRGOは、次段のチップ200が制御信号入力端子302Aから外部制御信号TRGIとして入力する。

(もっと読む)

メモリシステム及び半導体記憶装置

【課題】データ入力端子とデータ出力端子を分離し、スループットを向上させるとともに、端子数の増加を抑制できる半導体記憶装置及びメモリシステムを提供する。

【解決手段】少なくとも一つのライトデータ入力端子と、ライトデータ入力端子のN倍の数のリードデータ出力端子と、データ記憶部と、第1の周波数の信号に同期してデータ記憶部から読み出したリードデータをリードデータ出力端子から出力するデータ出力回路と、ライトデータ入力端子から入力したライトデータを第1の周波数のN倍の周波数のライトストローブ信号に同期して取り込み、前記データ記憶部へ送るデータ入力回路と、を備える。

(もっと読む)

半導体装置、それに結合されたコントローラ、それを含むシステム及び動作方法

【課題】半導体装置、これに結合されたコントローラ、これを含むシステム及び動作方法を提供する。

【解決手段】メモリにライト動作を行うために選択的にデータを処理し、ライト動作中にモードレジスタコマンドに応答して、プロセシング機能のグループのうち、1つのプロセシング機能をイネーブルするデータ制御部を備え、プロセシング機能のグループは、少なくとも3つのプロセシング機能を含む半導体装置である。

(もっと読む)

半導体装置及びこれを備える半導体パッケージ

【課題】パッケージ基板上におけるカップリングノイズを低減可能な半導体装置を提供する。

【解決手段】第1のデータ入出力パッド、第1の電源パッド、第2のデータ入出力パッド及び第2の電源パッドがこの順にX方向に配列されたパッド群Pを複数備える。第1及び第2のデータ入出力パッドはそれぞれ第1及び第2のデータ入出力バッファに接続され、第1の電源パッドは第1及び第2のデータ入出力バッファに第1の電源電位を供給し、第2の電源パッドは第1及び第2のデータ入出力バッファに第2の電源電位を供給する。各パッド群Pに含まれる第1のデータ入出力パッドは、他のパッド群に含まれる第2の電源パッド又はいずれのパッド群にも含まれない複数の電源パッドのいずれかと隣接している。これにより、パッケージ基板上におけるカップリングノイズを防止しつつ、パッド総数の増加を抑制することが可能となる。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】端子数を増加させることなく、同一アドレスに対して連続して実行される連続読み出し及び連続書き込みの動作を高速化する。

【解決手段】この半導体記憶装置は、所定のアドレスによって指定されるメモリセルから所定の長さ分のデータの連続読み出し及び連続書き込みが実行される半導体記憶装置であって、複数のメモリセルと、アドレスが入力されるアドレス入力端子と、所定の長さ分の読み出しデータを出力するデータ出力端子と、所定の長さ分の書き込みデータが入力されるデータ入力端子と、を備えている。アドレス入力端子の一部は、データ出力端子と共有されている。

(もっと読む)

半導体記憶装置、及び該半導体記憶装置のテスト方法

【課題】半導体記憶装置の実動作速度でテストを行い、且つ接続に要するテスターの入出力端子数を削減できる半導体記憶装置を提供する。

【解決手段】テストデータをメモリ部12へ記憶させる際、データ入出力端子17の一部の端子から入力されるデータをメモリ部12に出力して記憶させ、メモリ部12の動作テストを行う際、メモリ部12から読み出したデータを一度ラッチして、再びメモリ部12に入力し記憶させ、テストデータをメモリ部12から読み出す際、データ入出力端子17の一部の端子からテストデータを順次出力するループバック回路14を備える。

(もっと読む)

半導体素子

【課題】高速で動作する半導体素子において、データ伝達の信頼性を高め、動作モードに応じて誤り検出符号EDCを出力するパッドを介して巡回冗長検査CRC用データだけでなく、読み出し命令に対応して出力されるデータのためのデータストローブ信号を出力することにより、入出力の過程で歪み得るデータの信頼性を高めることができるようにする半導体素子を提供すること。

【解決手段】誤り検出のための巡回冗長検査用データを出力するパッドを備えており、該パッドを介し動作モードに応じて前記巡回冗長検査用データを出力するか、又は読み出し命令に対応して出力されるデータとともに出力されるデータストローブ信号を出力することを特徴とする。

(もっと読む)

半導体記憶装置

【課題】データマスク信号用の外部入力端子を増加させずに、データ信号のバースト読み出し又はバースト書き込みにおけるそれぞれのデータ信号ごとにマスクするか否かを選択し、それぞれのデータ信号のビットごとに異なるマスクをすることを可能とする。

【解決手段】アドレス信号用の外部入力端子17を介して入力されるマスク指示信号に基づき、マスクレジスタ回路11に記憶されるマスクパターン信号を用い、リードデータコンバータ回路16a及びライトデータコンバータ回路16cは、バースト読み出し又はバースト書き込みのそれぞれのデータ信号ごとにマスクするか否かを選択し、データ信号を変換する。変換されたデータ信号は、書き込み時はメモリセル500へ出力し記憶され、読み出し時はデータ信号用の外部入出力端子17へ出力される。

(もっと読む)

半導体記憶装置

【課題】製造コストを抑制しつつランダムアクセス性を向上させて高速に動作させる。

【解決手段】半導体記憶装置は、データを書き込む場合は、書込みコマンドが入力されたときのクロックと同じタイミングのときのデータを、活性化されたメモリバンクに書き込むようにデータ入力バッファ110を制御し、データを読み出す場合は、読出しコマンドが入力されたときのクロックに対して3以上の所定のリードレーテンシーで、活性化されたメモリバンクからデータを読み出してデータを出力するようにデータ出力バッファ120を制御するバッファ制御回路130を備えている。

(もっと読む)

メモリチップにアクセスする方法

【課題】メモリモジュールの電気配線密度を減らし、メモリチップの試験費用節減のために、メモリの入力ピン数を減少できるアクセス方法を提供する。

【解決手段】メモリチップにアクセスする方法は、メモリチップに複数の第一入力ピンと複数の第二入力ピンを設ける段階と、複数の行アドレス信号をそれぞれ前記第一入力ピンに入力する段階と、複数の列アドレス信号をそれぞれ前記第二入力ピンに入力する段階とを含む。前記各行アドレス信号の行アドレスコマンドパッケージ長はクロック信号の複数のクロック周期に対応する。前記各列アドレス信号の列アドレスコマンドパッケージ長はクロック信号の複数のクロック周期に対応する。

(もっと読む)

半導体記憶装置と品種展開方法

【課題】同一チップで一度にアクセスされるデータ転送量を変えてもトータルのピークバンド幅を一定に保つ半導体記憶装置の提供。

【解決手段】複数のバンクと、複数のデータ入出力端子と、制御信号端子と、アドレス信号端子と、バンクをまとめて一つの独立したチップとして動作可能な少なくとも1つ又は複数のバーチャルチップを備え、複数のデータ入出力端子のそれぞれは1又は複数のバーチャルチップのいずれか一つに属すると共に、複数の制御信号端子と複数のアドレス信号端子は、1又は複数のバーチャルチップのそれぞれで共有される。

(もっと読む)

半導体記憶装置、およびアドレスラッチの高速化方法

【課題】DDRの高速化方式において、従来別々とされていたアドレスピン及びコマンドピンを共通化し、Rise/Fall両エッジでコマンド及びアドレスデータを取り込む際に、従来のDDR方式において、1/2tCK分のアクセスペナルティの問題が生じることを解決する。

【解決手段】アドレス信号(ADD)を、FallエッジF1に同期してスルーラッチタイプのラッチ回路により取り込み保持するように構成する。これにより、アドレスラッチにおいて、FallエッジF1から決まるアクセス時間をセットアップ分(tS)だけ高速化することができ、1/2tCK分のペナルティを緩和することが可能になる。

(もっと読む)

半導体記憶装置

【課題】本発明は、A/DQ De−Mux動作とA/DQ Mux動作とが可能な擬似SRAMにおいて、入力回路のレイアウトを最適化できるようにする。

【解決手段】たとえば、複数のアドレスピン用の入力回路(A0’〜A23’)15を、その他の制御回路が配置されているチップ11の他端側(下側)に、それぞれ、複数のDQピン用の入力回路(DQ0’〜DQ23’)16に隣接させて配置する。また、複数のアドレスピン用の入力回路15と、チップ11の一端側(上側)に配置された複数のアドレスパッド13との間を、メタル配線LA0〜LA23を介して相互に接続してなる構成とされている。

(もっと読む)

半導体記憶装置

【課題】モード切り替えを行うための専用ピンを不要にでき、ピン数を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルMCを備えたメモリセルアレイ10と、モード制御信号BSTを生成するバースト回路31と、前記モード制御信号が送信される信号線34を前記バースト回路と共有するリフレッシュコマンド検出回路33とを備える制御回路19とを具備し、前記リフレッシュコマンド検出回路33は、前記モード制御信号が第1レベルの際に、前記メモリセルアレイにリフレッシュ動作を行う。

(もっと読む)

半導体メモリ

【課題】プローブ検査の要求位置精度を高めることなく、半導体メモリのデータ入出力PADを狭ピッチにする。

【解決手段】複数のメモリセルからなるメモリセルアレイ101と、狭ピッチの信号端子DQ1〜DQnと、ピッチの大きいテスト用信号端子TEST1〜4と、メモリセルに書き込むデータを信号端子から入力されたデータとテスト用信号端子から入力されたデータのいずれかから選択するものであって、各信号端子の配列に基づいてデータを重複させて割り当てるデータラッチ回路405とを備えている。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】アドレス信号のラッチマージンを確実に調整可能な半導体記憶装置を提供する。

【解決手段】コマンド信号CMDをラッチするコマンドラッチ回路130と、アドレス信号ADDをラッチするアドレスラッチ回路140と、モード信号MODをラッチするモードラッチ回路150と、コマンドラッチ回路130に通常コマンドがラッチされたことに応答してアドレスラッチ回路140を選択し、調整コマンドがラッチされたことに応答してモードラッチ回路150を選択するコマンドデコーダ170とを備える。これにより、モードレジスタセットを実行することなく、モード信号の受け付けをダイナミックに行うことができる。このため、モードラッチ回路のラッチマージンを十分に広く確保しておけば、モード信号の入力が不可能となるおそれが無くなる。

(もっと読む)

半導体記憶装置

【課題】アドレス入力とデータ入出力に同一のパッドを用い、高速動作が可能な半導体記憶装置を提供する。

【解決手段】アドレス入力とデータ入出力に同一のパッドを用い、そのパッドに接続された入力回路及びデータ出力回路を有する半導体記憶装置にて、チップイネーブル信号、出力イネーブル信号及びアドレス取り込み信号に応じて、スタンバイ時と出力ディセーブル時とアドレス取り込み期間には、データ出力回路の出力をハイインピーダンス状態にすることで、アドレス取り込み期間が終了する前であっても内部でのリード動作を開始できるようにし高速動作を可能にする。

(もっと読む)

半導体記憶装置

【課題】パリティデータを格納した場合においてもデータ圧縮を行いつつテストを実行することを可能にした半導体記憶装置を提供する。

【解決手段】メモリセルアレイ1は、複数のワード線WLと複数のビット線BLの交点に形成された複数のメモリセルMCを有する。メモリセルアレイは複数のセグメントSGに分割され、各セグメントSGからは4本のメインデータ線MDLが延びている。また、パリティデータ記憶用のセグメントSGPからは、パリティ用メインデータ線MDLPが延びている。第1判定回路10Aは、メインデータ線MDLから読み出されたデータとその期待値とを比較してその一致・不一致を判定する。第2判定回路10Bは、複数のパリティ用メインデータ線MDLPから読み出されるデータとその期待値とを比較してその一致・不一致を判定する。第2判定回路10Bは、その判定結果を選択的に出力する選択回路105を備えている。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で充分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

1 - 20 / 35

[ Back to top ]