Fターム[5M024BB28]の内容

DRAM (26,723) | 改良の場所/タイミング (5,148) | 場所 (3,103) | モード設定回路 (96)

Fターム[5M024BB28]に分類される特許

1 - 20 / 96

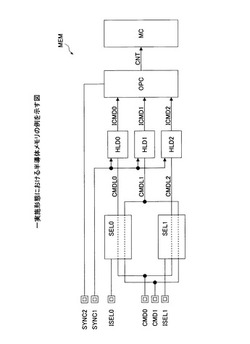

半導体メモリ、半導体メモリの動作方法、システムおよび半導体メモリの製造方法

【課題】少ない数のコマンド端子を用いて、半導体メモリを効率よくアクセスする。

【解決手段】半導体メモリMEMは、選択信号に応じて選択される1つが動作し、複数の第1コマンド端子CMD0、CMD1にそれぞれ供給される複数の第1コマンド信号を受け、受けた第1コマンド信号を出力する複数の第1選択部SEL0、SEL1と、第1選択部の出力に接続され、第1コマンド端子の数より多く、少なくとも1つが第1選択部の複数に共通に接続され、第1選択部の1つから出力される第1コマンド信号を、第1同期信号SYNC1に応答して保持し、第2コマンド信号として出力する複数の保持部HLD0、HLD1、HLD2と、第2コマンド信号に応じた動作制御信号CNTを、第1同期信号に比べて発生頻度が低い第2同期信号SYNC2に応答して出力する動作制御部OPCと、動作制御信号に応じてアクセスされるメモリセルMCとを有している。

(もっと読む)

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

半導体装置

【課題】1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込む。

【解決手段】例えば、モードレジスタ設定信号MRS1を活性化させるコマンドデコーダ82と、モードレジスタ設定信号MRS1を遅延させることによってモードレジスタ設定信号MRS2を生成するレイテンシシフタ83と、データ信号D0がローレベルである場合にはモードレジスタ設定信号MRS2に基づいてモードレジスタ設定信号MRS3を活性化させ、データ信号D0がハイレベルである場合にはモードレジスタ設定信号MRS3を非活性状態に保持する論理ゲート回路G2,G3と、モードレジスタ設定信号MRS3の活性化に応答してモード信号が設定されるモードレジスタ84を備える。これにより、1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込める。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1を介して設定可能な第1及び第2のモード情報を記憶するモード情報記憶部108−1と、クロック信号CK1が供給され第1のモード情報に基づいて動作するメモリコア106−1と、クロック信号CK2が供給されるメモリコア106−2と、メモリコア106−1をバスインターフェイス回路105−1に結合させ、メモリコア106−2を所定の切替情報に基づいてバスインターフェイス回路105−1,105−2のいずれかに選択的に結合させる選択回路107−1と、を備える。そして、メモリコア106−2は、バスインターフェイス回路105−2に結合された場合に第2のモード情報に基づいて動作する。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、セルフリフレッシュモードにエントリすると、オシレータ150を用いてリフレッシュ動作を周期的に実行する。セルフリフレッシュモードにおいて1回のリフレッシュ動作に要する時間をオートリフレッシュの1/4に短縮するとともに、リフレッシュ動作の実行頻度を4倍とする。これにより、セルフリフレッシュイグジットコマンドSRXを発行した後、ロウ系のコマンドの投入が禁止される期間を短縮することが可能となる。

(もっと読む)

半導体装置及びその制御方法並びに情報処理システム

【課題】ギアダウンモードのオン/オフによるラッチタイミング差をなくす。

【解決手段】クロック信号CLK1を分周することによってクロック信号CLK2を生成する分周回路2と、チップ選択信号CS1とクロック信号CLK2を論理合成することによりチップ選択信号CS2を生成する論理回路4と、チップ選択信号CS2に基づいて活性化されコマンド信号CMD1に基づいてコマンド信号CMD2を生成するコマンド生成回路6とを備える。本発明によれば、分周されたクロック信号に同期してコマンド信号のラッチを行うのではなく、分周されたクロック信号に同期してコマンド生成回路を活性化させていることから、分周されていないクロック信号に同期してコマンド信号のラッチ動作を行うことができる。これにより、ギアダウンモードのオン/オフによるラッチタイミングに差が生じなくなる。

(もっと読む)

モードレジスタセットを備える半導体メモリ装置

【課題】アドレスピンを追加せずに複数のMRSコマンドを生成することができるモードレジスタセットを備えた半導体メモリ装置を提供する。

【解決手段】データバッファ制御信号DQBUF_ENDBを生成する制御部230と、データバッファ制御信号DQBUF_ENDBに応じて、データパッドDQを介して入力される複数のMRSコードA<0:12>,BA<0:2>をバッファリングして出力するデータバッファ部250と、データバッファ部250から出力される複数のMRSコードA,BAをデータラインGIO,LIOを介して受信し、受信した複数のMRSコードA,BAを用いて複数のMRSコマンドNMRS_CMD<0:12>、EMRS_CMD<0:12>、EMRS2_CMD<0:12>、EMRS3_CMD<0:12>、TMRS_CMD<0:12>を生成する複数のMRSコマンド生成部290A〜290Eとを備える。

(もっと読む)

半導体メモリ

【課題】半導体メモリをアクセスするときに、消費電流が一時的に増加するピーク電流を低減する手段を提供する。

【解決手段】半導体メモリ10は、メモリセルアレイ11とデータマスク制御部101とを備える。データマスク制御部101は、メモリセルアレイ11とデータ入出力接点とのデータ授受を制御する内部マスク信号を出力する。データマスク制御部101は、外部から入力または内部で生成されるデフォルトマスク信号に応じて内部マスク信号の待機状態の論理値を可変とする。

(もっと読む)

半導体装置およびその動作方法

【課題】マックスパワーダウンモード(max power down mode)をサポートする半導体装置に関し、マックスパワーダウンモードの進入動作後に1つのバッファリング部のみを使用したとしても、マックスパワーダウンモードの脱出動作を可能にする半導体装置を提供する。

【解決手段】外部から入力される第1モード信号CSBをバッファリングする第1バッファリング部221と、第1バッファリング部221の出力信号ICSBに応答して活性化され、外部から入力される第2モード信号CKEをバッファリングする第2バッファリング部222とを備える。

(もっと読む)

DRAMの電力および性能を動的にスケーリングするための方法および回路

【課題】 電力および性能の動的スケーリングをサポートするメモリを提供すること。

【解決手段】 メモリシステムは、高性能モードおよび低電力モードをサポートする。このメモリシステムは、メモリコアおよびコアインターフェイスを含む。メモリコアは、どちらのモードでも同じままであるコア供給電圧を使用する。節電するために、コアインターフェイスの供給電圧および信号速度をスケールダウンすることができる。コアインターフェイスが異なるモードにおいて使用する信号電圧に対応するために、メモリコアとコアインターフェイスとの間のレベルシフタが信号を必要に応じてレベルシフトする。

(もっと読む)

メモリインタフェース回路、半導体装置、メモリインタフェース方法

【課題】定期的なスキュー調整を不要とし、任意の時期にスキュー調整を要求する信号を出力する。

【解決手段】メモリインタフェース回路は、遅延回路と、検査回路と、判定回路とを具備する。遅延回路は、メモリ回路から入力する信号に遅延を与えて出力する。検査回路は、遅延回路の遅延量を調整して設定し、遅延回路の遅延量を調整値算出回路によって設定された値から所定の量増減し検査する。判定回路は、信号に基づいて取り出すデータに関するリードエラーの発生を検知して制御回路にスキューの再調整を要求する。

(もっと読む)

クロック入力バッファの制御

集積回路は、バッファ(24)に結合されたクロック入力ピンを有してもよい。バッファは、メモリ等の集積回路チップにクロック信号(28)を供給してもよい。電力を節約するために、バッファはパワー・ダウンされる。使用する準備ができたとき、バッファは急速にパワー・アップ状態に戻る。一実施形態では、クロック信号の所定数のトグルに応答して、バッファは自動的にパワー・アップされる。 (もっと読む)

半導体装置、それに結合されたコントローラ、それを含むシステム及び動作方法

【課題】半導体装置、これに結合されたコントローラ、これを含むシステム及び動作方法を提供する。

【解決手段】メモリにライト動作を行うために選択的にデータを処理し、ライト動作中にモードレジスタコマンドに応答して、プロセシング機能のグループのうち、1つのプロセシング機能をイネーブルするデータ制御部を備え、プロセシング機能のグループは、少なくとも3つのプロセシング機能を含む半導体装置である。

(もっと読む)

半導体メモリ

【課題】 半導体メモリのデータ端子を任意に選択可能にし、1つの半導体メモリを様々な端子仕様のコントローラに接続する。

【解決手段】 半導体メモリは、複数のデータ端子と、データ端子にそれぞれ対応して設けられ、対応するデータ端子に供給されるデータを保持するメモリセルを含み、第1許可禁止信号にそれぞれ応じて動作が許可または禁止される複数の内部回路と、設定期間にデータ端子にそれぞれ供給される論理を許可レベルまたは禁止レベルとしてそれぞれ保持し、第1許可禁止信号として出力するレジスタとを有している。

(もっと読む)

半導体装置、センスアンプ回路、半導体装置の制御方法及びセンスアンプ回路の制御方法

【課題】ダブルゲートトランジスタを用いた機能回路のバックゲート電圧を適切に制御して良好な特性を実現可能な半導体装置等及びその制御方法を提供する。

【解決手段】本発明の半導体装置は、ダブルゲートトランジスタを含む機能回路と、ダブルゲート構造の基準トランジスタ20、30を含む電圧制御回路を備えている。基準トランジスタ20、30には、第1ゲート電極に参照電圧Vrp、Vrnが印加され、第2ゲート電極の電位はドレイン電流Ip、Inが参照電流Irp、Irnと一致するように制御され、その電位が制御電圧VBGP、VBGNとして出力される。制御電圧VBGP、VBGNを機能回路のダブルゲートトランジスタの第2ゲート電極に印加することで機能回路に所望の特性が付与される。

(もっと読む)

半導体メモリおよび半導体メモリの動作方法

【課題】 制御信号生成回路がフリーズしたときに、アクセスサイクル時間を増加することなく制御信号生成回路をリセットする。

【解決手段】 基幹信号生成回路は、アクセスコマンドに応答して基幹信号を活性化し、リセット信号またはハングアップ信号に応答して基幹信号を非活性化する。制御信号生成回路は、基幹信号に応答してメモリコアをアクセスするための制御信号を順次に生成し、制御信号の少なくともいずれかに応答してリセット信号を生成する。ハングアップ信号生成回路は、次のアクセスコマンドに応答してハングアップ信号を生成する。ハングアップ信号を半導体メモリの内部で生成される信号ではなく、半導体メモリの外部から供給されるアクセスコマンドに応答して生成することで、制御信号生成回路がフリーズしたときに、アクセスサイクル時間を増加することなく制御信号生成回路をリセットできる。

(もっと読む)

半導体記憶装置

【課題】リテンション時間を高めて消費電力を削減するとともに、回路面積の増大も抑制する。

【解決手段】ワード線とビット線の交点に配列されたメモリセルから読み出された信号をセンスアンプ回路にて検知増幅する。書き込み回路は、複数のメモリセルのうちの第1のメモリセルに保持された第1データを読み出して第1のメモリセルとは別の第2のメモリセルに第1データに対応する第2データを書き込む。データラッチ回路は、第1のメモリセルから読み出されたデータを保持する。論理演算回路は、第2のメモリセルから読み出されたデータとデータラッチ回路に保持されたデータとを入力値とした論理演算を実行して第3データを演算値として出力する。書き戻し回路は、第3データを第1のメモリセルに対し書き戻す。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム並びにコントローラ

【課題】特に多ビット品においてしばしば生じる実効的なデータ転送レートの低下を防止する。

【解決手段】メモリ回路部110A,110Bに対してそれぞれ割り当てられたデータ入出力端子LDQ,UDQと、メモリ回路部110A,110Bに対して共通に割り当てられたアドレス端子131と、を備える。メモリ回路部110Aは、チップ選択信号CS1Bが活性化されると、メモリ回路部110Bの動作とは無関係にアドレス信号ADDに基づいてデータ入出力端子LDQを介したリード動作又はライト動作を行う。メモリ回路部110Bは、チップ選択信号CS2Bが活性化されると、メモリ回路部110Aの動作とは無関係にアドレス信号ADDに基づいてデータ入出力端子UDQを介したリード動作又はライト動作を行う。これにより、無駄なデータ転送が防止され、実効的なデータ転送レートが高められる。

(もっと読む)

半導体記憶装置及びこれを制御するメモリコントローラ、並びに、情報処理システム

【課題】パワーダウン時において、DLL回路の動作を継続させるファストイグジットモードと、DLL回路の動作を停止させるスローイグジットモードをオンザフライで選択する。

【解決手段】パワーダウンコマンドに応答して所定の内部回路の動作を停止させるパワーダウンコントロール回路100と、パワーダウンコマンドの発行と同時に外部から選択信号A12が入力される外部端子14とを備える。パワーダウンコントロール回路100は、選択信号A12がローレベルである場合にはDLL回路23の動作を停止させ、選択信号A12がハイレベルである場合にはDLL回路23の動作を継続させる。本発明によれば、パワーダウンコマンドと同時に入力される選択信号A12によってオンザフライでモード選択が可能となる。

(もっと読む)

シンクロナスDRAMアクセス装置

【課題】 シンクロナスDRAMに対して、転送語数が複数であるデータや転送語数が1であるデータを切り替えて転送する場合に、効率的にデータ転送を行うための制御を簡単な回路で実現する。

【解決手段】 転送語数が2以上の場合、第1の制御器4を起動し、アクティブ、リード/ライト、プリチャージの順番にコマンドを出力する。転送語数が1の場合、第2の制御器5を起動し、アクティブ、リード/ライトの順にコマンドを出力し、次の転送要求を待つ。次の転送要求のデータ転送語数が1であれば、第2の制御器5はリード/ライトコマンドを出力し、再び転送要求を待つ。次の転送要求のデータ転送語数が2以上であればプリチャージコマンドを出力して第1の制御器4を起動し、バースト転送を行う。これにより、データ転送語数が1の場合の転送の際、不必要なアクティブコマンドやプリチャージコマンドを出力しないので、データ転送効率が改善された。

(もっと読む)

1 - 20 / 96

[ Back to top ]