Fターム[5M024DD32]の内容

Fターム[5M024DD32]に分類される特許

1 - 20 / 63

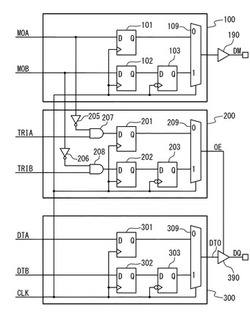

メモリ制御装置

【課題】メモリ書き込み時の消費電力を削減できるメモリ制御装置を提供する。

【解決手段】メモリ制御装置は、データバスを介してメモリ装置にデータをバースト転送するデータ出力バッファ回路390と、データのうちのメモリ装置内のメモリセルへの書き込みを禁止するデータを示すマスク信号をメモリ装置に出力するマスク信号出力バッファ回路190とを具備し、データ出力バッファ回路390は、マスク信号が書き込み禁止を示すときに出力ノードをハイインピーダンスにする。

(もっと読む)

メモリシステムの書き込みタイミングを較正する方法および装置

【課題】メモリの書き込み動作の実行に必要な信号のタイミングを較正する手法を提供する。

【解決手段】メモリ制御装置が、書き込み−読み出し−検証の動作を実行してデータストローブ信号とクロック信号との間のクロックサイクル関係を較正する(308)ように構成されており、クロック信号に対するデータストローブ信号の遅延をクロック周期単位で変化させることを含む。メモリチップの位相検出器は、クロック信号、マーキング信号、およびデータストローブ信号を含む複数の信号をメモリ制御装置から受信し、マーキング信号は、クロック信号の中の特定のクロックサイクルをマーキングするパルスを含み、マーキング信号を用いて、クロック信号の中の特定のクロックサイクルに窓を掛け、データストローブ信号を用いて窓掛けクロック信号を捕捉して、フィードバック信号を生成する。このフィードバック信号は、メモリ制御装置に返される。

(もっと読む)

半導体装置

【課題】ストローブ信号の変化によって基準電位に重畳するノイズを低減し、これにより、基準電位を用いる入力レシーバ回路の動作マージンの低下を防止する。

【解決手段】ストローブ信号IDQSTによって活性化され、入力信号DQの電位と基準電位VREFとを比較することによって出力信号IDQRを生成する入力レシーバ回路17Rと、ストローブ信号IDQSTの変化によって基準電位VREFに生じるノイズをキャンセルするノイズキャンセラ100Tとを備える。本発明によれば、ノイズキャンセラ100Tによって基準電位VREFに生じるノイズがキャンセルされることから、入力レシーバ回路17Rの動作マージンを十分に確保することができる。これにより、高速なデータ転送を行うことが可能となる。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】半導体装置に含まれるスプリッター回路10は、入力信号INTを受けて反転信号IB1を出力するインバータINV1と、反転信号IB1を受けて非反転信号IT1(第1の出力信号)を出力するインバータINV2が縦続接続される信号パスPASS1を含む。また、スプリッター回路10は、入力信号INTを受けて反転信号IB3(第2の出力信号)を出力するインバータINV3を含む信号パスPASS2を含む。また、インバータINV3と補助インバータINVCは出力信号線を共有する。インバータINV3と補助インバータINVCは、共に、入力信号INTの反転信号を電源とする。

(もっと読む)

DDR型半導体記憶装置

【課題】アドレス入力バッファによる電力消費を低減可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、アドレス端子に接続される第1入力バッファと、データ入力の基準となるクロック信号を受けるクロック端子と、前記クロック端子に接続されるクロック信号を受ける第2入力バッファとを具備する。前記第1入力バッファは、ライトコマンドが入力された場合に活性化され、ライトコマンドが入力された後、前記クロック信号の所定サイクル後に非活性化される。

(もっと読む)

高速メモリーバス上の同期データ書込み

【課題】コマンド入力用のコマンドクロックと書き込みデータ入力用の書き込みクロックの位相ずれに拘らず正常なタイミングで書き込みデータの取り込みが可能な同期メモリの動作方法を提供する。

【解決手段】メモリコントローラは、クロックとともにストローブ信号をメモリに供給する。該ストローブ信号は書き込みコマンドを検出するとディスエーブルからプリアンブル期間を示すロー状態になり、書き込みデータの先頭に一致する時点でハイになり、書き込みバーストの残りの期間でローになる。メモリはストローブ信号のハイを受信すると書き込みデータの受け取りを開始する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

ドライバ回路及びそのドライバ回路を備えた半導体集積回路

【課題】半導体記憶装置において未使用ビットが存在すると、本来不要であるデータによって、消費電流が増加する問題が存在する。そのため、半導体記憶装置を駆動するドライバ回路であって、未使用ビットが存在する場合には消費電流の低減を実現するドライバ回路が望まれる。

【解決手段】図1に示すドライバ回路は、半導体記憶装置に書き込むデータを構成する複数のビットのうち、半導体記憶装置を含む機器の動作に影響を与えるデータを構成する使用ビットから、半導体記憶装置を含む機器の動作に影響を与えないデータを構成する未使用ビットに書き込むデータを所定の規則に基づいて生成する制御回路を備えている。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

半導体装置およびその制御方法

【課題】半導体装置のデータ入力回路における消費電力を削減すること。

【解決手段】半導体装置は、クロック信号の立ち上がりエッジおよび立ち下がりエッジの少なくともいずれか一方の近傍の期間において活性状態となる制御信号を生成して出力する制御信号生成回路と、制御信号が活性状態である期間においてデータ信号を受信可能な活性状態となり、それ以外の期間において非活性状態となるデータ入力回路と、を備えている。

(もっと読む)

データ入力回路

【課題】プリアンブル期間で内部ストローブ信号がトグルされてもデータストローブ信号の最後の立下がりエッジを正確に感知して書き込み動作のエラーを防止できるようにしたデータ入力回路を提供すること。

【解決手段】プリアンブル期間で発生する内部ストローブ信号のパルスを除去して有効ストローブ信号を生成する有効ストローブ信号生成部と、前記有効ストローブ信号をバースト長情報に応じてカウントして、書き込み動作時にデータを整列するための書き込みラッチ信号を生成するデータストローブ信号カウンタとを備えることを特徴とする。

(もっと読む)

電圧レベルシフト回路および半導体装置

【課題】電圧レベルシフト回路において、入力信号の信号レベルによる応答特性の差違を抑制する。

【解決手段】電圧レベルシフト回路は、入力信号とは異なる電圧振幅を有する出力信号VOUTを生成する。インバータINV2は、入力信号にしたがってVSS〜VDDIの範囲の電圧V1を生成する。インバータINV3は、入力信号にしたがってVSS〜VPERIの範囲の電圧V2を生成する。インバータINV4は、V1およびV2にしたがって出力信号VOUTを生成する。

(もっと読む)

データ入力回路

【課題】ポストアンブル期間でデータストローブ信号のリンギングによる書き込み動作のエラーを防止できるようにしたデータ入力回路を提供すること。

【解決手段】書き込みレイテンシが経過した後に発生するパルスを含むシフト信号を生成し、シフト信号パルスが発生する時点からバースト期間の間、内部クロックをサンプリングしてサンプリングクロックを生成するクロックサンプリング部と、前記シフト信号を前記サンプリングクロックに同期させてラッチしてレベル信号を生成し、バースト信号に応じて、前記レベル信号から最終クロックを生成する最終クロック生成部と、前記最終クロックをラッチしてイネーブル信号を生成し、前記イネーブル信号に応じて整列されたデータをラッチさせて出力する書き込みラッチ信号を生成する書き込みラッチ信号生成部とを備えることを特徴とする。

(もっと読む)

メモリシステム及び半導体記憶装置

【課題】データ入力端子とデータ出力端子を分離し、スループットを向上させるとともに、端子数の増加を抑制できる半導体記憶装置及びメモリシステムを提供する。

【解決手段】少なくとも一つのライトデータ入力端子と、ライトデータ入力端子のN倍の数のリードデータ出力端子と、データ記憶部と、第1の周波数の信号に同期してデータ記憶部から読み出したリードデータをリードデータ出力端子から出力するデータ出力回路と、ライトデータ入力端子から入力したライトデータを第1の周波数のN倍の周波数のライトストローブ信号に同期して取り込み、前記データ記憶部へ送るデータ入力回路と、を備える。

(もっと読む)

半導体装置、データ伝送システム、及び半導体装置の制御方法

【課題】小振幅信号を高速に増幅して出力し、かつ、消費電力の少ないアンプを備える半導体装置を提供する。

【解決手段】クロックに同期してデータが更新される小振幅信号を受信するアンプ部と、アンプ部の出力に接続された出力部と、を備え、アンプ部はクロックに同期して小振幅信号の論理レベルが遷移しうるタイミングで電流源の電流を増加し、遷移しないタイミングで電流を減少する。出力部はクロックに同期してアンプ部の出力データの論理レベルが遷移しうるタイミングで出力インピーダンスを低下させて高速に負荷を駆動すると共に、論理レベルが遷移しないタイミングで出力インピーダンスを増加させて貫通電流が流れることを防ぐ。

(もっと読む)

半導体メモリ

【課題】 半導体メモリのデータ端子を任意に選択可能にし、1つの半導体メモリを様々な端子仕様のコントローラに接続する。

【解決手段】 半導体メモリは、複数のデータ端子と、データ端子にそれぞれ対応して設けられ、対応するデータ端子に供給されるデータを保持するメモリセルを含み、第1許可禁止信号にそれぞれ応じて動作が許可または禁止される複数の内部回路と、設定期間にデータ端子にそれぞれ供給される論理を許可レベルまたは禁止レベルとしてそれぞれ保持し、第1許可禁止信号として出力するレジスタとを有している。

(もっと読む)

半導体装置及びその制御方法並びにデータ処理システム

【課題】複数のコアチップから出力されるリードデータをインターフェースチップにおいて正しく取り込む。

【解決手段】コアチップCC0〜CC7は、パラレルデータの出力に同期したタイミング信号DRAOIFをインターフェースチップIFに出力するタイミング制御回路100を含み、インターフェースチップIFは、タイミング信号DRAOIFに同期してパラレルデータを取り込むデータ入力回路25iを含む。これにより、パラレルデータの出力タイミングと、パラレルデータの取り込みタイミングがいずれもコアチップによって生成されるタイミング信号に同期することから、各コアチップとインターフェースチップとの間に動作速度差がある場合であっても、インターフェースチップ側においてパラレルデータを正しく取り込むことが可能となる。

(もっと読む)

供給ノイズおよび終端ノイズの低減方法およびシステム

【課題】 SSNに関連する問題を軽減するシステムおよび方法を提供すること。

【解決手段】 シングルエンドの通信チャネルを介して第1の集積回路(IC)が第2のICと通信する通信システムを開示する。双方向基準チャネルは、第1のICおよび第2のIC間に延在し、両エンドで終端される。基準チャネルの各エンドにおける終端インピーダンスは、信号を異なる方向に通信するための異なるモードをサポートする。基準チャネルの終端インピーダンスは、それぞれの信号方向に最適化されることができる。

(もっと読む)

入力バッファ回路

【課題】貫通電流の量を低減し、応答速度の低下を抑制する。

【解決手段】差動入力回路と、電源VDDと差動入力回路の一方の電源との間を接続し、差動入力回路の動作状態と非動作状態とを切り替え可能とするPMOSトランジスタ20と、PMOSトランジスタ20に並列に接続され、ゲートに差動入力回路の出力信号を入力するPMOSトランジスタ14と、を備える。PMOSトランジスタ20のサイズは、PMOSトランジスタ14のサイズよりも小さい。接地と差動入力回路の他方の電源との間を接続し、差動入力回路の動作状態と非動作状態とを切り替え可能とするNMOSトランジスタ19と、NMOSトランジスタ19に並列に接続され、ゲートに差動入力回路の出力信号を入力するNMOSトランジスタ13と、をさらに備える。NMOSトランジスタ19のサイズは、NMOSトランジスタ13のサイズよりも小さい。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、データの送受信を精度良く行うことができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、双方向用信号線を介してデータの送受信が行われるSoC回路100及びSDRAM回路101を備え、SoC回路100は、電源と双方向用信号線との間に設けられた抵抗207,208と、抵抗207,208に流れる電流のオンオフを制御するスイッチ209,210と、を有するターミネーション回路204と、データ受信時にはスイッチ209,210をオンし、データ送信時にはスイッチ209,210をオフし、データ受信後にさらに別のデータを受信する場合には、先のデータ受信後から所定の期間スイッチ209,210をオンし続けるように、ターミネーション回路204に対して制御信号200を出力する制御回路205と、を備える。

(もっと読む)

1 - 20 / 63

[ Back to top ]