Fターム[5M024HH14]の内容

Fターム[5M024HH14]の下位に属するFターム

Fターム[5M024HH14]に分類される特許

1 - 13 / 13

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】スタンバイ時においてハイレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDT1L,VSSTLに接続し、スタンバイ時においてローレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDTL,VSST1Lに接続する。スタンバイ時における擬似電源線VDDTL,VDDT1L,VSSTL,VSST1Lの電位VDDT,VDDT1,VSST,VSST1は、VDDT<VDDT1<VDD、VSST>VSST1>VSSを満たす。これにより、スタンバイ状態においてオンするトランジスタのゲート電極と基板との間を流れるリーク電流や、スタンバイ状態においてオフするトランジスタのドレインと基板との間を流れるリーク電流が低減される。

(もっと読む)

半導体回路装置

【課題】階層電源構成を有する半導体回路装置においてサブスレッショルドリーク電流の低減効果を維持しつつスタンバイ状態初期の動作遅延を防止する。

【解決手段】メイン電源線10、メイン接地線14中に抵抗素子50,52を挿入し、その両端の電圧をオフセット差動増幅器54,56で受け、サブ電源線12、サブ接地線16に接続されたトランジスタ58,60を制御する。これにより、サブ電源線12からメイン接地線14に流れるリーク電流、メイン電源線10からサブ接地線16に流れるリーク電流Ileakは、常に一定に維持される。

(もっと読む)

半導体メモリデバイス

【課題】ストレージノードの電圧上昇に起因する誤読み出しを有効に防止する。

【解決手段】メモリセルアレイを構成するメモリセル1Aの各々が、書き込みトランジスタWTと、書き込みトランジスタWTから入力するデータを電気的フローティング状態で保持するストレージノードSNと、ストレージノードSNにゲートが接続され、ストレージノードSNの保持電圧に応じてオンまたはオフすることにより記憶データをソースまたはドレインから出力する読み出しトランジスタ(アンプトランジスタAT)と、を備える。そして、アンプトランジスタATの記憶データの出力側と反対側のソースまたはドレインに、当該ソースまたはドレインの電圧を共通電圧(接地電圧)から上げる昇圧部(ダイオード接続トランジスタDT)が接続されている。

(もっと読む)

オンチップ温度センサ及び温度検出方法、並びにこれを用いたリフレッシュ制御方法

【課題】オンチップ温度センサ及び温度検出方法、そしてこれを用いたリフレッシュ制御方法を提供する。

【解決手段】温度センサは、高温及び低温テストを用いて、温度に対して独立した電流Idを発生させて感知温度変化の基準とする。温度センサは、短い周期でトラッキングコードPcode[n:0]を±1ずつ変化させつつ、温度センサの感知温度を、設定された単位温度ずつ変化させ、温度センサの感知温度がチップの現在温度と同じである時のトラッキングコードを検出する。検出されたトラッキングコードPcode[n:0]によってセルフリフレッシュ周期をセットする。次いで、長い周期ごとに一回ずつトラッキングコードを±1ずつアップデートさせ、アップデートされるトラッキングコードによってセルフリフレッシュ周期を調節する。

(もっと読む)

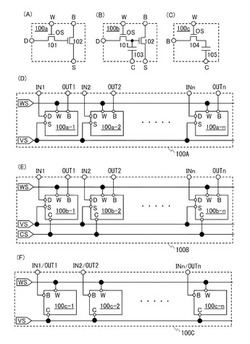

半導体記憶装置

【課題】2トランジスタ型のゲインセルにおいて、誤動作なく安定した読出しが可能で、かつ、面積の小さいメモリセルを有する半導体記憶装置を提供する。

【解決手段】書込みトランジスタM2及び読出しトランジスタM1を有する2トランジスタ型ゲインセルメモリにおいて、書込みワード線WWL、読出しワード線RWL、書込みビット線WBL、及び読出しビット線RBLをそれぞれ別に用意し、各々独立に印加電圧を設定する。さらに、メモリセルMCを、隣接するメモリセルMCと同一の読出しワード線RWL、及び書込みビット線WBLに接続する。

(もっと読む)

半導体記憶装置

【課題】 温度に応じてリフレッシュの周期を細かく変更し、低消費電力にする。

【解決手段】 温度検出部1は、チップの温度を検出し、温度信号tを出力する。基準温度信号出力部2は、チップの温度と比較される複数の異なる基準温度に対応した基準温度信号tbを、選択信号sに応じて出力する。温度比較部3は、温度信号tと基準温度信号tbとによって、チップの温度と基準温度とを比較する。選択信号出力部4は、温度比較部3の比較結果に応じて、選択信号sを出力する。リフレッシュ周期制御部5は、温度比較部3の比較結果に応じて、リフレッシュの周期を変更する。

(もっと読む)

256Megダイナミックランダムアクセスメモリ

【課題】経済的な方法でより高密度なメモリを実現する。

【解決手段】本発明のメモリは、複数のメモリセルと、複数のパッドと、複数のメモリセルと複数のパッドとの間でデータを送信するための複数の周辺装置と、複数の供給電圧を生成する複数の電圧源と、複数の供給電圧を送給する電力分配バスと、電力分配バスの一部を形成するリードフレームを有し、メモリを密閉するパッケージと、を具えている。また、電力分配バスの一部を形成するリードフレームは、接地用バスを形成する。

(もっと読む)

256Megダイナミックランダムアクセスメモリ

【課題】集積回路メモリであるダイナミックランダムアクセスメモリ(DRAM)の設計に於いて、ソリッドステート装置を密閉する方法を提供する。

【解決手段】結合パッドにリードフレームが接続される型式のソリッドステート装置を密閉する方法であって、密閉処理中、タイバーをリードフィンガーの支持体として供することを特徴とする。また、リードフレームの一部分は、ソリッドステート装置の電気回路の一部を形成するのが好ましい。また、タイバーを切断する工程を含むのが好ましい。

(もっと読む)

256Megダイナミックランダムアクセスメモリ

【課題】経済的な方法でより高密度なメモリを実現する。

【解決手段】本発明のダイナミックランダムアクセスメモリは、メモリセルからなる複数の独立アレイであって、それらを通って延びるディジット線を有する複数の独立アレイと、ディジット線を用いて、メモリセルについてデータの書込みとデータの読出しを行なう複数の周辺装置であって、該周辺装置は、ディジット線上の信号を感知する複数のセンス増幅器を具えており、該センス増幅器は、メモリセルに書き込まれるデータ信号の大きさよりも大きな制御信号によって制御される複数の周辺装置と、複数の供給電圧を生成する電源と、複数の供給電圧を、複数の独立アレイ及び周辺装置に送給する電力分配バスと、を具えている。

(もっと読む)

256Megダイナミックランダムアクセスメモリ

【課題】経済的な方法でより高密度なメモリを実現する。

【解決手段】本発明のダイナミックランダムアクセスメモリは、メモリセルの複数の独立アレイであって、行と列に配置されて、複数のアレイブロックを形成する複数の独立アレイと、複数のセンス増幅器を有し、複数のメモリセルについて、情報の書込みと読出しを行なう複数の周辺装置と複数の周辺装置を制御する冗長信号を生成するロジックと、電源と、複数のパッドと、を有しており、金属伝導体の第1層と第2層のみが、複数のメモリセル、複数の周辺装置、ロジック、電源、及び複数のパッドの間の相互接続をもたらしており、冗長信号は、センス増幅器を経由して第2金属層に送られる。

(もっと読む)

ヒステリシス特性を有する温度感知回路

【課題】 ヒステリシス特性を有する温度感知回路を提供する。

【解決手段】 温度信号に応答して可変するリフレッシュ周期を有するDRAM、及びDRAMの温度が第1温度レベル以上である場合、第1の二進値を有する温度信号を生成し、DRAMの温度が第2温度レベル以下である場合、第2の二進値を有する温度信号を生成し、第2温度レベルは、第1温度レベルより低い温度感知回路を備える半導体装置である。

(もっと読む)

1 - 13 / 13

[ Back to top ]