Fターム[5M024JJ58]の内容

Fターム[5M024JJ58]に分類される特許

1 - 20 / 118

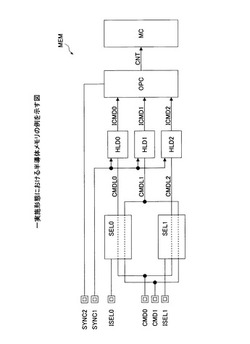

半導体装置

半導体メモリ、半導体メモリの動作方法、システムおよび半導体メモリの製造方法

【課題】少ない数のコマンド端子を用いて、半導体メモリを効率よくアクセスする。

【解決手段】半導体メモリMEMは、選択信号に応じて選択される1つが動作し、複数の第1コマンド端子CMD0、CMD1にそれぞれ供給される複数の第1コマンド信号を受け、受けた第1コマンド信号を出力する複数の第1選択部SEL0、SEL1と、第1選択部の出力に接続され、第1コマンド端子の数より多く、少なくとも1つが第1選択部の複数に共通に接続され、第1選択部の1つから出力される第1コマンド信号を、第1同期信号SYNC1に応答して保持し、第2コマンド信号として出力する複数の保持部HLD0、HLD1、HLD2と、第2コマンド信号に応じた動作制御信号CNTを、第1同期信号に比べて発生頻度が低い第2同期信号SYNC2に応答して出力する動作制御部OPCと、動作制御信号に応じてアクセスされるメモリセルMCとを有している。

(もっと読む)

半導体装置

【課題】小規模な論理回路によって基準レイテンシとオフセットレイテンシを用いた演算を行う。

【解決手段】例えば、基準レイテンシCLの値を示す複数のビットA0〜A3のそれぞれと、オフセットレイテンシSRLの値を示す複数のビットC0〜C2のそれぞれと、を論理合成して複数の制御信号E0〜E3を生成する論理回路100と、複数の制御信号E0〜E3をデコードして複数の制御信号ULPCL4〜ULPCL15を生成する論理回路200とを備える。本発明によれば、基準レイテンシCLの値とオフセットレイテンシSRLの値をデコードする前に演算していることから、より小規模な論理回路によって調整レイテンシULPCLを算出することが可能となる。

(もっと読む)

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

半導体装置

【課題】1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込む。

【解決手段】例えば、モードレジスタ設定信号MRS1を活性化させるコマンドデコーダ82と、モードレジスタ設定信号MRS1を遅延させることによってモードレジスタ設定信号MRS2を生成するレイテンシシフタ83と、データ信号D0がローレベルである場合にはモードレジスタ設定信号MRS2に基づいてモードレジスタ設定信号MRS3を活性化させ、データ信号D0がハイレベルである場合にはモードレジスタ設定信号MRS3を非活性状態に保持する論理ゲート回路G2,G3と、モードレジスタ設定信号MRS3の活性化に応答してモード信号が設定されるモードレジスタ84を備える。これにより、1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込める。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードにエントリしている期間中においてもデータ端子のインピーダンス制御を可能とする。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、インピーダンス制御信号ODTを受信する入力バッファ回路72をセルフリフレッシュモード中においても常時活性化させるとともに、セルフリフレッシュモード中においては、内部クロック信号ICLK0に同期してインピーダンス制御信号IODT0をラッチするラッチ回路84をバイパスさせる。これにより、外部クロック信号CKを使用することなく、セルフリフレッシュモード中におけるインピーダンス制御信号ODTの入力が可能となる。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、セルフリフレッシュモードにエントリすると、オシレータ150を用いてリフレッシュ動作を周期的に実行する。セルフリフレッシュモードにおいて1回のリフレッシュ動作に要する時間をオートリフレッシュの1/4に短縮するとともに、リフレッシュ動作の実行頻度を4倍とする。これにより、セルフリフレッシュイグジットコマンドSRXを発行した後、ロウ系のコマンドの投入が禁止される期間を短縮することが可能となる。

(もっと読む)

モード選択可能プリフェッチおよびクロック対コアタイミングを伴うメモリ装置

【課題】コア速度に過度にストレスをかけずに、広いデータ転送範囲に応じるメモリ装置を提供する。

【解決手段】記憶アレイからリトリーブされたデータの第1の部分またはより小さな第2の部分のどちらかが、プリフェッチモード選択に従ってデータバッファにロードされ、次に、信号インタフェースを介してメモリ装置から出力される。記憶リソースのいずれか1つに連続アクセスを行う間に生じることになるクロック信号の最小サイクル数を示す値は、メモリ装置の構成回路内で受信および記憶する。この値が、閾値数未満であるクロックサイクル数Nを示す場合には、メモリ装置は、クロック信号のNサイクルのそれぞれの間に、信号インタフェースとデータバッファとの間で、第1のアドレスに関連するデータを転送する。Nが閾値数を超えるか等しい場合には、メモリ装置は、別の制御を行う。

(もっと読む)

半導体メモリ、半導体メモリの動作方法およびシステム

【課題】 外部からメモリコアを指定することなく動作の停止が必要なメモリコアのみ動作を停止する。

【解決手段】 動作制御回路は、第1動作コマンドに応答してメモリコアのいずれかの第1動作を開始し、第2動作コマンドに応答してメモリコアのいずれかにおいて所定時間で完了する第2動作を開始し、複数のメモリコアの動作を停止するための停止コマンドに応答して、第1動作を停止するとともに所定時間が経過していない第2動作を継続する。活性化回路は、第1または第2動作コマンドに応答してアクセス信号を活性化する。第1の非活性化回路は、第1動作を停止するために停止コマンドに応答してアクセス信号を非活性化する。非活性化禁止回路は、第2動作を停止するための停止コマンドに応答するアクセス信号の非活性化を禁止する。第2の非活性化回路は、第2動作の完了に同期してアクセス信号を非活性化する。

(もっと読む)

モードレジスタセットを備える半導体メモリ装置

【課題】アドレスピンを追加せずに複数のMRSコマンドを生成することができるモードレジスタセットを備えた半導体メモリ装置を提供する。

【解決手段】データバッファ制御信号DQBUF_ENDBを生成する制御部230と、データバッファ制御信号DQBUF_ENDBに応じて、データパッドDQを介して入力される複数のMRSコードA<0:12>,BA<0:2>をバッファリングして出力するデータバッファ部250と、データバッファ部250から出力される複数のMRSコードA,BAをデータラインGIO,LIOを介して受信し、受信した複数のMRSコードA,BAを用いて複数のMRSコマンドNMRS_CMD<0:12>、EMRS_CMD<0:12>、EMRS2_CMD<0:12>、EMRS3_CMD<0:12>、TMRS_CMD<0:12>を生成する複数のMRSコマンド生成部290A〜290Eとを備える。

(もっと読む)

揮発性メモリのレジスタの読み出し

【課題】SDRAMモジュールにおいて、SDRAMに記憶されていないモードレジスタ等の保持情報をSDRAMに記憶されているデータと同期して読み出すことを可能にする。

【解決手段】DRAM配列に記憶されているデータに対して指示される読み出しコマンド/動作と同等のタイミングおよび動作をするレジスタ読み出しコマンド/動作と呼ばれるデータ転送モードを有する。レジスタ読み出しコマンドは、MRSまたはEMRSコマンドと同じ制御信号状態を含み、固有値に設定されたバンクアドレスをもつ。レジスタ読み出しコマンドは、1つのデータのみを読み出すか、またはアドレスバスを利用して、DRAM配列に記憶されていない複数のデータをアドレス指定し得る。レジスタ読み出し動作は、バースト読み出しであり、バースト長は、種々のやり方で定められ得る。

(もっと読む)

半導体装置

【課題】レイテンシカウンタの制御に必要な制御信号のビット数を低減する。

【解決手段】内部コマンド信号ICMDに奇数サイクルのレイテンシを与えるか否かを選択する第1のレイテンシカウンタ110と、内部コマンド信号に2サイクル単位でレイテンシを与える第2のレイテンシカウンタ120とを備え、これらレイテンシカウンタ110,120が直列接続されている。これにより、設定可能なレイテンシの種類よりもレイテンシを設定するための制御情報のビット数が少なくなることから、配線密度を低減することが可能となる。

(もっと読む)

半導体装置

【課題】レプリカ回路の精度を抜本的に向上する。

【解決手段】半導体装置10は、少なくともフィードバッククロック信号RCLK1に基づいて外部クロック信号CK,/CKを遅延させてなる内部クロック信号RLCLKを出力するDLL回路70と、内部クロック信号RLCLKに同期してデータを出力する複数の出力バッファ64aと、出力バッファ64aのレプリカであり、内部クロック信号RLCLKに同期してフィードバッククロック信号RCLK1を生成し、DLL回路70に供給する出力レプリカ73と、DLL回路70から内部クロック信号RLCLKを受け、複数の出力バッファ64a及び出力レプリカ73に伝送するクロックツリー72とを備え、クロックツリー72は、それぞれDLL回路70から複数の出力バッファ64a及び出力レプリカ73に至る内部クロック信号RLCLKの複数の伝送経路の信号線負荷が互いに実質的に等しくなるよう構成される。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】並列接続された複数の入力回路のうち使用する入力回路を切り替える際に生じる出力ノードの信号ノイズ(ハザード)を防止する。

【解決手段】それぞれが、入力信号INが供給される一つの入力ノードN10に接続し、出力信号OUTを供給する一つの内部出力ノードN11に接続し、互いに電気的特性が異なる第1及び第2の入力回路100A,100Bと、切り替え信号SELを生成し、切り替え信号SELによって、入力回路100A,100Bを制御する入力制御回路300とを備える。入力制御回路300は、入力回路100A,100Bのいずれか一方を活性から非活性へ、いずれか他方を非活性から活性へ切り替えるとき、入力回路100A,100Bが同時に活性状態となる時間を含むように制御する。これにより、入力回路100A,100Bの切り替えに伴う信号ノイズ(ハザード)の発生が防止される。

(もっと読む)

半導体メモリ

【課題】半導体メモリをアクセスするときに、消費電流が一時的に増加するピーク電流を低減する手段を提供する。

【解決手段】半導体メモリ10は、メモリセルアレイ11とデータマスク制御部101とを備える。データマスク制御部101は、メモリセルアレイ11とデータ入出力接点とのデータ授受を制御する内部マスク信号を出力する。データマスク制御部101は、外部から入力または内部で生成されるデフォルトマスク信号に応じて内部マスク信号の待機状態の論理値を可変とする。

(もっと読む)

半導体装置およびその動作方法

【課題】マックスパワーダウンモード(max power down mode)をサポートする半導体装置に関し、マックスパワーダウンモードの進入動作後に1つのバッファリング部のみを使用したとしても、マックスパワーダウンモードの脱出動作を可能にする半導体装置を提供する。

【解決手段】外部から入力される第1モード信号CSBをバッファリングする第1バッファリング部221と、第1バッファリング部221の出力信号ICSBに応答して活性化され、外部から入力される第2モード信号CKEをバッファリングする第2バッファリング部222とを備える。

(もっと読む)

半導体装置

【課題】データストローブ信号のスルーレートを変更することなくデータストローブ信号のクロスポイントの電位を調整可能な半導体装置を提供する。

【解決手段】半導体装置は、外部クロックに基づき第1内部クロックを発生する発生回路と、第1内部クロックに基づき第2及び第3内部クロックを生成する分割回路であり第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを調整するエッジ調整回路を含む分割回路と、エッジ調整回路にエッジ調整信号を供給する調整情報保持部と、第2内部クロックに応じて第1データストローブ信号を発生し第3内部クロックに応じて第1データストローブ信号と位相が異なる第2データストローブ信号を発生する出力回路を備え、エッジ調整回路はエッジ調整信号に応じて第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを可変に調整する。

(もっと読む)

半導体装置

【課題】一の動作の契機を他の動作の契機として利用する場合に、2つの動作が互いに影響し合うことを防止する。

【解決手段】

半導体装置は、制御回路107を備える。制御回路107は、例えば、少なくとも外部及び内部タイマのいずれか一方からコマンドデコーダ109を介して特定信号が供給される度に第1の動作(リフレッシュカウンタ105等)を引き起こし、第1の動作が所定回数に達すると、次に供給される特定信号に応じて、第1の動作に替えて第2の動作(DLLの更新114またはキャリブレーション115)を引き起こす。

(もっと読む)

半導体装置およびデータ処理システム

【課題】ヒューズ素子などの不揮発性記憶素子から記憶内容を低消費電流で読み出す。

【解決手段】タイミング制御回路は、外部リセット信号の状態遷移を契機として、内部リセット信号PRESET1、2を活性化させる。ヒューズ回路30は、ヒューズ素子31と、内部リセット信号PRESET1に応答して、ヒューズ素子31の設定データを取得する読出回路RDと、設定データを一時的に保持し、内部リセット信号PRESET2によってリセットされるラッチ回路L1を備える。タイミング制御回路は、内部リセット信号PRESET2を活性化させることによりラッチ回路L1をリセットし、内部リセット信号PRESET1を所定期間だけ活性化させることにより設定データをラッチ回路L1に保持させる。

(もっと読む)

バイモーダル・データストローブを備えた集積回路

【課題】より高速で動作するシステムに対応すべくデータストローブを改良する。

【解決手段】2種の動作モードを有するメモリ素子130/440/450−1〜130/440/450−8。第一のモードにおいて、データストローブ170−1〜170−8はソース同期されていて、データの送信中である場合、メモリ素子により駆動される。第二のモードにおいて、メモリ素子はデータストローブを駆動しない。このモードでは、データストローブ信号170−1〜170−8は、書込データをサンプリングする自由継続クロックとして用いられる。コントローラ110/425による読込みデータの取得は、システム・クロックからの較正済み内部タイミング基準を用いてコントローラ110/425により計時される。

(もっと読む)

1 - 20 / 118

[ Back to top ]