Fターム[5M024LL20]の内容

Fターム[5M024LL20]に分類される特許

1 - 20 / 59

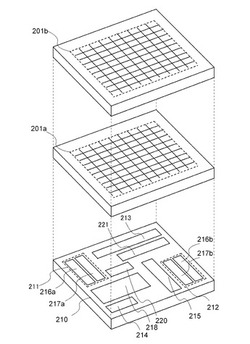

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

DRAMをスタックする方法及び装置

【課題】スタックドメモリチップをシグナルインテグリティ等の問題を排除するように構成する。

【解決手段】第1の速度でアクセス可能な複数のセルから構成されるメモリコアを備え、垂直方向にスタックされた複数のDRAM集積回路と、第1の速度よりも大きい速度で、DRAM集積回路とメモリバスとの間でインタフェースを設けるインタフェース集積回路と、メモリスペアリングとを備え、スタックされたDRAM集積回路が(p+q)個のDRAM集積回路を備え、p個のDRAM集積回路が、メモリ集積回路の作業プールとして用いられる複数のDRAM集積回路を備え、q個のDRAM集積回路が、メモリ集積回路のスペアプールとして用いられる複数のDRAM集積回路を備える。

(もっと読む)

半導体装置

【課題】配線層の空きスペースを利用して電源補償容量を形成する。

【解決手段】Y方向に配列された複数のメモリマットMATと、Y方向に隣接するメモリマットMAT間にそれぞれ配置されたセンス領域SAと、カラム選択信号を生成するカラムデコーダ13と、複数のメモリマットMAT上をY方向に延在し、カラム選択信号をカラムデコーダ13から複数のセンス領域SAに供給するカラム選択線YSと、カラムデコーダ13からみて最も遠いメモリマットMATa上に設けられた電源補償容量30とを備える。電源補償容量30は、容量電極として機能する電源配線VL1,VL2を含み、その少なくとも一方がカラム選択線YSと同じ配線層に形成されている。本発明によれば、カラム選択線YSを形成する必要のないメモリマットMATa上に電源補償容量30を設けていることから、チップ面積を縮小することが可能となる。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置を提供する。

【解決手段】少なくともターミナルの第1対を含むパッケージインターフェースと、半導体チップのスタックと、それぞれ半導体メモリチップに備えられ、すぐに隣接した半導体チップの貫通電極と電気的に連結される貫通電極の複数のスタックと、第1情報を提供するディファレンシャル信号を受信するターミナルの第1対と連結される入力、及び貫通電極の複数のスタックのうち少なくとも一つに、第1情報を含む出力信号をシングルエンド信号のフォーマットで提供する出力を含むインターフェース回路と、を備える半導体パッケージである。

(もっと読む)

半導体装置

【課題】配線間のカップリングノイズの影響によりデータ読み出し時間が長くなるのを抑制した半導体装置を提供する。

【解決手段】所定の方向に沿って配置された複数のメモリセルアレイと、複数のメモリ素子に記録されたデータを読み出すための複数のビット線と、選択されたビット線に現れる電位およびその逆相の電位のそれぞれを増幅し、データ信号を所定の方向とは異なる方向に出力し、データ反転信号をデータ信号の出力方向とは逆の方向に出力するセンスアンプ部と、データ信号およびデータ反転信号に基づくデータを外部に出力するデータ出力回路と、データ信号およびデータ反転信号をデータ出力回路に伝送するための、所定の方向に平行に配置された複数のローカル信号線と、を有し、複数のローカル信号線のうち、隣り合う2本のローカル信号線の所定の方向に垂直な方向の位置が、所定の間隔で交互に入れ替わっている構成である。

(もっと読む)

半導体装置

【課題】一の動作の契機を他の動作の契機として利用する場合に、2つの動作が互いに影響し合うことを防止する。

【解決手段】

半導体装置は、制御回路107を備える。制御回路107は、例えば、少なくとも外部及び内部タイマのいずれか一方からコマンドデコーダ109を介して特定信号が供給される度に第1の動作(リフレッシュカウンタ105等)を引き起こし、第1の動作が所定回数に達すると、次に供給される特定信号に応じて、第1の動作に替えて第2の動作(DLLの更新114またはキャリブレーション115)を引き起こす。

(もっと読む)

半導体記憶装置

【課題】大規模なメモリセルアレイブロック内に分散配置されたセンスアンプを持つ場合に、動作マージンを向上させ、かつ、高速読み出しを実現することができなかった。

【解決手段】複数のメモリセルを有するメモリセルアレイと、前記メモリセルアレイに隣接して配置されるとともに、対応する前記メモリセルから読み出された信号を増幅するセンスアンプと、読み出し信号線と、前記センスアンプと前記読み出し信号線とを選択的に接続する複数の接続回路と、選択信号によって選択された前記接続回路によって前記センスアンプから前記読み出し信号線を経由して読み出された信号を増幅して出力する複数のメインアンプと、前記メインアンプに接続された起動信号線と、前記起動信号線に前記メインアンプの起動信号を出力する起動信号発生回路と、を備え、前記起動信号発生回路は、前記接続回路に近接して配置される。

(もっと読む)

記憶制御装置、記憶装置、記憶装置システム

【課題】ロジックがメモリのリフレッシュ動作を制御する積層型メモリシステムの構成において、個々のメモリの温度情報に基づいてメモリごとのリフレッシュ動作の頻度を個別に変更可能とする。かつ、複数のメモリとロジックとの間での温度情報入出力のための配線を簡易化する。

【解決手段】メモリ200において、入力選択温度情報Dtemp−3と温度センサー220の自己温度情報Dtemp−0とを比較して高い方を出力選択温度情報Dtemp−1として出力させる。出力選択温度情報Dtemp−1と入力選択温度情報Dtemp−3のためのマイクロバンプ500a、500bは、それぞれメモリチップの上側面と下側面とで同じ平面位置に配置する。メモリ200ごとに統合温度用TSV400bを同じ位置に形成することで統合温度情報Dtemp−2対応の信号路を共有させる。

(もっと読む)

記憶装置

【課題】複数のダイナミック型メモリのメモリアレイに対して、温度状態に応じて適切なタイミングによりリフレッシュ動作を行う。

【解決手段】メモリチップ上に複数のメモリアレイ10が配置され、その近傍に温度センサー20が設けられる。温度情報出力部40は、複数の温度センサー20によって生成された温度情報に基づいてメモリチップの外部に総合温度情報を出力する。総合温度情報に応じて、外部からリフレッシュコマンドが入力される。リフレッシュトリガ制御部60は、外部からのコマンド入力および複数の温度センサー20からの温度情報に従って、リフレッシュ動作のトリガとなるリフレッシュトリガを生成する。リフレッシュアドレス制御部70は、外部からのコマンド入力および複数の温度センサー20からの温度情報に従って、リフレッシュアドレス生成部50におけるリフレッシュアドレスの生成を制御する。

(もっと読む)

半導体装置及びその制御方法

【課題】パイプライン動作を行う場合に半導体メモリに対するアクセスにおける使い勝手を向上させる。

【解決手段】各メモリコアMEMが、複数のメモリバンクBANK0〜3に共通に設けられたアドレスバスABUS及びリードライトバスRWBUSと、コマンドデコーダ213からの制御信号に基づいて、アドレスバス上のアドレス情報を取り込むアドレス遅延回路222と、データ読出し動作時はリードライトバス上に読み出すべきデータを一時保持するデータ出力ラッチ237と、データ書込み動作時はリードライトバス上の書き込むべきデータを一時保持するデータ入力ラッチ238とを備え、各メモリバンクに対する各一回のデータ読出し又は書込みアクセスを順次行う一連のデータアクセスを一サイクルとして当該サイクルが繰り返し実行されるように複数のメモリバンクに対するデータアクセスがパイプライン化されている。

(もっと読む)

半導体記憶装置及びデータ処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置においてリフレッシュ動作時におけるピーク電流を低減する。

【解決手段】予め互いに異なるチップ情報LIDが付与される複数のコアチップCC0〜CC7を備え、内部リフレッシュコマンドREFaを互いにタイミングの異なる複数のリフレッシュコマンドREFbに分割し、分割されたリフレッシュコマンドREFbのカウント値C2とチップ情報LIDの少なくとも一部とが互いに一致したコアチップにおいてリフレッシュ動作が実行される。これにより、複数のコアチップCC0〜CC7に内部リフレッシュコマンドREFbが共通に供給される場合であっても、各コアチップにおけるリフレッシュ動作のタイミングをずらすことが可能となる。これにより、リフレッシュ動作時におけるピーク電流を低減することが可能となる。

(もっと読む)

半導体装置

【課題】センスアンプ接地電位の変動で発生するノイズによる誤動作を防いだ半導体装置を提供する。

【解決手段】センスアンプに接地電位を供給するための電極パッドであるセンスアンプ接地電位用パッドと、センスアンプ接地電位用パッドに接続された第1の導電線と、パッド列に含まれる複数の電極パッドのうち、センスアンプ接地電位用パッドとの距離が最も近い電極パッドに接続された第2の導電線と、を有し、第2の導電線がパッド列を基準にして第1の導電線とは反対側に延びている構成である。

(もっと読む)

メモリモジュール

【課題】高いデータ転送レートを実現可能なLoad Reduced型のメモリモジュールを提供する。

【解決手段】モジュール基板110の長辺に沿って設けられた複数のデータコネクタ120と、モジュール基板110に搭載されたメモリチップ200及びデータレジスタバッファ300と、データコネクタ120とデータレジスタバッファ300とを接続するデータ配線L0と、データレジスタバッファ300とメモリチップ200とを接続するデータ配線L1,L2とを備える。各データレジスタバッファ300と、これに対応するデータコネクタ120及びメモリチップ200は、モジュール基板110の短辺方向に並べて配置されている。本発明によれば、データ配線の配線距離が非常に短くなることから、非常に高いデータ転送レートを実現することが可能となる。

(もっと読む)

半導体装置

【課題】高温時にリフレッシュ間隔を狭めることによってDRAMをより広い温度範囲で使用する。

【解決手段】温度計測モジュールTMPは温度を検出し、検出した温度に応じた信号をリフレッシュカウンタRCとアクセスコントローラA_CONTに出力する。リフレッシュカウンタRCは、温度計測モジュールTMPの出力信号によって温度に応じたリフレッシュ間隔の変更を行い、DRAMのリフレッシュ間隔にあわせてリフレッシュを行うアドレスを生成する。アクセスコントローラA_CONTはCHIP2全体動作の制御と、DRAMへアクセスを行うためのアドレスを発生する。

(もっと読む)

半導体記憶装置及びこれを備えるメモリモジュール、並びに、データ処理システム

【課題】ダイナミックODT機能を有する半導体記憶装置において正確なライトレベリング動作を行う。

【解決手段】ライトレベリングモード時に活性化されるスキュー検出回路110と、ODT信号を用いてデータストローブ端子15aに接続された終端抵抗回路を活性化させるODT制御回路200とを備える。ODT制御回路200は、ライトレベリングモード時においてダイナミックODTが不使用状態である場合には第1の抵抗モードを選択し、ライトレベリングモード時においてダイナミックODTが使用状態である場合には第2の抵抗モードを選択する。これにより、実際のライト動作時においてダイナミックODTが使用状態である場合の抵抗値と、ダイナミックODTが不使用状態である場合の抵抗値を再現することができるため、より正確なライトレベリング動作を行うことが可能となる。

(もっと読む)

半導体記憶装置及びこれを備えるメモリモジュール、並びに、データ処理システム

【課題】ライトレベリングモードにエントリした後、速やかにスキューの測定を可能とする。

【解決手段】ライトレベリングモード時に活性化されるスキュー検出回路110と、ODT信号を用いてデータストローブ端子15aに接続された終端抵抗回路を活性化させるODT制御回路200とを備える。ODT制御回路200は、ODT信号を遅延させるカウンタ220,230を含み、通常動作モード時においてはカウンタを通過したODT信号を用いて終端抵抗回路を活性化させ、ライトレベリングモード時においてはカウンタをバイパスしたODT信号を用いて終端抵抗回路を活性化させる。これにより、ライトレベリングモード時においては、ODT信号のレイテンシを待つことなく、速やかにライトレベリング動作を行うことが可能となる。

(もっと読む)

サブワードライン駆動回路

【課題】レイアウト面積の増加なしにワードラインを速くディセーブルさせるサブワードライン駆動回路を提供する。

【解決手段】第1ワードラインを活性及び非活性化する第1ワードライン駆動及びクリア手段P1,N1と、第1ワードラインの電位を接地電位に放出させる第1ワードライン電位放出手段N2と、第2ワードラインを活性及び非活性化する第2ワードライン駆動及びクリア手段P2,N3と、第2ワードラインの電位を接地電位に放出させる第2ワードライン電位放出手段N4と、ワードラインブースティング信号により第1及び第2ワードラインを等しくする等化手段N5と、を含み、等化手段は、第1及び第2ワードライン電位放出手段が形成される領域に形成され、第1及び第2ワードライン電位放出手段は、第1ワードライン駆動及びクリア手段と第2ワードライン駆動及びクリア手段との間に配置される。

(もっと読む)

メモリモジュール及びその使用方法、並びにメモリシステム

【課題】データ入出力パッド13の終端抵抗と終端抵抗のオンオフを制御する信号を入力するための終端抵抗制御パッド14とを備えた同期式メモリチップを多ランク搭載した多ランクメモリモジュールにおいて、メモリモジュールに設けた終端抵抗制御(ODT)端子の数より、ランクの数のほうが大きい場合においても、内蔵終端抵抗を用いて、高速動作を可能にする。

【解決手段】モジュール基板8上のデータバス19とデータ入出力パッド13との配線の長さが長いメモリチップ12の終端抵抗制御パッド14を、終端抵抗制御配線18、21に接続し、ODT端子から終端抵抗のオンオフを制御し、モジュール基板上のデータバス19とデータ入出力パッド13との配線の長さが短いメモリチップ11の終端抵抗制御パッドについて終端抵抗をオンさせるように固定電位20に接続する。

(もっと読む)

メモリシステム、該メモリシステムに搭載されるリフレッシュ動作が必要なメモリ、および該メモリシステムに搭載されるリフレッシュ動作が不要なメモリ

【課題】複数のメモリを備えるメモリシステムにおいて、リフレッシュ動作が不要なメモリが放出する熱の影響を受けてリフレッシュ動作が必要なメモリのリフレッシュ動作におけるデータ保持特性の悪化を防止する。

【解決手段】リフレッシュ動作が必要なメモリとリフレッシュ動作が不要なメモリとを含む複数のメモリを有するメモリシステムにおいて、リフレッシュ動作の不要なメモリに対するアクセスコマンドを認識するコマンド認識部と、コマンド認識部によりアクセス開始指令を認識することに応じて、リフレッシュ動作の周期を、アクセス開始指令の認識以前に設定されていた周期に比して短周期に変更するリフレッシュ周期変更部とを備えて構成されている。

(もっと読む)

積層型メモリ装置、メモリシステム、及びそのリフレッシュ動作制御方法

【課題】複数のメモリの内の第1メモリとは異なる他のメモリが放出する熱の影響を受けて、第1メモリのリフレッシュ動作の性能が劣ることを防止することができる積層型メモリ装置及びそのリフレッシュ動作制御方法を提供する。

【解決手段】所定の周期でメモリセルのリフレッシュ動作が必要な第1メモリ20を含む複数のメモリ20、40がマザー基板10の上に積層され、ワイヤボンディングによってマザー基板上の電極端子11に複数のメモリ20、40が共通接続された積層型メモリ装置1において、積層された複数のメモリの内の最下層に、第1メモリ20を配置した。

(もっと読む)

1 - 20 / 59

[ Back to top ]