Fターム[5M024QQ02]の内容

Fターム[5M024QQ02]に分類される特許

1 - 15 / 15

半導体装置

【課題】不要にリフレッシュ周期が変更されることによる無駄な消費電流を削減する。

【解決手段】複数の半導体チップを備え、複数の半導体チップのうちの第1の半導体チップは第1の温度センサを有し、第1の半導体チップとは異なる第2の半導体チップはリフレッシュ動作を必要とする半導体チップであって、第1の半導体チップの第1の温度センサの出力結果に応じて第2の半導体チップのリフレッシュ周期が変更される。

(もっと読む)

半導体装置

【課題】センスアンプのセンスマージンを拡大する。

【解決手段】2つの素子分離領域3に隣接して各ウェル1,2にドライバトランジスタ4a,5a,4b,5bをそれぞれ配置し、各ウェル1,2にドライバトランジスタ4a,5a,4b,5bよりも素子分離領域3a,3bから離れた位置にクロスカップルされた2つの一対のセンストランジスタ6a乃至9a、6b乃至9bをそれぞれ配置する。これにより、センストランジスタ6a乃至9a、6b乃至9bと夫々対応する素子分離領域3a,3bと間に一定以上の距離が確保されることから、素子分離領域3a,3bからの距離によってトランジスタのしきい値が変化する現象の影響が低減され、その結果、夫々クロスカップルされた一対のトランジスタの特性を正確に一致させることが可能となる。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

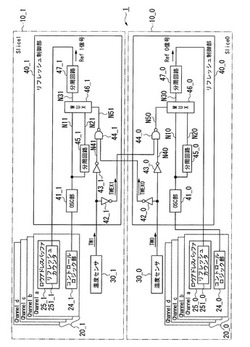

ディレイパルス発生回路、および半導体記憶装置

【課題】入力信号を基にディレイパルスを発生させる場合に、ディレイパルスのパルス幅の温度依存性を低減できるディレイパルス発生回路を提供する。

【解決手段】入力信号Aから所定のパルス幅のディレイパルスを生成するため使用されるディレイ回路を、ディレイ量が温度の上昇に伴い増加する通常ディレイ回路41〜44と、ディレイ量が温度の上昇に伴い減少する逆温度特性ディレイ回路31〜34と、で構成する。そして、通常ディレイ回路41〜44におけるディレイ量と、逆温度特性ディレイ回路31〜34におけるディレイ量とを合わせて、温度依存性を低減させたディレイ量を得るようにし、このディレイ量を基にディレイパルスを生成する。

(もっと読む)

半導体装置

【課題】製造プロセス、電源電圧、接合温度等の変動要因を補償して、センスアンプの動作マージンの低下を防止する。

【解決手段】階層型ビット線構造の半導体記憶装置におけるシングルエンド型のセンスアンプが、メモリセルからビット線に出力される信号を増幅する第1のMOSトランジスタと、第1のMOSトランジスタの出力をグローバルビット線に供給する第2のMOSトランジスタと、グローバルビット線電圧判定回路とを含み、第1のMOSトランジスタのレプリカとグローバルビット線電圧判定回路のレプリカとを含む遅延回路の出力信号により、少なくとも第2のMOSトランジスタのON/OFFタイミングあるいはグローバルビット線電圧判定回路を含むグローバルセンスアンプの読み出しタイミングを制御する。

(もっと読む)

半導体メモリ装置およびその動作方法

【課題】各種のメモリタイプのメモリとして使用でき、しかも、コントロールデバイスにおける制御負担を軽減できる半導体メモリ装置およびその動作方法を提供する。

【解決手段】メモリアレイが形成されたメモリアレイ部3と、外部装置とメモリアレイ部3との間のインターフェースを行うインターフェース部2と、インターフェースに応じたモードを示す任意のモード信号を設定可能なモード信号保持部25と、を有し、インターフェース部2は、複数のメモリタイプにそれぞれ対応し、モード信号に応じて選択的に上記外部装置と上記メモリアレイ部との間のインターフェース処理に適用される複数のインターフェースモジュールを含み、モード信号保持部25は、各モード信号が記憶される不揮発性メモリと、不揮発性メモリから読み出されたコマンドを一時的に保持しておくモードレジスタと、を含む。

(もっと読む)

半導体記憶装置

【課題】配線ピッチが微細化した場合などでも読み出し電圧を確保する。

【解決手段】サブビット線SBL00〜SBLn3等は、第1メタル(第1金属配線層)で形成されている。一方、メインビット線は、第2、第3メタル(第2、第3金属配線層)に分散して形成されている。これにより、メインビット線のカップリング容量やオーバラップ容量が小さく抑えられ、カップリングノイズの影響も低減される。

(もっと読む)

半導体記憶装置

【課題】 電源立ち上げ時において、揮発性メモリの通常動作で必要とされる設定情報の設定を、簡単な構成で、処理時間及びCPU負荷を低減できる半導体記憶装置を提供する。

【解決手段】 揮発性の第1データ記憶領域21に対する通常動作の実行に必要な設定情報を記憶する揮発性のモードレジスタを備える揮発性半導体記憶装置20と、不揮発性の第2データ記憶領域12と設定情報を有する不揮発性の設定情報記憶領域を備える不揮発性半導体記憶装置10を備え、不揮発性半導体記憶装置10が、電源立ち上げ検知手段30と、電源立ち上げ後、通常動作前に、揮発性半導体記憶装置20に対し、設定情報を自動的に送出する設定情報送出手段13と、を備え、揮発性半導体記憶装置20が、電源立ち上げ後、通常動作の実行前に、不揮発性半導体記憶装置10から設定情報を受け付けてモードレジスタに記憶する設定情報記憶手段を備えて構成される。

(もっと読む)

半導体記憶装置

【課題】待機動作における消費電力を削減すると共に、待機機能の実装に伴う面積オーバヘッドを最小化した半導体記憶装置を提供する。

【解決手段】セルデータを記憶するメモリセルアレイ1と、セルデータの誤り訂正のための冗長データを記憶する冗長メモリセルアレイ2とにより、ビット線BLが共有される。セルデータ及び冗長データは、センスアンプ5により検知・増幅されて巡回冗長符号化器/復号化器7に出力される。巡回冗長符号化器/復号化器7は、セルデータを逐次処理して符号化して冗長データを生成し又はセルデータ及び冗長データを逐次処理して復号化しセルデータの誤り訂正を実行する。ロウデコーダ3,4及びカラムデコーダ9がビット線BL、ワード線WL及び冗長ワード線RWLを選択的に活性化することにより、巡回冗長符号化器/復号化器7が出力したセルデータ及び冗長データがメモリセルアレイ1又は冗長メモリセルアレイ2に書き込まれる。

(もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の静的消費電流テストを、一枚のウェーハ上で、複数の半導体集積回路装置で同時に行っても、半導体集積回路装置個々の静的消費電流特性を、高い精度で測定できる半導体集積回路装置を提供すること。

【解決手段】 少なくとも2つ以上の第2導電型の第1の半導体領域22と、半導体基板と絶縁され、第1の半導体領域22に形成された第1導電型の第2の半導体領域25と、少なくとも2つ以上の第1の半導体領域22を分離、かつ隣接して形成し、第1の半導体領域22と第2の半導体領域25とに形成される半導体素子により構成された半導体集積回路部と、半導体集積回路部に動作電圧を与えるために、第1の半導体領域22と第2の半導体領域25に少なくとも1つの高電位及び低電位電源端子と、少なくとも2つ以上の第1の半導体領域22を分離、かつ隣接して形成された領域以外に、基板にバイアス電位を印加する端子503を具備する。

(もっと読む)

半導体メモリ装置及びこれを具備するメモリシステム、並びにそのスイング幅制御方法

【課題】半導体メモリ装置及びこれを具備するメモリシステム、並びにそのスイング幅制御方法を提供する。

【解決手段】半導体メモリ装置は、校正コードに応答してデータスイング幅をそれぞれ可変する複数の出力ドライバと、対応する出力ドライバのデータスイング幅によって校正コードを可変してデータスイング幅を校正スイング幅に校正した後、対応する出力ドライバのデータが正常に伝送される範囲内で校正コードを再び可変してデータスイング幅を減少させる複数のデータスイング幅制御部とを具備することを特徴とする。これによって、半導体メモリ装置は、データが正常に伝送される範囲内でデータのスイング幅を最小化し半導体メモリ装置の電力消費を最小化すると共に、メモリシステムの動作性能を向上させる。

(もっと読む)

低電圧センス増幅器および方法

第1センス増幅器(110)は、一対の相補センス線(S、S*)間に接続された相補入力および出力を有する。各センス線(150、152)は、結合トランジスタを介して、各相補ディジット線(D、D*)に接続される。結合トランジスタは、初期センス期間に起動され、ディジット線からの差動電圧をセンス線に接続する。その後センス線は、ディジット線から分離され、ディジット線の容量からの負荷を受けることなく、第1センス増幅器を差動電圧に対応させる。また、センス線は、ディジット線に接続された相補出力を有する第2センス増幅器の相補入力に接続される。第2センス増幅器(120)をディジット線ではなくセンス線に接続することにより、第2センス線に印加された差動電圧は、ディジット線間の差動電圧よりも早く増加する。  (もっと読む)

(もっと読む)

半導体集積回路装置及びそのテスト方法

【課題】

メモリマクロに対して冗長置き換え情報を記憶する不揮発性記憶回路の数を削減できるとともに、冗長置き換え情報の転送のための入出力回路を簡素化できる半導体集積回路装置を提供すること。

【解決手段】

本発明にかかる半導体集積回路装置では、不良セルを置き換える冗長回路を有する複数のメモリマクロ3と、複数のメモリマクロ3から選択される第1のメモリマクロ3の不良セルを冗長回路に置き換えるための冗長置き換え情報を記憶する複数のヒューズボックス2とを備え、冗長置き換え情報は、ヒューズボックス2からメモリマクロ3へ並列に転送される。

(もっと読む)

1 - 15 / 15

[ Back to top ]