国際特許分類[G01R31/316]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | 電気的性質を試験するための装置;電気的故障の位置を示すための装置;試験対象に特徴のある電気的試験用の装置で,他に分類されないもの (15,110) | 電子回路の試験,例.シグナルトレーサーによるもの (5,767) | アナログ回路の試験 (200)

国際特許分類[G01R31/316]の下位に属する分類

限界試験

機能試験

国際特許分類[G01R31/316]に分類される特許

1 - 10 / 200

インターフェースボード

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

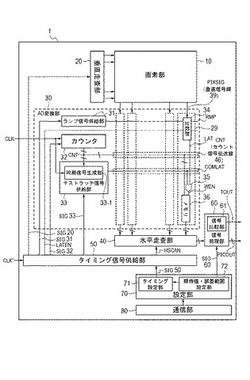

アナログデジタル変換回路、撮像装置、アナログデジタル変換回路の検査方法

【課題】 カウンタが複数のメモリに共通してカウント信号を供給する列ADCにおいて、カウンタからメモリへカウント信号を伝送する信号経路の不良によって生じる、メモリに供給されるカウント信号の遅延を好適に検出することを目的とする。

【解決手段】 カウント信号の信号値が変化したタイミングに応じて、カウント信号をメモリに保持させるラッチ信号をメモリに供給するテストラッチ信号供給部を有するアナログデジタル変換回路である。

(もっと読む)

アナログ/デジタル変換回路及び半導体装置

【課題】アナログ/デジタル変換器のより詳細な故障診断のための技術を提供する。

【解決手段】アナログ/デジタル変換回路(100〜108)は、入力されたアナログ信号(x、15)を所要の演算式(f(x))にしたがって診断用に演算する演算部(12)と、前記入力されたアナログ信号(x)又は前記演算部によって演算されたアナログ信号(y)のいずれかを選択する第1選択部(11)と、前記第1選択部によって選択されたアナログ信号をデジタル信号に変換する変換部(10、21、22、23)とを有する。

(もっと読む)

半導体装置、その検査方法および送信回路

【課題】光結合部の伝送マージンを確保して復調誤りを抑制し、高精度の信号伝送を可能とする半導体装置、その検査方法および送信回路を提供する。

【解決手段】半導体装置100は、アナログディジタル変換部3と、ディジタル信号に応じたパルスパターンである伝送信号を出力するパルス幅変調部5と、固定パルスである参照信号を生成する参照信号生成部7と、を備える。そして、前記伝送信号および前記参照信号のいずれかを選択する第1の制御部13と、前記伝送信号または前記参照信号に基づく駆動電流を出力する発光素子駆動部9と、前記伝送信号または前記参照信号基づく光信号を放出する発光素子15と、を備える。さらに、前記光信号を電圧信号に変換する光受信部21と、前記電圧信号を前記伝送信号または前記参照信号に基づくディジタル信号に復調する復調部25と、を備える。

(もっと読む)

テスト回路

【課題】アナログデジタル変換器の微分直線性を小規模な回路構成に基づいて検査できるようにすること。

【解決手段】テスト回路は、アナログデジタル変換器から出力された第1のデジタル値を格納する第1のレジスタと、アナログデジタル変換器から出力された第2のデジタル値を格納する第2のレジスタと、第1のレジスタに格納された第1のデジタル値と第2のレジスタに格納された第2のデジタルとの差分値を算出する差分算出器と、差分値が所定の上限値と所定の下限値との間に含まれる否かを判定し、判定結果を出力する比較判定器と、を備えている。

(もっと読む)

半導体装置および半導体装置の測定方法

【課題】半導体ウエハ上の半導体チップのアナログ特性の測定を精度良く行えるようにする。

【解決手段】半導体チップ1の被測定部3は半導体素子3a、回路3bである。被測定部3のアナログ特性を測定する測定回路4を設けている。測定回路4は、外部電源からプローブ針Pa、Pbを介して給電され、内部で測定用印加電圧を生成し、配線パターン5を介して被測定部3に印加する。測定回路4は、被測定部3の出力を配線パターン5から入力し、デジタルデータに変換する。測定回路4と配線パターン7を介して半導体チップ2の不揮発性メモリ6に接続され、デジタルデータが転送記憶される。一連の測定が終了した後に、不揮発性メモリ6からデジタルデータを取り出す。プローブ針の接触抵抗や浮遊容量の影響を低減して精度良いアナログ特性の測定ができる。

(もっと読む)

逐次比較型ADコンバータおよびその検査方法

【課題】ADコンバータの変換時間および検査時間を削減する。

【解決手段】

本発明にかかる逐次比較型ADコンバータ10は、アナログ入力をサンプルホールドするサンプルホールド回路13と、サンプルホールド回路13から出力された電位と基準電位とを逐次比較する比較器14と、比較器14による比較結果を記憶する逐次比較レジスタ15と、逐次比較レジスタから出力された比較結果のうち上位ビットの値を記憶するSAR上位ビットレジスタ17と、逐次比較レジスタ15から出力された比較結果の下位ビットの値に基づいて、比較器14における次回以降の逐次比較を全ビットについて行うか、または下位ビットについてのみ行うかを設定するスキップフラグ設定回路18と、を備える。

(もっと読む)

半導体試験装置

【課題】 正極出力と負極出力との差分値に基づく良否判定にかかる時間を短縮して、被試験デバイスの階調テストに要する時間を短縮する半導体試験装置を提供する。

【解決手段】 本発明の代表的な構成は、FPDドライバ102の階調テストを行う半導体試験装置100において、FPDドライバ102のピンから出力される正極出力または負極出力をA/D変換するA/D変換器112a〜112nと、A/D変換された正極出力または負極出力の一方を記憶しておくメモリ118と、メモリ118に記憶された正極出力または負極出力の一方を出力したものと同じピンについて、A/D変換された負極出力または正極出力の他方の入力を受けて、正極出力と負極出力との差分値を逐次演算する差分演算回路114と、を有することを特徴とする。

(もっと読む)

半導体集積回路

【課題】A/Dコンバータ及びD/Aコンバータをいずれも含んだアナログモジュールを備えた半導体集積回路において、アナログモジュールの調整コストを低減する。

【解決手段】テスト起動端子TSを介して起動指令が入力されると、アナログモジュールの動作特性が、目標特性と一致していない場合、一方の調整パラメータを固定し他方の調整パラメータを可変設定しながらテスト処理を実行することによって得られた判定結果(近似度を含む)から、他方の調整パラメータの最適値を求め(S210〜S260)、次は、固定側と可変設定側とを入れ替えて、固定側は、調整パラメータを直前の処理で求められた最適値に固定して同様の処理を実行する(S270〜S310)、その結果、アナログモジュールの動作特性が目標特性と一致したときに設定されている調整パラメータを用いる。

【選択図】図4  (もっと読む)

(もっと読む)

半導体装置

【課題】RFチップ本来の回路特性を抽出できるようにする。

【解決手段】半導体試験装置より出力された変調信号を増幅して出力する低雑音増幅器より出力される信号が供給されるとともに、低雑音増幅器により増幅された後に直交復調処理された変調信号を半導体試験装置用基板の伝送路に対して出力する増幅器に入力される信号が供給される試験回路をRFチップに備える。試験回路は、半導体試験装置より出力する変調信号の波形データが予め記憶され、低雑音増幅器より出力される信号及び増幅器に入力される信号をスペクトラム解析した解析結果と記憶されている変調信号の波形データとの比較によりRFチップにおけるチップ内ノイズ及びRFチップ本来の回路特性を抽出する。

(もっと読む)

1 - 10 / 200

[ Back to top ]