国際特許分類[G05F3/24]の内容

物理学 (1,541,580) | 制御;調整 (21,505) | 電気的変量または磁気的変量の調整システム (3,201) | 自己調整特性を有する一つの非制御素子,または複数の素子から成る組合せであって自己調整特性を有するものによって,電気的変量を調整する非反作用系 (687) | 電流または電圧の調整 (687) | 直流のもの (678) | 非線形特性を有する非制御素子を使用するもの (675) | 半導体装置であるもの (675) | ダイオードトランジスタの組合せを用いるもの (666) | トランジスタは電界効果型のみであるもの (240)

国際特許分類[G05F3/24]に分類される特許

1 - 10 / 240

半導体集積回路、および、半導体記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

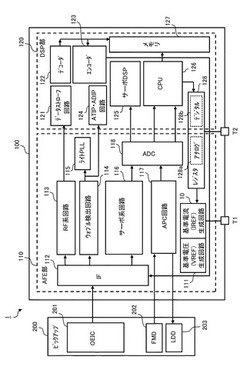

半導体装置、光ディスク装置及び半導体装置のテスト方法

【課題】コストの低減を図りつつ、かつ、精度よく基準電流を生成することが可能な半導体装置、光ディスク装置及び半導体装置のテスト方法を提供する。

【解決手段】半導体装置100は、基準電流を生成する電流生成回路と、記生成された基準電流をテスタ300へ出力する外部端子T1と、基準電流の電流値を制御するための電流制御データを、外部端子T1から出力された基準電流に応じてテスタ300により設定される外部端子T2と、テスタ300により設定された電流制御データにしたがって、電流生成回路により生成される基準電流が所定値となるように調整する電流制御部14と、を備える半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基準電圧発生回路を構成するエンハンスメント型MOSFETとデプレッション型MOSFETとの間の温度特性の差を小さくすることができ、基準電圧発生回路の出力電圧の温度特性を改善することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6上においてRef回路領域8およびCMOS領域7に跨るようにゲート絶縁膜66を形成した後、CMOS領域7の部分を選択的に除去する。次に、熱酸化により、ゲート絶縁膜66が除去されたCMOS領域7に第1ゲート絶縁膜12を形成し、同時に、Ref回路領域8に残っているゲート絶縁膜66を厚くして第1ゲート絶縁膜12よりも厚い第2ゲート絶縁膜13を形成する。

(もっと読む)

昇降圧回路、スイッチ回路

【課題】駆動用のMOSトランジスタのオン抵抗が小さく、リーク電流の発生を防ぎ、しかも小型化、低消費電力化に適した昇降圧回路を提供する。

【解決手段】入力電圧IN2が入力される入力端子104、入力電圧IN2に基づいてVCCまたはGNDを出力するMOSトランジスタ201、203、入力電圧IN2に基づいて2VCCまたはGNDを出力するMOSトランジスタ202、204、MOSトランジスタ201、202に一端が接続され、他端がMOSトランジスタ202、204に接続される容量素子206、ソース・ドレイン端子の一方に2VCCが供給され、ソース・ドレイン端子の他方にVCCが供給され、2VCCまたはGNDがゲート端子に供給され、2VCCまたはGNDによってオン、オフされるMOSトランジスタ205と、によって昇圧回路を構成する。

(もっと読む)

定電流回路及び基準電圧回路

【課題】高温時でもエンハンスメント型Nチャネルトランジスタが弱反転状態で動作できる定電流回路を提供する。

【解決手段】カレントミラー回路と定電流生成ブロック回路とオフリーク回路を備えた定電流回路において、オフリーク回路は、ゲートとソースが接地端子に接続され、ドレインが定電流回路の出力に接続される第一のエンハンスメント型Nチャネルトランジスタで構成される。これにより、定電流を生成するエンハンスメント型Nチャネルトランジスタのゲート−ソース間電圧の上昇を抑えることで、弱反転状態での動作を保つ。

(もっと読む)

基準電圧発生回路

【課題】比較回路の基準値を調整するのに、抵抗成分の異なるMOSのトランジスタを利用することにより、低コストの製造を可能とし、しかも、こうした基準値設定回路やこれを含む制御回路等のワンチップ化を可能にする。

【解決手段】 入力信号の電圧を基準値と比較する比較回路において、所定電圧間に、抵抗成分の合計値が共通する複数のMOSトランジスタを直列接続した組を複数組並列に接続する。MOSトランジスタの各組において、各MOSトランジスタの抵抗成分の比率を変更することにより、各MOSトランジスタの組毎に異なる基準電圧を比較回路に出力する基準値設定回路を設けた。

(もっと読む)

基準電圧回路

【課題】出力電圧における温度補償をする際の抵抗のばらつきの影響を低減する。

【解決手段】基準電圧(Vref)を生成して出力端から出力するバンドギャップリファレンス回路(1)と、基準電圧の分割電圧(ノードAの電圧)とダイオード(36)の順方向電圧との差電圧に応じて差電圧を電流に変換する電圧電流変換回路(3に相当)と、を備え、電圧電流変換回路は、変換された電流(19)を出力端にフィードバックする。

(もっと読む)

過電流検出回路

【課題】温度変化の影響を受けにくい過電流検出回路を提供する。

【解決手段】ダイオード列55を設け、ダイオード列55のアノード端をデプレッション型トランジスタDNM1のソース端子に接続するとともに、ダイオード列55のカソード端とデプレッション型トランジスタDNM1の基板を基準電位に接続する。ダイオード列55を構成する各ダイオードの順方向電圧をVf、ダイオード列55を構成するダイオードの数をm(mは1以上の整数)とすると、デプレッション型トランジスタDNM1の基板バイアス電圧Vbは、Vb=m×Vfとなる。ダイオードの順方向電圧Vfは負の温度係数をもつから、基板バイアス電圧Vbも負の温度係数をもつ。これにより閾値電圧に負の温度係数をもたせて、ドレイン電流IDの温度特性と相殺させる。

(もっと読む)

半導体集積回路

【課題】クランプ電圧を正確な値に設定できる半導体集積回路を提供することを目的とする。

【解決手段】第1の電圧である電源を供給されて定電流を発生する定電流部60と、定電流部60で発生された定電流を供給されて第1の電圧より低い第2の電圧を発生し、第1の電圧の電源を第2の電圧にクランプするクランプ部71と、クランプ部71でクランプされた電源を供給されて基準電圧を発生する基準電圧発生部72とを有し、クランプ部71は、ゲートとドレインに接続され縦型接続された複数段のMOSトランジスタM11−1〜M11−nである。

(もっと読む)

基準電圧回路

【課題】プロセス変動によるバラつき要因が少ない基準電圧回路の提供。

【解決手段】第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

(もっと読む)

1 - 10 / 240

[ Back to top ]