国際特許分類[G06F11/18]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 故障の発生への応答,例.耐故障性 (1,764) | ハードウェアに冗長性を持たせることによるデータのエラー検出または訂正 (1,266) | 冗長回路のエラーを受動的にマスクすることによるもの,例.カッディングまたは多数決回路によるもの (261)

国際特許分類[G06F11/18]に分類される特許

1 - 10 / 261

高速情報処理システム

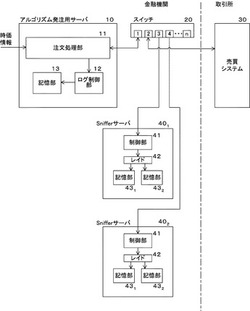

【課題】取引情報を送信するときに送信処理に遅延を起すことなく且つ送信する取引情報のログを確実に記憶することができる高速情報処理システムを提供する。

【解決手段】本発明の高速情報処理システムは、アルゴリズム発注用サーバ(主サーバ)10と、アルゴリズム発注用サーバ10から送られる発注情報を取引売買システム(外部のシステム)30に送出すると共に、その発注情報をコピーするポートミラーリング機能を有するスイッチ(中継切替手段)20と、スイッチ20によって作成された発注情報のコピーを受信して、発注情報のログを記憶するためのSnifferサーバ(ログ用サーバ)40とを備えている。本発明によれば、高速で取引情報を送信する際に、取引情報を送信するための送信処理に影響を与える遅延を最小限に抑えて、送信する取引情報のログを記憶することができる。

(もっと読む)

高完全性処理を提供する方法

【課題】高集積度マイクロプロセッサにおいて、ロックステップで動作できる機能を提供する。

【解決手段】高完全性処理を提供する方法として、各レーン12、14がアプリケーションプロセッサ20、40を有し、それらのアプリケーションプロセッサが非ロックステップ構成において同じアプリケーションソフトウェアを実行する少なくとも2つの冗長処理レーンを有し、アドレス可能な空間へのアクセスを必要とするトランザクションを出力する高完全性処理システムにおいて、同期および完全性検査を提供する方法。

(もっと読む)

高整合性処理を提供する方法

【課題】マイクロプロセッサにて、ロックステップで走る能力を実現する。

【解決手段】非ロックステップ構成での少なくとも2つの冗長なアプリケーションプロセッサ(12および14)を有する高整合性処理システム10において高整合性通信を提供する。それらの冗長なアプリケーションプロセッサ(12および14)は同じアプリケーションを走らせていて、それらの冗長なアプリケーションプロセッサ(12および14)は、通信チャネル18によって少なくとも1つの入出力プロセッサ16に接続される。

(もっと読む)

バス同期2重系コンピュータシステム

【課題】バス同期2重系コンピュータシステムの制御対象の稼働率を向上させる。

【解決手段】同一情報に対し同一演算処理を同期して行う2個の演算部2A,2Bの各データを照合部4で照合した結果から制御対象の動作を制御するコンピュータシステムにおいて、2個の演算部2A,2Bと別に予備演算部3を設け、前記照合部4の照合前に2個の演算部2A,2Bと予備演算部3の各データを別の照合部5で相互に照合した結果から予備演算部3が正常で2個の演算部2A,2Bのいずれか一方が異常のとき異常側演算部を予備演算部3に切替えるバス同期2重系コンピュータシステム。

(もっと読む)

フェイルセーフマイコン

【課題】同一の処理を同期して行う2系統の処理装置を含むフェイルセーフマイコンにおいて、ノイズなどの外乱によって動作が誤って停止されてしまうことを抑制して、制御対象機器の稼動率を高める。

【解決手段】自系の照合データを他系に出力し(S101)、他系の照合データを入力し(S102)、自系の照合データと他系の照合データとを照合する(S103)。次いで、自系の照合結果を他系に出力し(S104)、他系の照合結果を入力し(S105)、これら照合結果の組み合わせの正常・異常を判定する(S106)。正常であれば、自系の照合結果をそのまま出力するが(S107)、異常である場合には、エラーカウンタの値をインクリメントし(S109)、エラーカウンタの値と閾値とを比較する(S110)。そして、エラーカウンタの値が閾値を超えるまでは、S101〜S106の照合動作を再度実行させ、閾値を超えると異常処理を実行する(S111)。

(もっと読む)

電子制御装置

【課題】第1のマイコンの異常を第2のマイコンにより確実に監視することが出来る電子制御装置を提供する。

【解決手段】少なくとも2個のマイクロコンピュータを有し、第1のマイクロコンピュータ(3)が主に制御対象の制御を司り、第2のマイクロコンピュータ(4)が、主に第1のマイクロコンピュータ(3)の異常の監視を行なうように構成された電子制御装置であって、第1マイクロコンピュータ(3)は、自身が制御量の演算に用いるデータの少なくとも一部を、自身の演算リソースを用いずに第2のマイクロコンピュータ(4)に送信するように構成され、第2のマイクロコンピュータ(4)は、送信されたデータに基づいて第1のマイクロコンピュータ(3)の異常の有無を判断するように構成されている。

(もっと読む)

情報処理装置

【課題】ロックステップ方式で動作する情報処理装置において、エラー情報の出力による処理負荷を低減し、演算処理の停止や遅延を抑制する。

【解決手段】プロセッサコア1A、1Bがエンジン制御用の演算処理を実行している期間は通知不要フラグ33をオフに設定し、補助的な処理や空のループ処理等を実行している期間は通知不要フラグ33をオンに設定する。比較手段2は、2つのプロセッサコア1A、1Bによる演算処理結果が不一致であった場合に通知不要フラグ33の設定を参照し、通知不要フラグ33がオフに設定されている期間にはエラー情報を出力し、エラー処理手段32がエラー処理を実行するようにし、通知不要フラグ33がオンに設定されている期間には、エラー情報を出力しない。これにより、エラー処理の必要性の低いエラー情報の出力処理が抑制され、プロセッサコア1A、1Bの処理負荷が低減される。

(もっと読む)

情報処理装置、情報処理システム、情報処理装置の異常兆候検出方法、及び異常兆候検出プログラム

【課題】他の情報処理装置のCPUとの間で同期ずれが発生したCPUで、異常兆候を検出する。

【解決手段】情報処理装置10は、CPU11と、入出力関連装置13と、同期制御部14と、他の情報処理装置20との間で情報を送受信する通信部17とを備える。同期制御部14は、CPU11を初期化する初期化設定部140と、CPU11と入出力関連装置13間のトランザクションを監視するトランザクション監視部141と、トランザクションの監視情報と他の情報処理装置20から受信したトランザクションの監視情報とからCPU11の同期ずれを判定する同期判定部142と、トランザクションの監視情報に基づき、異常兆候関連情報を取得する異常兆候関連情報取得部143と、同期ずれ有りのとき、異常兆候関連情報に基づき、CPU11の異常兆候の有無を判定する異常判定部144とを備える。

(もっと読む)

モジュール、周波数制御方法、及び周波数制御プログラム

【課題】 複数のプロセッサが同一処理を同期を取りながら同時に行う、同期状態を保ったまま、各プロセッサの動作周波数を変更するモジュールを提供する。

【解決手段】 本発明のモジュールは、同期して同一処理を実行するプロセッサを有する、同一構成の複数のモジュールを含み、前記複数のモジュールのプロセッサに対して通知される割り込みが、同時に全てのモジュールのプロセッサに対して通知されるフォールトトレラントコンピュータの、前記複数のモジュールに含まれ、周波数変更指示を入力する指示入力手段と、前記周波数変更指示を入力すると前記プロセッサに割り込みを通知するプロセッサ制御手段と、前記割り込みを受信すると、前記同一処理を中断し、当該プロセッサの周波数の変更を行い、周波数の変更の時刻から、前記複数のモジュール全てのプロセッサの周波数が切り替わる時間以上の所定時間経過後に、中断した前記同一処理を再開する前記プロセッサとを含む。

(もっと読む)

二重化情報処理システム

【課題】二重化運転を速やかに開始することができないこと。

【解決手段】動作系情報処理システム1aに待機系情報処理システム1bを同期化させる際、キャッシュコピー手段5が動作系のキャッシュメモリ3aの内容を待機系のキャッシュメモリ3bにコピーすると共に、主記憶コピー手段6が動作系の主記憶装置2aの内容を待機系の主記憶装置2bにコピーする。主記憶アービタ手段7は、主記憶コピー手段6によるコピーが完了するまでの間、動作系のCPU4aおよび待機系のCPU4bからのリードおよびライトを動作系の主記憶装置2aに対するリードおよびライトとして処理する。動作系のCPU4aと待機系のCPU4bは、キャッシュコピー手段5によるコピーの完了時、主記憶コピー手段6によるコピーの完了を待たずに、同一タイミングで同一の処理の実行を開始する。

(もっと読む)

1 - 10 / 261

[ Back to top ]