国際特許分類[G06F12/06]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | ロケーションの物理的ブロックのアドレシング,例.ベース・アドレシング,モジュール・アドレシング,メモリ空間拡張,メモリ専用 (1,078)

国際特許分類[G06F12/06]に分類される特許

1 - 10 / 1,078

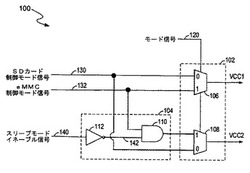

メモリデバイスに対する電力制御

【課題】余分のピンを使用すること、およびそれに関わる費用は、ある厳しい予算の環境下で、チップサイズおよび回路基板の大きさが決定的な要因である場合には、関心事項になる。

【解決手段】電力コントローラは、異なるタイプのメモリデバイスに異なるレベルの電力を供給するように構成される。電力コントローラは、メモリデバイスに供給する電力を制御する制御モードを選定する選定ユニットを含む。選定ユニットは、モード信号を受信するように構成された第1の入力と、いくつかの制御モード信号を受信するように構成された複数の制御入力と、メモリデバイスに電力を出力するように構成された複数の出力とを含む。選定ユニットは、受信したモード信号に従って制御モードを選定し、制御モード信号に従って電力を出力する。

(もっと読む)

半導体装置

【課題】データ用電流パスの占有面積を最小化し、かつ動作速度の低下も抑制する。

【解決手段】半導体装置10は、互いに積層されたインタフェースチップIF及び複数のコアチップと、インタフェースチップIFと複数のコアチップのそれぞれとを接続するデータ用電流パスとを備え、インタフェースチップIFは、複数のコアチップに対して同時にリードコマンドを供給するコマンドデコーダ32を有し、複数のコアチップはそれぞれ、メモリセルアレイ50と、当該コアチップに割り当てられた層アドレスLIDを記憶する層アドレス発生回路46と、リードコマンドに応じてメモリセルアレイ50からリードデータを読み出し、層アドレス発生回路46に記憶される層アドレスLIDに応じたタイミングで、上記データ用電流パスを介してインタフェースチップIFに出力するデータコントロール回路54とを有する。

(もっと読む)

電子機器及び固有情報の管理方法。

【課題】マイクロコントローラのフラッシュメモリに記憶されたプログラムにより電子機器本体を制御する電子機器において、製造コストの低下を図りかつ固有情報の書き換えを速やかに行う。

【解決手段】フラッシュメモリ5内の固有情報領域7に外部コンピュータ4から固有情報群を事前に書き込んでおく。固有情報群は例えばシンセサイザ回路部2に使用される標準のパラメータ群及び周波数シンセサイザ1の仮番号である。マイクロコントローラ3のRAM8には、固有情報領域7と同容量の読み出し領域81が割り当てられ、電源投入時に固有情報領域7から読み出し領域81に固有情報群が読み出される。外部コンピュータ4からの指示により当該固有情報群の一部を書き換え、その後固有情報領域7内の固有情報群を一括消去した後、読み出し領域81内の固有情報群を一括して固有情報領域7に書き込む。

(もっと読む)

デジタル信号処理用のメモリアクセス

【課題】デジタル信号処理システムにおけるメモリアクセスを提供する。

【解決手段】一例では、デジタル信号処理システムは、複数の単一ポートのメモリデバイスに接続されたメモリインタフェースから構成されたマルチポートのメモリを有する。メモリインタフェースは、プロセッサが単一アドレス空間を使用して単一ポートのメモリデバイスに格納されたデータにアクセスするために使用できるアクセスポートを提供する。プロセッサは、複数のアクセスポートに接続され、同時に複数の異なるメモリアドレスのデータへのアクセスを要求するためにこれらを使用してもよい。デジタル信号処理システムは、メモリインタフェースに接続された単一ポートのメモリデバイスの総数が3以上の素数になるように構成される。素数の数のメモリデバイスが使用されるため、異なるメモリアドレスのデータが同じ単一ポートのメモリデバイスにある可能性が最小化され、メモリアクセス速度を増加させる。

(もっと読む)

デュアルポートメモリおよびその方法

【課題】デュアルポートメモリを提供すること。

【解決手段】デュアルポートメモリは、第1のシングルポートメモリおよび第2のシングルポートメモリを含む。第1のシングルポートメモリは、デュアルポートメモリの偶数アドレス中のデータを記憶するように構成される。第2のシングルポートメモリは、デュアルポートメモリの奇数アドレス中のデータを記憶するように構成される。デュアルポートメモリは、奇数アドレスからデータを読み出す読出動作および偶数アドレスの中へデータを書き込む書込動作を同時に実行する。デュアルポートメモリは、偶数アドレスからデータを読み出す読出動作および奇数アドレスの中へデータを書き込む書込動作を同時に実行する。

(もっと読む)

バス接続回路、半導体装置及びバス接続回路の動作方法

【課題】直接転送をする場合と直接転送をしない場合とが混在しても、MEMC設定等の追加の動作を行うことなく、1サイクル転送することを可能とする。

【解決手段】バス接続回路は、バスマスタ10と複数のバススレーブ12、15とを接続する。バス接続回路は、ミラー領域アクセス検出回路13と、処理回路21、22、14とを具備する。ミラー領域アクセス検出回路13は、バスマスタ10が複数のバススレーブ12、15のうちの第1バススレーブ12のミラー領域へアクセスすることを検出して、検出信号35を出力する。処理回路21、22、14は、検出結果35に基づいて、当該検出結果35に対応して予め設定されている処理を、アクセスの対象としての領域又はデータに対して実行する。

(もっと読む)

情報処理システム、制御システム及び半導体装置

【課題】制御システムがメモリシステムのバンクグループにアクセスする際の効率を高めることが可能な情報処理システムを提供する。

【解決手段】本発明の情報処理システムは、例えば、メモリシステム20と、アクセス制御部15を含む制御システム13とを備えている。メモリシステム20は、記憶領域が複数のバンクにより構成され、この複数のバンクが複数のバンクグループにグループ化されている。アクセス制御部15は、複数のプロセシングエンジンによるアクセスの優先順位に対応し、バンクグループ毎にレイテンシを含むアクセス情報を第1のレジスタ15aに保持し、バスマスタ11aを介してプロセシングエンジンからのアクセス要求を受けたとき、第1のレジスタ15aを参照し、その内容に基づいてアクセス対象のバンクグループに対するアクセスをフレキシブルに制御する。

(もっと読む)

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

メモリ・デバイス

【課題】規格で定められていない仕様について、より高い性能を実現できるメモリ・デバイスを提供する。

【解決手段】メモリ・デバイスは、複数のセルからなる書き込み単位ごとにデータを書き込む不揮発性のメモリと、メモリを制御するコントローラを含む。コントローラは、メモリのメモリ空間を複数のパーティションに区切って管理し、ホスト・デバイスからの書き込みデータをメモリに書き込む要求に対して書き込みデータの分割された部分である書き込みデータ部分を送信することをそのサイズを指定してホスト・デバイスに要求することを定めた書き込み手順に従い、第1パーティションへのアクセスを要求する第1コマンドの処理の完了前に第2パーティションへのアクセスを要求する第2コマンドを受け付ける。書き込みデータ部分は該データ部分および付加的データの和のサイズが書き込み単位のサイズ以下で最大となるサイズの整数倍のサイズを有する。

(もっと読む)

マルチCPUコア・プロセッサ用DMAC付きDRAMアドレス・マッピング回路

【課題】CPUシステム(PC,TabletPC,PDA etc.)において、CPUコアもしくはOSが32bitであると主記憶サイズは4GB以下の3.5GB程度に制約される。 現状4GB(3.5GB)を超えて搭載したメモリーは無駄となる。 また、実行速度改善に効果がある現在のRAMDISKは主記憶を使う為、主記憶サイズの制限は、32bitシステムでの性能向上の足かせとなっている。

【解決手段】DRAMのローカル・アドレスをシステム物理アドレスにマッピングする回路にDMA機能を持たせる事により、主記憶に割り振れなかったDRAM領域をRAMDISKとして経済的に使用し、かつ、それに関わるデータ転送をDRAMのローカルバス上で局所的に行う事で、従来の主記憶を使ったRAMDISKより、実行効率の良いRAMDISKを供給する。

(もっと読む)

1 - 10 / 1,078

[ Back to top ]