国際特許分類[G06F12/16]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | メモリ内容の破壊に対する保護 (2,432)

国際特許分類[G06F12/16]に分類される特許

101 - 110 / 2,432

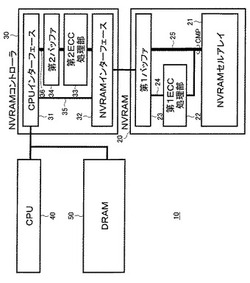

不揮発性メモリ、メモリコントローラ、不揮発性メモリのアクセス方法、およびプログラム

【課題】メモリセルとしてバイト単位のアクセスが可能であり、求められるアクセスに対して最適な単位でECC処理を行うことが可能な不揮発性メモリ、メモリコントローラ、不揮発性メモリのアクセス方法、およびプログラムを提供する。

【解決手段】ワード単位でアクセス可能で固定レイテンシでアクセス可能な第1アクセスモードと可変レイテンシでアクセス可能な第2アクセスモードによりアクセス可能な不揮発性メモリセルアレイを少なくとも含む不揮発性メモリセルデバイスと、第1アクセス経路に配置され、第1アクセスモード時にメモリセルアレイから出力されたデータに対してECCを適用した誤り検出処理および訂正処理を行う第1ECC処理部と、第2アクセス経路に配置され、第2アクセスモード時にメモリセルアレイから出力されたデータに対してECCを適用した誤り検出処理および訂正処理を行う第2ECC処理部とを有する。

(もっと読む)

記憶制御装置、及び、記憶制御方法

【課題】記憶媒体へのデータ転送速度を改善する技術を提供する。

【解決手段】RAIDコントローラ2(記憶制御装置)は、複数のSSD制御ユニット4(記憶媒体制御ユニット)と、論理ドライブ制御部5(ユニット統括部)と、を備えている。SSD制御ユニット4は、サイズ記憶部6(データブロックサイズ記憶部)とデバイスアクセス処理部7(入出力実行部)、最適アクセス方法評価部8(データブロックサイズ設定部)を有している。最適アクセス方法評価部8は、異なる複数のデータブロックサイズにてSSD3に対して入出力を実行すると共にその際のデータ転送速度を計測し、その計測結果に基づいてサイズ記憶部6のデータブロックサイズを設定する。

(もっと読む)

携帯可能電子装置、ICカード、及び携帯可能電子装置の制御方法

【課題】 より安定して動作する携帯可能電子装置、ICカード、及び携帯可能電子装置の制御方法を提供する。

【解決手段】 一実施形態に係る携帯可能電子装置は、データを記憶する第1のメモリと、復元アドレスと復元データとを対応付けてメモリ保障データとして記憶する第2のメモリと、外部機器から送信された書込みコマンドを受信する受信部と、前記書込みコマンドからアドレス及び書込みデータを取得し、前記アドレスと、前記書込みデータのデータサイズと、に基づいて前記第1のメモリ上の領域を特定し、特定された前記領域のデータを復元データとして前記第2のメモリに記憶し、前記アドレスを復元アドレスとして前記第2のメモリに記憶する制御部と、特定された前記第1のメモリ上の領域に前記書込みデータを書込む書込み処理部と、を具備する。

(もっと読む)

メモリコントローラ

【課題】フラッシュメモリに格納されるデータの信頼性を確保するとともに、構成を簡略化することができるメモリコントローラを提供することを課題とする。

【解決手段】メモリコントローラ3は、読み出しコマンドを受け付けた場合、通常アクセス領域41から格納データ50を読み出し、格納データ50のエラーを訂正する。格納データ50のエラーがECC回路34のエラー訂正能力の範囲内である場合、メモリコントローラ3は、エラー訂正された格納データ50に含まれる実体データを出力する。格納データ50のエラーがエラー訂正能力を超えている場合、メモリコントローラ3は、格納データ50のバックアップデータである格納データ70を、バックアップ領域42から読み出し、格納データ70に含まれる実体データを出力する。ホストコントローラ3は、格納データ70を用いて、通常アクセス領域41に格納された格納データ50を修復する。

(もっと読む)

マルチチャネルを有するメモリ装置及び同装置における誤り訂正チャネル決定を含む書き込み制御方法

【課題】誤り訂正チャネルを適用していながら、データ読み出しの並列度を向上できるようにする。

【解決手段】実施形態によれば、誤り訂正チャネル決定手段は、論理ブロックを構成する複数の論理ページがページ単位に複数のチャネルを介してメモリに書き込まれる際に、複数のチャネルのそれぞれに誤り訂正チャネルが割り当てられる論理ページの数が均等になるように、ページ単位に誤り訂正チャネルが割り当てられるチャネルを決定する。コマンドリスト生成手段は、誤り訂正チャネルが割り当てられるチャネルの決定に基づいて、複数のチャネルのうちの誤り訂正チャネルを除くチャネル群を介して、対応する論理ページを並列に書き込むためのライトコマンド群のリストを生成する。コマンドリスト投入手段は、ライトコマンド群のリストをメモリインタフェースに投入する。

(もっと読む)

情報処理端末及び管理サーバ

【課題】フラッシュメモリに書き込まれたデータの信頼性を向上することができる技術を提供することを課題とする。

【解決手段】メモリカード7Aは、コンテンツデータAを記録するメモリ71と、メモリコントローラ72とを備える。メモリコントローラ72は、メモリ71のエラーブロックのアドレスを記録したエラー発生データ75Aを作成する。エラー発生データ75Aは、情報処理端末4を介して、集計サーバ1に送信される。集計サーバ1は、複数の情報処理端末から受信したエラー発生データ75Aを集計して、メモリ71において検査対象となる検査領域を設定し、検査領域が記録された個別検査領域データ16Aを作成する。情報処理端末4は、個別検査領域データ16Aを集計サーバ1から取得して、メモリコントローラ72に出力する。メモリコントローラ72は、個別検査領域データ16Aに基づいて、メモリ71で検査する領域を決定する。

(もっと読む)

電子機器

【課題】フラッシュROMに対し、効率的にデータを書込可能な技術を提供する。

【解決手段】電子制御装置のMPUは、フラッシュROM13への書込対象データを、1バイト単位のデータ(バイトデータ)に分割し(S130)、この書込対象データを構成するバイトデータの夫々を、順に処理対象データに選択する(S140)。そして、処理対象データと、フラッシュROMが記憶する当該処理対象データに対応するバイトデータとを比較し(S150)、処理対象データが、フラッシュROMが記憶するものから内容変更されたものである場合には(S150でYes)、これをフラッシュROMに追記する形式で書き込む(S160)。一方、処理対象データがフラッシュROMが記憶するものから内容変更されたものでなければ(S150でNo)、この処理対象データのフラッシュROMへの書込については行わないようにする。

(もっと読む)

電子機器

【課題】不揮発性メモリにおける記憶ブロック間のデータ消去回数のばらつきを抑える。

【解決手段】電子制御装置は、フラッシュROMを備える。フラッシュROMは、複数の記憶ブロックを備え、記憶ブロック単位でのデータ消去が可能な周知のメモリである。電子制御装置のMPUは、フラッシュROMの記憶ブロック群を、書込頻度が低いデータ記憶用の低頻度ブロック群と、書込頻度が高いデータ記憶用の高頻度ブロック群とにグループ化する。そして、高頻度ブロックのデータ消去回数に基づき、データ消去回数が100の倍数となる度、低頻度ブロックを、記憶ブロック一つ分ずらすようにして、高頻度ブロックと入れ替える。この動作によって、フラッシュROM内の記憶ブロック群を再グループ化する。一般的に高頻度ブロックのデータ消去回数のほうが低頻度ブロックよりも多くなるが、再グループ化により記憶ブロック間のデータ消去回数のばらつきは抑えられる。

(もっと読む)

メモリコントローラ、半導体メモリ装置、および復号方法

【課題】、実装メモリ容量が小さく回路規模の小さいメモリコントローラ3を提供する

【解決手段】メモリコントローラ3は、LDPC符号により符号化されたフレーム単位のデータを、単位行列からなるブロックと、単位行列の各行が順にシフトしている複数のブロックと、からなる検査行列をもとに、部分並列処理により復号を行い、メモリ部5から読み出したデータの閾値判定情報を記憶するバッファ24と、閾値判定情報をLLRに変換するLLR変換部16と、ブロックのサイズ以下のイタレーション単位で、LLRをもとに、列処理および行処理を繰り返し行うイタレーション処理のときに算出される確率情報βを、記憶するLMEM12と、イタレーション単位のイタレーション処理が完了する度に、LMEM12に記憶される確率情報βを、バッファ24に転送するCPUコア10と、を具備する。

(もっと読む)

コンピュータ、その制御方法及びプログラム

【課題】MBRとバックアップセクタデータを検証し、正常にリードできない又は不正であるときに、自動的に復旧し起動処理を実行する。

【解決手段】シャットダウンを検知した場合に、MBRとバックアップMBRのリードを行い、MBRのデータとバックアップMBRのデータとが同一でないときにMBRをバックアップMBRにコピーするか、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーするかする。コンピュータの電源をオンした場合に、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーする。

(もっと読む)

101 - 110 / 2,432

[ Back to top ]