国際特許分類[G06F12/16]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | メモリ内容の破壊に対する保護 (2,432)

国際特許分類[G06F12/16]に分類される特許

71 - 80 / 2,432

プラグインカード収容装置

【課題】エラー訂正回路の動作に起因して発生する消費電力の低減を図る。

【解決手段】プラグインカード収容装置は、受信した入力データを格納するメモリと、前記メモリに電気的に接続可能に設けられ、前記メモリから出力された前記入力データのエラーを訂正するエラー訂正回路とを含むプラグインカードと、前記プラグインカードが実装される装置本体と、前記装置本体に実装された前記プラグインカードに備えられる前記メモリのエラー率に基づいて前記プラグインカードの信頼性指標値を算出し、算出した前記信頼性指標値が基準値に近づくように、前記エラー訂正回路を前記メモリに電気的に接続するかどうかを決定するプロセッサとを有する。

(もっと読む)

診断装置、診断方法および診断プログラム診断方法

【課題】コンピュータシステムのメモリ部の障害の被疑部位を高速かつ正確に特定する診断装置を提供する。

【解決手段】コンピュータシステム100のメモリ部3にアクセスしてエラーが発生した際に、診断装置10は、エラー発生時のメモリ読み出しアドレスおよびメモリ読み出しデータのエラービットをそれぞれ読み出しアドレス保持回路15およびエラービット保持回路12に保持し、診断読み出しアドレス生成回路16および診断読み出しコマンド生成回路14からメモリ読み出し制御部2に指示してエラー発生時の同一メモリ読み出しアドレスに再度アクセスするリトライ動作を実施させ、リトライ結果として、エラービット比較回路13において再度同一のエラービットが発生するか否かの比較結果131に基づいて、診断制御回路17は、固定障害か否かを判別し、固定障害と判別した場合エラーが発生した部位を中心に切り分けテストを行い、障害被疑部位を特定する。

(もっと読む)

ICチップ、ICチップにおける処理方法、及びICチップ用処理プログラム

【課題】処理中断によりトランザクションが行われた場合であっても、処理時間制約が厳しい方のインターフェイスを用いた処理を正常に行うことが可能なICチップ、ICチップにおける処理方法、及びICチップ用処理プログラムを提供する。

【解決手段】ICチップは複数のインターフェイスに対応した処理手段と、データを記憶するデータ記憶領域と前記データをバックアップするためのバックアップ領域と、を有する不揮発性メモリと、第1の前記インターフェイスを用いた処理により受信されたデータを前記データ記憶領域に書き込む際に前記データ記憶領域に記憶されているデータを前記バックアップ領域にバックアップし、前記第1の前記インターフェイスを用いた処理が中断された場合には、前記バックアップ領域にバックアップされている前記データを前記記憶領域に書き戻す処理を行う制御手段と、を備える。

(もっと読む)

情報更生装置、メモリ制御システム、情報更生方法およびコンピュータプログラム

【課題】 記憶容量が不足する事態を抑制しながら、メモリにおける情報保持性能の信頼性を高める。

【解決手段】 更生部2を備える。当該更生部2は、メモリから読み出された情報に含まれるビット誤りの数を誤りビット数として前記メモリにおける予め定められたメモリ領域毎に計数する機能を備えている。また、更生部2は、その誤りビット数が予め定められた閾値以上である前記メモリ領域には、当該メモリ領域とは別のメモリ領域に事前に書き込まれていたバックアップ情報を上書きする機能を備えている。

(もっと読む)

半導体集積回路、半導体装置およびリモートコントローラ

【課題】マイクロコンピュータがストップ状態であり、キャパシタによって電源電圧がマイクロコンピュータに供給されている場合、マイクロコンピュータのストップ状態を維持する。

【解決手段】検出回路(3)は、外部キャパシタ(C1)を放電させる外部キャパシタ放電回路(30A)と、電源電圧を保持する内部キャパシタ(C2)と、内部キャパシタを放電させる内部キャパシタ放電回路(30)と、比較器(32)と、出力回路(33)とを有する。比較器は、放電後の外部キャパシタの第1電圧(VC1)を、放電後の内部キャパシタの第2電圧(VC2)と比較する。比較の結果、出力回路は、第1電圧が第2電圧よりも低い場合、マイクロコンピュータが外部キャパシタから電源電圧の供給を受けていることを示す検出信号(S2)を出力する。割り込み回路(4)は、その検出信号を受けた場合、割り込み信号(SI)を出力しない。

(もっと読む)

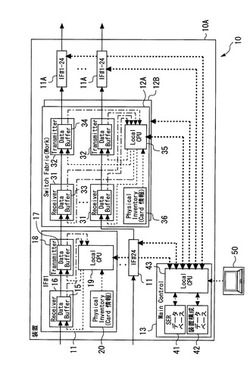

メモリ制御装置

【課題】H/Wの無駄が生じることがなく、高速に処理可能なメモリ制御装置を実現する。

【解決手段】メモリ制御装置1000は、ペイロードをペイロード領域に格納し、パリティデータをパリティ領域に格納する実メモリ004を制御する。ペイロード/パリティ領域アドレス計算部001は、ペイロードとパリティデータのビット数の比をペイロード/パリティ比104として入力し、実メモリ004の領域をペイロード/パリティ比に近似させてペイロード領域とパリティ領域とに分類した結果ペイロード領域に分類される領域の数を分割比103として入力し、実メモリ004のメモリアドレス長102を入力し、ペイロードのメモリアドレス101を入力し、これらを用いて、当該ペイロードに対応するパリティデータのパリティ領域でのメモリアドレスを算出する。

(もっと読む)

フラッシュメモリの制御装置

【課題】フラッシュメモリの寿命を延ばすことができる、フラッシュメモリの制御装置を提供する。

【解決手段】フラッシュメモリの複数のブロックを、低頻度データブロックと高頻度データブロックに分ける。低頻度データブロックには、更新頻度の低いデータとして予め設定された低頻度データを記憶する。一方、高頻度データブロックには、更新頻度の高いデータとして予め設定された高頻度データを記憶する。そして、フラッシュメモリに新たに記憶させるデータの種類が低頻度データであれば低頻度データブロックに記憶させ、高頻度データであれば高頻度データブロックに記憶させる。

(もっと読む)

半導体装置

【課題】データの誤書換を防止することが可能な低消費電力の半導体装置を提供する。

【解決手段】マイクロコンピュータ1は、電源電圧VCCが正常範囲から外れた場合にリセット信号REを出力する電圧検出器2と、各々がデータを不揮発的に記憶する複数のメモリセルを含むメモリアレイ5と、イレーズコマンドまたはプログラムコマンドに応答して、電圧検出器2の応答時間TR以上の保留時間TSだけ経過した後にデータのイレーズまたはプログラムを実行し、リセット信号REに応答してリセットされる制御部7とを備える。したがって、電圧検出器2の応答時間TRが長い場合でも、データの誤書換を防止できる。

(もっと読む)

メモリコントローラ、半導体記憶装置および復号方法

【課題】複雑な処理を行わずに回路規模を低減することができるメモリコントローラを得ること。

【解決手段】メモリコントローラであって、メモリ部へ書き込むデータとデータに対する誤り検出符号とデータおよび誤り検出符号に対するt(tは2以上の整数)シンボル訂正可能な誤り訂正符号とをn個のチャネルごとにメモリ部へ書き込み、データと誤り検出符号と誤り訂正符号とを読み出しデータとしてチャネルごとにメモリ部から読み出すメモリインタフェースと、チャネルごとの読み出しデータに対してs(s<t)シンボル訂正可能な第1の誤り訂正復号化処理を実施するn個の第1の誤り訂正復号化部と、第1の誤り訂正復号化処理の復号結果に基づいてチャネルごとに誤り検出処理を行うn個の誤り検出部と、誤りが検出されたチャネルの読み出しデータに対してtシンボル訂正可能な誤り訂正復号化処理を実施する第2の誤り訂正復号化部と、を備える。

(もっと読む)

情報処理装置および方法、並びにプログラム

【課題】より効率的に処理を実行できるようにする。

【解決手段】制御部は、データをnビット単位でアクセスし、記憶部は、mビット単位の管理データを複数個組み合わせてnビットになるように、管理データを記憶し、変換部は、制御部が管理データにアクセスする場合、mビット単位の管理データをnビット単位の管理データに仮想的に変換する。

(もっと読む)

71 - 80 / 2,432

[ Back to top ]