国際特許分類[G06F12/16]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | メモリ内容の破壊に対する保護 (2,432)

国際特許分類[G06F12/16]に分類される特許

41 - 50 / 2,432

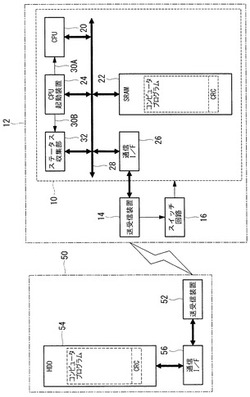

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

プログラム、情報処理システム、情報処理装置、および情報処理方法

【課題】他のデータに対するアクセスにより生じるエラーから特定のデータを保護できるプログラム、情報処理システム、情報処理装置、および情報処理方法を提供する。

【解決手段】例示的な実施の形態は、コンピュータで実行される、1つのメモリセルに複数ビットを記憶可能な半導体記憶手段に対してデータを書き込むためのプログラムを提供する。プログラムは、コンピュータに、第1のデータを記憶するための第1の領域を半導体記憶手段の記憶領域内に割り当てる割当ステップと、第1のデータの書込要求に応答して、第1の領域の境界から所定のサイズを保護領域とし、残りの領域を使用領域として、第1のデータを使用領域のみに書き込む書込ステップとを実行させる。

(もっと読む)

記憶装置

【課題】データページの読み込み時間の短縮を可能にするメモリシステムを提供する。

【解決手段】記憶装置は、所定の数のビットからなるデータページ102を複数有する不揮発性メモリ100と、ビットの状態出力を要求するコントローラ110とを有し、不揮発性メモリ100は、ビットの状態出力の要求を受けた際に、ビットの論理値を検査する論理回路103を有し、ビットが全て書き込み可または書き込み不可を示す論理値をコントローラに出力する。

(もっと読む)

情報処理装置及び記憶部検査方法

【課題】CPUの運用中においても、記憶部の検査のためにCPUによるソフトウェアのデータ処理を一時停止させることがなく、記憶部の異常の有無をチェックすることができる情報処理装置及び記憶部検査方法を提供する。

【解決手段】CPU1とは独立に設置された記憶制御部2は、CPU1から書き込みようの処理データと書き込み先の記憶部3の指定アドレスを受け、検査用データを指定アドレスに書き込み、それを読み出す。記憶制御部2が備えるデータチェック部20は、検査用データと読み出されたデータとを比較し、一致するかどうかを判定する。一致しなければ指定アドレスに異常があると判定し、その旨をCPU1に通知し、一致すれば、記憶制御部は処理データを指定アドレスに書き込む。

(もっと読む)

半導体記憶装置

【課題】

実施形態は、解析が簡便な半導体記憶装置を提供する。

【解決手段】

本実施形態の半導体記憶装置は、メモリ部(100)と、前記メモリ部(100)に接

続されるコントローラ部(200)と、前記コントローラ部(200)に接続される第1

入出力部(300)と、前記メモリ部(100)と前記コントローラ部(200)の間の

ノードに電気的に接続され、前記第1入出力部(300)とは異なる第2入出力部(40

0)とを備える。

(もっと読む)

コントローラおよびメモリシステム

【課題】データの消失を効率よく予防すること。

【解決手段】本発明の一つの実施形態によれば、コントローラは、読み出し検査実行部と、検査ブロック設定部と、タイミング決定部とを備えている。読み出し検査実行部は、不揮発性メモリが備える複数のブロックのうちの有効データが格納されているブロックの読み出し検査を実行する。検査ブロック設定部は、不揮発性メモリが備える複数のブロックのうちから少なくとも1つに出来るだけ高い閾値を有する検査パターンデータを書き込んで検査ブロックを設定する。ここで、タイミング決定部は、検査ブロックに書き込まれた検査パターンデータに発生するビット反転数に基づいて読み出し検査実行部による読み出し検査のタイミングを決定する。

(もっと読む)

メモリデバイス

【課題】高品質なメモリデバイスを提供する。

【解決手段】メモリデバイスは、不揮発性のメモリ11と、コマンド格納部と、記憶部46と、管理部と、を備えている。コマンド格納部は、コマンドを格納する。記憶部46は、バックグランド処理の種類とその優先順位とが設定され、必要とされているバックグランド処理の情報が設定され、ホストデバイス2によって、バックグランド処理の許可または不許可が設定される。管理部は、コマンド格納部にコマンドが格納されていないと判定すると、記憶部46を参照してホストデバイス2がバックグランド処理を行うことを許可しているか否かを判定し、許可されていない場合、記憶部46に設定されたバックグランド処理の情報と優先順位とを参照して、メモリ11の未使用のブロックの数と、必要とされているバックグランド処理の優先順位及び数とに基づいてバックグランド処理の重要度を記憶部46に設定する。

(もっと読む)

メモリシステム

【課題】不良メモリチップが発生した場合でも、並列駆動可能な組み合わせ数を最大限確保可能なメモリシステムを提供すること。

【解決手段】物理バンク内の不良メモリチップが識別可能な不良メモリチップ情報に基づき、不良メモリチップを使用せずに各レーン内において並列アクセス可能なメモリチップ数が最大となるように、論理バンクを構成する複数の物理バンクの組み合わせを動的に設定する。

(もっと読む)

メモリシステムとその制御方法

【課題】 データを確実且つ高速に書き込むことが可能なメモリシステムとその制御方法を提供する。

【解決手段】 メモリシステムは、第1、第2のディストリクト31a、31bと、制御部21を含んでいる。第1、第2のディストリクト31a、31bは、それぞれメモリセルアレイ32を有する。制御部21は、第1、第2のディストリクト31a、31bへ同時に第1のデータを書き込むための書き込みコマンド及びアドレスを受け、第1、第2のディストリクト31a、31bに同時に第1のデータを書き込む。

(もっと読む)

メモリコントローラ

【課題】半導体メモリを効率的に利用可能なメモリコントローラを提供すること。

【解決手段】実施形態のメモリコントローラ20は、第1インターフェイス21と、第2インターフェイス23と、制御部24とを備える。第1インターフェイス21は、ホスト10との間で信号を送受信する。第2インターフェイス23は、不揮発性の半導体メモリ30との間で信号を送受信する。制御部24は、第1インターフェイス21で受信した第1コマンドに応答して半導体メモリ30に予備領域を確保し、半導体メモリ30に保持されるデータの更新時には予備領域に更新データを書き込む。予備領域のサイズは、第1コマンドに応じて可変である。

(もっと読む)

41 - 50 / 2,432

[ Back to top ]