国際特許分類[G06F7/38]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915) | 位取り記数法を用いて計算を行なうための方法または装置,例.2進,3進,10進法を用いるもの (331)

国際特許分類[G06F7/38]の下位に属する分類

接点開閉素子,例.電磁継電器,を用いるもの (1)

電気機械的計数器型の累算器を用いるもの

無接点素子,例.真空管,固体素子,を用いるもの;素子を特定しないで用いるもの (289)

国際特許分類[G06F7/38]に分類される特許

11 - 20 / 41

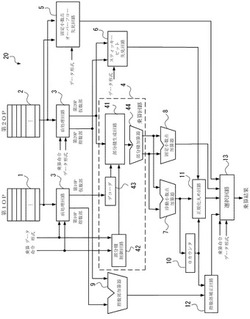

ベクトル乗算処理装置および方法ならびにプログラム

【課題】オペランドのシフトを要することなく消費電力の削減をはかる。

【解決手段】高速化回路(固定小数点オーバーフロー先見回路5、スティッキービット先見回路6)を備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、高速化回路を使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路4(部分積生成回路41、部分積制御回路42)、を備える。

(もっと読む)

エラー検出機能付き演算回路、および演算回路のエラー検出方法

【課題】ソフトエラーに基づく演算結果の誤りを確実に検出する。

【解決手段】エラー検出機能付き演算回路は、グレイコード形式の第1の数値を保持するレジスタと、前記レジスタに保持された前記第1の数値から、該第1の数値に対する所定の数値演算の結果である第2の数値をグレイコード形式で求めて出力する数値演算手段と、前記レジスタに保持された前記第1の数値に対するパリティ値である第1のパリティ値を使用して、前記数値演算に対応する所定の論理演算を行うことにより、前記第2の値に対するパリティ値である第2のパリティ値を生成するパリティ演算手段と、前記パリティ演算手段により生成された前記第2のパリティ値を使用して、前記数値演算手段により出力された前記第2の数値に対するパリティチェックを行うパリティチェック手段と、を有する。

(もっと読む)

演算装置、演算方法及び演算プログラム

【課題】浮動小数点演算でアンダーフロー例外及びオーバーフロー例外が発生した場合に消費電力を抑えることができる演算装置を提供する。

【解決手段】指数演算手段81は、浮動小数点数の指数に対して演算を行う。仮数演算手段82は、浮動小数点数の仮数に対して演算を行う。演算例外検知手段83は、指数演算手段81が演算を実行したときに、その演算結果がオーバーフロー又はアンダーフローを示す演算例外であることを検知する。演算停止手段84は、演算例外検知手段83が演算例外を検知したときに、仮数演算手段82の演算を停止させる。

(もっと読む)

デジタル・シグナル・プロセッサの演算論理装置

本発明は、デジタル・シグナル・プロッサ(DSP)、特に、オーディオ信号処理のためのDSPの演算論理装置(ALU)に関し、入力として第1の信号及び第2の信号を受信し、第1の信号及び第2の信号の乗算結果である第3の信号を出力として供給できる乗算回路と、ディザ信号の生成回路と、乗算回路の下流に配置され、第4の信号を出力に供給するために第3の信号Mとディザ信号の加算を実行できる加算回路と、加算回路の下流に配置され、第4の信号の切捨て又は丸めを実行できる切捨て又は丸め回路と、を備えている。  (もっと読む)

(もっと読む)

信号処理プロセッサ及び半導体装置

【課題】複数のデータ語長への飽和処理を効率良く行える信号処理プロセッサ及び半導体装置を提供すること。

【解決手段】デコード部110とレジスタ部と命令実行部130とを含む信号処理プロセッサ100であって、命令実行部130は、読み出し処理部140と、演算部150と、飽和処理部160と、書き出し処理部170と、を含みレジスタ部は、飽和処理において飽和させる語長を特定する飽和語長調情報124を含む飽和情報が保持された飽和情報保持部120を含み、飽和処理部160は、飽和語長情報124によって特定される語長に対応した飽和処理を行う。

(もっと読む)

プロセッサ

【課題】固定小数点演算において小数点位置を変更可能にすることで、プログラムで処理すべき値を正規化する作業を省く。

【解決手段】四則演算とシフト演算の少なくとも一方を行う算術論理演算ユニット13と、固定小数点演算の小数点位置データを保持する小数点位置レジスタ14と、小数点位置レジスタ14に保持される小数点位置データに基づいて、算術論理演算ユニット13の出力に対して所定の丸め及び飽和処理を行う丸め/飽和処理器20とを有する。

(もっと読む)

演算回路及び演算方法並びに情報処理装置

【課題】より少ない回路量で数値的に大きな誤差をもつエラーを効率的に検出する浮動小数点演算回路を提供する。

【解決手段】上記課題を解決するために、浮動小数点演算回路に、第1の演算結果を出力する第1の演算器101と、第2の演算結果を出力する第2の演算器102と、第1の演算結果と第2の演算結果とについて所定ビット幅の比較を行う比較回路103と、を備える。

(もっと読む)

3項入力の浮動小数点加減算器

【課題】演算過程で無限の精度をもって演算した後丸めを行った場合と同一の結果を得ることができる3項入力の浮動小数点加減算器を提供する。

【解決手段】入力される3項の指数の大きさが最大の仮数、中間の仮数、最小の仮数に振り分け、指数の大きさが中間の仮数と最小の仮数とをそれぞれ2n+3ビット幅で右シフトして桁合わせを行った仮数と最大の仮数とを出力する前処理回路100と、前処理回路100からの3項の仮数を2項に減らす桁上げ保存加算器(CSA)101と、2項になった仮数の加算を行う桁上げ先見加算器(CLA)102と、最上位ビットが1になるように左シフトする正規化回路103と、上位からn+3ビット目を新たなStickyビットとし、それより下位のビットとの論理和を取って丸めを行う丸め処理回路104と、最終的な指数を出力する指数演算器100とを備える。

(もっと読む)

演算装置

【課題】演算途中の結果が汎用レジスタのビット幅を超えるような演算においても、チップに対する占有面積の増加を抑えて、高精度の演算が可能な演算装置を提供する。

【解決手段】複数の汎用レジスタ12は、第1のビット幅を有している。演算器13は、第1、第2の入力端を有し、少なくとも第1の入力端が第1のビット幅より広い第2のビット幅を有し、汎用レジスタ12から第1、第2の入力端に供給されるデータを演算する。第1のビット幅より狭いビット幅を有する第1、第2のレジスタov0、ov1は、演算器13による演算の結果、あふれた桁のデータをオーバーフローデータとして保持し、演算器13の少なくとも一方の入力端に、上位ビットとして保持したオーバーフローデータを供給する。

(もっと読む)

命令に応じた丸め処理の実行

ある実施形態では、本発明は、プロセッサにおいて丸め命令および直接値を受領し、前記直接値の丸めモード・オーバーライド指標がアクティブであるかどうかを判定し、もしアクティブであれば、前記丸め命令に応答して、前記直接オペランドに記述されている丸めモードに従って前記プロセッサの浮動小数点ユニットにおいてソース・オペランドに対して丸め処理を実行することを含む方法を含む。他の実施形態も記載され、特許請求される。  (もっと読む)

(もっと読む)

11 - 20 / 41

[ Back to top ]