国際特許分類[G11C11/4097]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 特定の電気的または磁気的記憶素子の使用によって特徴づけられたデジタル記憶装置;そのための記憶素子 (6,432) | 電気的素子を用いるもの (5,515) | 半導体装置を用いるもの (5,114) | トランジスタを用いるもの (5,110) | リフレッシングまたは電荷再生,すなわちダイナミック・セル (3,594) | 周辺回路,例.アドレス用,デコード用,駆動用,書込み用,検出用,または同期用 (1,832) | 電界効果型のメモリ・セル用の周辺回路,例.アドレシング,復号化,駆動,書込み,検知または同期用 (1,832) | 読出し−書込み回路 (638) | ビット・ライン構成,例.ビット・ライン配置,折り返しビット・ライン (38)

国際特許分類[G11C11/4097]に分類される特許

1 - 10 / 38

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体装置

【課題】ダミーマットの占有面積を縮小する。

【解決手段】半導体装置は、ビット線32と、ビット線に接続された複数のメモリセル31と、ダミービット線52と、ダミービット線にソース及びドレインの一方が接続された複数のダミーセルトランジスタ51と、ビット線とダミービット線との間に接続されたセンスアンプ33とを有し、複数のダミーセルトランジスタの各々のソース及びドレインの他方は、フローティング状態にされるか、又はダミービット線に接続されている。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

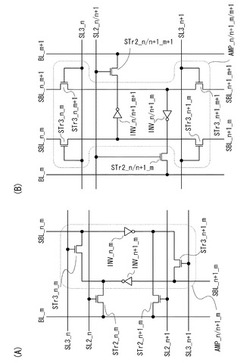

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

半導体装置及びその制御方法並びにその情報処理システム

【課題】階層化ビット線構成を有するメモリセルアレイにおいてプリチャージ回路を削減しつつ冗長判定に伴うアクセス速度の低下を防止し得る半導体装置を提供する。

【解決手段】階層化ビット線構成の通常領域であるメモリ領域SM(0)及び冗長領域を含むメモリ領域SM(m)を有する。スタンバイ時にはグローバルビット線GBL及びメモリ領域SM(m)のローカルビット線LBLをプリチャージし、メモリ領域SM(0)のローカルビット線LBLはプリチャージしない。例えば、メモリ領域SM(0)のアクティブ動作時には直ちにメモリ領域SM(0)のローカルビット線LBLをプリチャージし、その後の冗長判定結果に応じて各メモリ領域SM(0)、SM(m)の階層スイッチSWをそれぞれ維持または非活性状態に制御して通常メモリセルMC又は冗長メモリセルRCをアクセスする。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなった。

【解決手段】1つの主ビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと2乃至32個のメモリセル(MC_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr_n_mと読み出しトランジスタRTr_n_mを有し、読み出しトランジスタRTr_n_mのゲートにはサブビット線SBL_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷情報を読み出しトランジスタRTr_n_mでエラーなく増幅でき、主ビット線MBL_mに出力できる。

(もっと読む)

半導体装置及びその制御方法

【課題】ビット線構成が階層化されたメモリセルアレイのプリチャージ動作時に配線レイアウトに起因するプリチャージ速度の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ローカルビット線LBLとグローバルビット線GBLとに階層化され、階層スイッチLSWによりローカルビット線LBLとグローバルビット線GBLとの間の電気的接続が制御され、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。プリチャージ動作時には、階層スイッチLSWが導通している状態で、グローバルビット線GBLの側のプリチャージ回路(不図示)によりプリチャージ電圧がグローバルビット線GBLに供給される。所定時間が経過してローカルビット線LBLの電位がプリチャージ電圧に収束すると、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。

(もっと読む)

1 - 10 / 38

[ Back to top ]