国際特許分類[G11C16/04]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 消去可能でプログラム可能なリードオンリメモリ (6,621) | 電気的にプログラム可能なもの (6,621) | 閾値が可変なトランジスタを用いるもの,例.FAMOS (1,754)

国際特許分類[G11C16/04]に分類される特許

1 - 10 / 1,754

不揮発性半導体メモリおよびそのデータの読出し方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

暗号化演算装置を搭載する不揮発性半導体記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

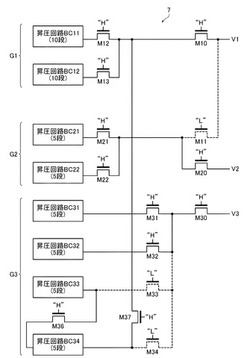

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の回路面積を削減する。

【解決手段】半導体記憶装置10は、複数のメモリセルを有する第1のブロックを含むメモリセルアレイ11−1と、複数のメモリセルを有する第2のブロックを含むメモリセルアレイ11−2と、メモリセルアレイ11−1及び11−2に配設された複数のワード線と、複数のワード線のそれぞれに電圧を転送する複数の転送ゲートSWを有するロウデコーダ12とを含む。第1のブロックに配設された複数のワード線は、第1及び第2のグループを有し、第2のブロックに配設された複数のワード線は、第3及び第4のグループを有する。上記第1及び第3のグループは、転送ゲートSWを共有する。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

不揮発性メモリーセル

【課題】種々の回路ブロックを単一の集積回路(IC)に集約するために、不揮発性メモリーブロックをロジック機能ブロックにまとめる。

【解決手段】結合素子と第一のセレクトトランジスターを有している。結合素子は第一の伝導領域において形成されている。第一のセレクトトランジスターは、第一の浮遊ゲートトランジスターおよび第二のセレクトトランジスターに直列的に接続されており、それらは全て第二の伝導領域に形成されている。結合素子の電極および第一の浮遊ゲートトランジスターのゲートは、モノリシックに形成された浮遊ゲートである。第二の伝導領域は第一の伝導領域と第三の伝導領域の間に形成され、第一の伝導領域、第二の伝導領域、および第三の伝導領域は、ウェルである。

(もっと読む)

半導体記憶装置

【課題】動作の安定性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、複数のメモリセルと、複数のワード線と、複数のビット線と、複数の選択トランジスタと、配線層と、を備える。複数のメモリセルは、第1方向及び第1方向と直交する第2方向にそれぞれ配置される。複数のワード線は、それぞれ第1方向に延在して設けられる。複数のビット線は、それぞれ第2方向に延在し、第1方向及び第2方向と直交する第3方向に複数のワード線と離間して設けられる。複数の選択トランジスタは、複数のストリングにそれぞれ設けられる。配線層は、選択トランジスタのソースと同電位に設けられる。配線層は、第3方向にみて複数のワード線とそれぞれ重なる複数の第1重複部分を有する。配線層のパターンが繰り返される単位領域において、複数の第1重複部分のそれぞれの面積は同じである。

(もっと読む)

1 - 10 / 1,754

[ Back to top ]