国際特許分類[G11C17/06]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 一度だけプログラム可能なリードオンリメモリ;半永久的記憶装置,例.手でリプレースできる情報カード (379) | ダイオード素子を用いるもの (43)

国際特許分類[G11C17/06]に分類される特許

1 - 10 / 43

OTPメモリ

【課題】より秘匿性の高いOTPメモリを提供する。

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルごとの消去回数を低減することで、フラッシュメモリの寿命を延ばす。

【解決手段】不揮発性半導体記憶装置3は、複数の半導体領域202の各々に設けられ、かつ直列に接続されたメモリトランジスタ及び選択トランジスタを有する複数の不揮発性メモリセルがマトリクス状に配置されたメモリセルブロックと、同一行にあるメモリトランジスタを共通接続するようにして、複数のメモリトランジスタのコントロールゲートに接続された複数のワード線WLと、同一行にある選択トランジスタを共通接続するようにして、複数の選択トランジスタのゲートに接続された複数の選択ゲート線SGとを含む。ロウデコーダ20は、消去動作時に、半導体領域に消去電圧を印加した状態で、データが消去される選択ワード線に負の第1の電圧を印加し、データが消去されない非選択ワード線に正の第2の電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置及びその駆動方法

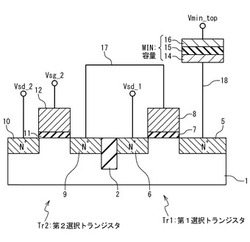

【課題】セルの配置効率が高く且つ読み出し時の消費電流が少なく、さらにはデータを高速に読み出すことができるようにする。

【解決手段】ゲートが列方向に延伸する第1の選択ワード線23と接続され、ソースが第1の副ビット線20と接続され、ドレインが行方向に延伸する第1の主ビット線22と接続された第1の選択トランジスタ21と、ゲートが列方向に延伸する第2の選択ワード線33と接続され、ソースが第2の副ビット線30と接続され、ドレインが行方向に延伸する第2の主ビット線32と接続された第2の選択トランジスタ31とを有している。ここで、第2の選択トランジスタ31の耐圧は、第1の選択トランジスタ21の耐圧よりも低い。

(もっと読む)

半導体装置及びその駆動方法

【課題】現行プロセスを用いて追加工程なしに製造でき、高い信頼性を有する多値化された電気ヒューズを有する半導体装置を提供する。

【解決手段】第1フィラメントFS1と、第1フィラメントFS1に接続された第2フィラメントFS2とを有する電気ヒューズ素子を有し、第1フィラメントFS1の第2フィラメントFS2との接続端と反対の端部に接続された第1フィラメントFS1と第2フィラメントFS2の直列抵抗を読み出す直列読み出し部RDSとを有する構成とする。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

メモリ

【課題】消費電流(消費電力)が増加するのを抑制することが可能なメモリを提供する。

【解決手段】このメモリ(クロスポイント型のダイオードROM)では、半導体基板の表面に形成された不純物領域22は、メモリセルにおけるダイオードのカソードとして機能するセル領域22bと、コンタクト領域24が形成される配線接続領域22aとを含み、不純物領域22のうちの配線接続領域22aの近傍(抵抗領域22c)の抵抗は、セル領域22bの抵抗よりも大きい。

(もっと読む)

半導体装置

【課題】内部回路の動作パラメータなどの設定を行うデータを長期にわたって安定に供給する。

【解決手段】第1の動作モード(PROM)時には、不揮発性メモリセルに対し非破壊的に書換え可能な態様でデータを書込み、第2の動作モード(OTP)時には不揮発性メモリセルに対し、破壊的に書換え不可能な態様でデータを書込む。この不揮発性メモリセルは、記憶素子として、可変磁気抵抗素子を有し、可変磁気抵抗素子の抵抗値に応じて情報を不揮発的に記憶する。

(もっと読む)

メモリ

【課題】スタンバイ時に導電層からダイオードを介してビット線に電流がリークするのを抑制することが可能なメモリを提供する。

【解決手段】このクロスポイント型のダイオードROM(メモリ)は、複数のワード線WLに交差するように配置される複数のビット線BLと、ワード線WLに沿って延びるように設けられる導電層2cと、導電層2cとビット線BLとが交差する位置に配置され、導電層2cにカソードが接続されるダイオード3を含むメモリセル4と、メモリセル4に記憶されるデータが読み出されるソース線S0(S1〜S3)とを備え、スタンバイ時に導電層2cまたはビット線BLの一方がフローティング状態になるように構成されている。

(もっと読む)

半導体記憶装置の駆動方法

【課題】製造以外でも情報の書込みが可能なアンチヒューズ型の半導体記憶装置を提供することを目的の1つとする。また、半導体記憶装置の小型化及び大容量化を図ることを目的の1つとする。

【解決手段】半導体記憶装置は、メモリセルがマトリクス状に配置されたメモリセルアレイを有し、ビット線駆動回路とワード線駆動回路から構成されている。m×n個のメモリセル103(MC(1,1)〜M(m,n))がマトリクス状に配置されたメモリセルの例において、メモリセルはビット線とワード線の交差部に設けられている。ビット線駆動回路と101ワード線駆動回路102をより少ない部品点数で構成することにより記憶装置の小型化と大容量化につながる。ビット線駆動回路とワード線駆動回路の部品点数が少なくてすむ記憶装置の駆動方法を提供する。

(もっと読む)

不揮発性でプログラム可能なメモリセルおよびメモリアレイ

不揮発性1回限りプログラム可能メモリセルは、2端子ヒューズおよび3端子アンチヒューズを、直列に結合する。複数のそのようなメモリセルが、1つの不揮発性プログラム可能メモリアレイの中に含まれうる。また、再プログラム可能な不揮発性プログラム可能メモリセルが、記述される。  (もっと読む)

(もっと読む)

1 - 10 / 43

[ Back to top ]