国際特許分類[H01L21/58]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | サブグループ21/06〜21/326の一つに分類されない方法または装置を用いる半導体装置の組立 (13,682) | 支持体上への半導体装置のマウント (9)

国際特許分類[H01L21/58]に分類される特許

1 - 9 / 9

半導体装置、半導体装置の再生方法、および半導体装置の製造方法

【課題】回路基板から半導体パッケージを取り外した後、半導体パッケージの再取り付けが容易である半導体装置を提供する。

【解決手段】半導体装置は、回路基板と、半導体パッケージと、回路基板と前記半導体パッケージとを電気的に接続するはんだ接合部と、回路基板と半導体パッケージとの間に配置され、はんだ接合部が通る穴を有し、穴は、穴の最も狭い部分に対し半導体パッケージ側に配置された部分のはんだ接合部よりも細く形成されている板状部材とを有する。

(もっと読む)

半導体装置の製造方法

【課題】フェノール樹脂を含有する保護膜とダイアタッチ層との密着性に優れる信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】少なくとも(1)ウエハ上にフェノール樹脂を含有する樹脂膜を形成する工程、(2)前記樹脂膜に反応性ガスを用いたプラズマ処理を圧力60Pa以下でする工程、(3)前記プラズマ処理した樹脂膜上にダイアタッチ層を形成する工程および(4)前記ダイアタッチ層上に基板を積層する工程をこの順に有することを特徴とする半導体装置の製造方法。

(もっと読む)

絶縁ゲート型半導体装置

【課題】破壊耐量を向上させることができる絶縁ゲート型半導体装置を得る。

【解決手段】絶縁ゲート型半導体装置は、ダイボンド基板3と、ダイボンド基板3に半田2によってダイボンドされた半導体チップ1とを備える。ダイボンド前の半導体チップ1の電気特性のチップ面内分布を不均一にすることで、ダイボンドにより半導体チップ1に印加される応力による半導体チップ1の電気特性の変化を打ち消して、ダイボンド後の半導体チップ1の電気特性のチップ面内分布を均一にする。

(もっと読む)

2個の接合素子の低温加圧焼結接合方法およびそれによって製造される構成体

【課題】低温加圧焼結接合時に空洞の形成あるいはそのサイズを低減した2個の接合素子の低温加圧焼結接合方法およびそれによって製造される構成体を提供する。

【解決手段】構成体製造方法は、第1接触面16を有する第1接合素子10を用意するステップ、焼結金属の粒子および溶剤から構成される焼結ペーストからなる層を第1接触面16に施与するステップ、焼結ペーストに温度を加えて、焼結層を形成するように溶剤を追い出すステップ、その焼結層に液体を施与するステップ、第2接合素子50を配置するステップ、接着剤62を、焼結層と第2接合素子50との縁部領域に、第1接合素子10にも接触する状態で塗着するステップ、接合素子10、50間の材料密着結合の低温加圧焼結接合を形成するために、構成体にさらに温度および圧力を加えるステップであって、焼結層が均質な焼結金属層34に転化されるステップ、を有する。

(もっと読む)

電子部品取り付け状態検査装置及び電子部品取り付け状態検査方法

【課題】ペースト過多の状態で取り付けられた電子部品を排除して製品の良品率を向上させることができる電子部品取り付け状態検査装置及び電子部品取り付け状態検査方法を提供することを目的とする。

【解決手段】アイランド部2aに接合された電子部品3の周囲からはみ出たペーストPstを含む領域を撮像したうえで、その撮像によって得られた画像に基づいて、電子部品3の周囲からはみ出たペーストPstの外径形状を検出し、その検出した電子部品3の周囲からはみ出たペーストPstの外径形状から得られる、電子部品3の一辺からはみ出たペーストPstのその一辺からの最大はみ出し距離YSが予め定めた許容距離RYSを上回る場合に、アイランド部2aに対する電子部品3の取り付け状態が不良であると判定する。

(もっと読む)

半導体ウェハの裏面を被覆する方法

本発明は、半導体ウェハの裏面全体に被覆物を堆積させる方法を提供する。本発明の方法は、半導体ウェハの裏面への被覆物の堆積に通常伴う欠陥に対処する。本発明の方法は結果的に、被覆物がウェハの縁部の最後まで施されたウェハになるので、ダイシング中のチップ飛散、およびウェハ破損およびチップ破損が最小限となる。その上、本発明の方法は結果的に、従来のスピンコート法と比較して廃棄物が著しく減少する。 (もっと読む)

光学部品実装用サブマウント、及び光送受信モジュール

【課題】簡易且つ確実に精度良く光学部品の実装が可能な光学部品実装用サブマウント、及びこれを用いた光送受信モジュールを提供すること。

【解決手段】 例えば、サブマウント22は、略直方体状の基板から構成されている。このサブマウント22には、高分子光導波路フィルム10を取付けるための凹部26(光学部品実装用凹部)と、受光素子及び発光素子を嵌め込んでそれぞれ保持(実装)するための凹部28a,28b(光学部品実装用凹部)とが形成されている。このような構成のサブマウント22において、光学部品実装用凹部としての凹部26,28a,28bは、4つ或いは3つの側壁がテーパー状となっており、開口が底面よりも大きくなるように設ける。

(もっと読む)

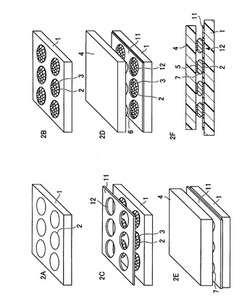

半導体装置およびその製造方法

【課題】 回路要素のキャパシタを備え、小型で冗長な配線を持たないICチップを搭載した低コストの半導体装置、およびその製造方法を提供すること。

【解決手段】 所定の厚さに裏面研削されたICチップ1のシリコン基板11の表面の電極または配線12を平行平板電極の一方の電極とし、一方の電極と対向して、シリコン基板11の裏面にパッケージ基板2の表面の電極または配線22を密接させ他方の電極とすると共に、ICチップ1とパッケージ基板2との間の電極または配線22を除く部分に接着樹脂4を適用して、パッケージ基板2上にICチップ1をフェイスアップに搭載する。これによって、シリコン基板11を誘電体層とし、一方の電極12と他方の電極22とからなるキャパシタ8を形成させる。

(もっと読む)

導電性接着剤および半導体装置

1 - 9 / 9

[ Back to top ]