国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

8,681 - 8,690 / 9,686

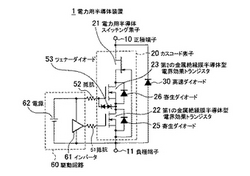

電力用半導体装置

【課題】逆回復電流に起因するスイッチング損失を減少することができ、発熱損失を減少することができ、小型化を実現することができる電力用半導体装置を提供する。

【解決手段】電力用半導体装置1において、カスコード素子20の電力用半導体スイッチング素子21のソース領域と負極端子11との間に複数直列接続された第1の金属絶縁膜半導体型電界効果トランジスタ22及び第2の金属絶縁膜半導体型電界効果トランジスタ23を備え、カスコード素子20に対して電気的に並列に高速ダイオード30を備える。電力用半導体スイッチング素子21はノーマリーオン型であり、第1の金属絶縁膜半導体型電界効果トランジスタ22及び第2の金属絶縁膜半導体型電界効果トランジスタ23はノーマリーオフ型である。

(もっと読む)

半導体集積回路

高閾値を有する第1導電型トランジスタおよび低閾値を有する第2導電型トランジスタは、電源電圧が供給される第1実電源線と、低閾値を有するトランジスタで構成される回路ブロックの電源端子に接続される仮想電源線との間に直列に接続されている。第1および第2導電型トランジスタは、互いに逆の極性を有している。電源制御回路は、第1および第2導電型トランジスタを、回路ブロックの動作中にオンさせるとともに、回路ブロックの非動作中にオフさせる。高閾値を有する第1導電型トランジスタに低閾値を有する第2導電型トランジスタを直列に接続することで、第1および第2導電型トランジスタのオン抵抗の増加を最小限にするとともに、オフ抵抗を増加させることができる。このため、第1および第2導電型トランジスタのサブスレッショルド電流を抑制できる。この結果、半導体集積回路のスタンバイ期間の消費電力を削減できる。  (もっと読む)

(もっと読む)

トランジスタ半導体装置

【課題】 バラスト抵抗を用いることなく、トランジスタの熱暴走を防止することができるトランジスタ半導体装置を提供する。

【解決手段】 同一の半導体基板上に配置されている、アンプ回路10のトランジスタTr1とバイアス回路20のダイオードD1及びダイオードD2とを、熱伝導の良好な金属材料等によって形成される熱伝導配線30で覆う。この熱伝導配線30により、トランジスタTr1で生じる温度上昇を速やかにダイオードD1及びダイオードD2に伝達することができる。ダイオードD1及びダイオードD2は、トランジスタTr1の温度を下げる方向に動作するため、トランジスタTr1の熱暴走を防止することができる。

(もっと読む)

半導体装置

【課題】半導体装置の放熱性を向上させ、素子で生じた熱が特定の回路に伝達され難くする。

【解決手段】半導体装置は、第1素子分離絶縁膜41と、それにより熱伝導率の低い第2素子分離絶縁膜42とを備えている。熱の伝達を抑制したいMOSトランジスタT1とMOSトランジスタT2との間には、熱伝導率の低い第2素子分離絶縁膜42を配設し、それ以外の素子間には第1素子分離絶縁膜41を配設する。

(もっと読む)

薄膜キャパシタ、その製造方法、及び、半導体装置

【課題】 薄膜キャパシタ、その製造方法、及び、半導体装置に関し、インターポーザ構造やフレキシブルなフィルム状キャパシタを採用することなく、半導体集積回路素子とデカップリングキャパシタを最短距離で実装するとともに、接続信頼性を向上する。

【解決手段】 半導体集積回路素子11を実装し電気的に接続するパッケージ基板9に設けたはんだバンプ10位置に対応する部分をくり貫いた貫通孔8を有する支持基板2上に設けるキャパシタを誘電体層4と、誘電体層4を挟持する上部電極5及び下部電極3によって構成するとともに、上部電極5及び下部電極3と電気的に接続されるとともに、はんだバンプ10の一部と電気的に接続される配線層7を上部電極5及び下部電極3と異なる材料で構成する。

(もっと読む)

(001)配向したペロブスカイト膜の形成方法、およびかかるペロブスカイト膜を有する装置

本発明は一般に強誘電体膜を有する装置に係り、特にシリコン基板上にエピタキシャル成長した強誘電体を有する半導体装置に関する。

本発明は、(111)配向した基板と、前記基板上に形成された(001)配向のペロブスカイト構造を有するエピタキシャル膜と、前記エピタキシャル膜上に形成された電極とを含む容量素子であり、ペロブスカイト型エピタキシャル膜の成膜方法は、(111)配向を有する基板上に(001)配向を有する岩塩構造の金属酸化物膜をエピタキシャルに成長し、前記金属酸化物膜上に(001)配向を有しペロブスカイト構造を有する金属酸化物膜をさらにエピタキシャルに成長する工程を含む。

本発明により、強誘電体メモリやSAWフィルタ、強誘電体アクチュエータなどの様々な機能素子を形成することが可能になる。  (もっと読む)

(もっと読む)

I/Oセル及び半導体装置

【課題】 チップ面積の縮小化等を可能とするI/Oセル等を提供する。

【解決手段】 I/Oセル61は、第1保護素子サブブロック11、第2保護素子サブブロック12、第1駆動素子サブブロック13、第2駆動素子サブブロック14、第1制御素子サブブロック15、及び、第2制御素子サブブロック16を含んでいる。第1駆動素子サブブロック13、第1保護素子サブブロック11、第2保護素子サブブロック12、及び、第2駆動素子サブブロック14は、第1の方向に沿って配列されている。第1制御素子サブブロック15は、第1の方向と交差する第2の方向において第1保護素子サブブロック11に隣接するように配置され、第2制御素子サブブロック16は、第2の方向において第2保護素子サブブロック12に隣接するように配置されている。

(もっと読む)

論理回路を有する電子装置及び論理回路を設計する方法。

論理回路LCを備える電子装置が提供される。論理回路LCは、少なくとも一の電子ユニットEU、特に一の論理ゲートを有する。電子ユニットEUは、論理演算を実行する第1電子的構成要素EC1;及び、論理回路LCのソフトエラー感度を改善するための少なくとも一の第2電子的構成要素EC2を有する。第1及び第2電子的構成要素EC1,EC2は実質的に同一の論理機能を備えて実装される。第2電子的構成要素EC2は重複である。加えて、第1及び第2電子的構成要素EC1,EC2の入力はそれぞれ結合され、第1及び第2電子的構成要素EC1,EC2の出力はそれぞれ結合される。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置の組立製造時に発生する当該半導体装置に対する内部および外部応力による半導体装置の電気特性劣化箇所およびモードを検出することができ、さらに半導体装置製造直後の電気特性劣化を検出する。

【解決手段】電極パッド1の最上層の直下に、SiN材で構成された層間絶縁膜3を介して抵抗配線4,6を設け、この抵抗配線4,6を断面方向に対して数層に渡って設ける。各抵抗配線4,6は、その幅および長さを電極パッド1内の一定範囲ごとに変化させ、かつ配線抵抗値の差を各配線にもたせておく。これにより回路構成の端子に電流および電圧を印加すると、電極パッド1直下の特定の範囲において、配線の断線、あるいは異なる抵抗値を有する配線間におけるショート、あるいは電極パッドと配線間にリークが発生した場合に、回路全体の抵抗値変動が発生する。これを検出することにより、半導体装置の電気特性劣化箇所などを検出することができる。

(もっと読む)

保護回路

【課題】 電圧入力端子を持つ電気回路を過大電圧から保護するにあたり、過大電圧を確実に接地する一方において正常電圧を接地してしまわないようにする。

【解決手段】 トランジスタのコレクタを電圧入力端子に接続し、エミッタを接地する。またベースは抵抗を介して接地する。その抵抗は可変抵抗であり、電圧入力端子の電圧が高いほど抵抗値が高くなる特性のものを利用する。

電圧入力端子に入力する電圧が過大に上昇する場合には、抵抗値が増大してブレークダウン電圧が低下する。電圧入力端子に入力する電圧が過大に上昇するまえにトランジスタがブレークダウンし、電圧入力端子に入力する最大電圧を低く抑えることができる。電圧入力端子に入力する電圧が適正電圧である場合には、抵抗値が減少してブレークダウン電圧が上昇する。電圧入力端子に適正電圧が入力する限り、電気回路は適正に動作する。

(もっと読む)

8,681 - 8,690 / 9,686

[ Back to top ]