国際特許分類[H01L29/423]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475) | 整流,増幅またはスイッチされる電流を流さないもの (2,575)

国際特許分類[H01L29/423]に分類される特許

1,001 - 1,010 / 2,575

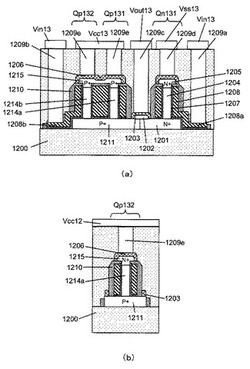

半導体装置およびその製造方法

【課題】縦型MOSトランジスタの小型化、それに伴い増加する寄生抵抗、寄生容量の低減。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成される第1のドレイン/ソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成される第2のソース/ドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1又は第2のMOSトランジスタの第2のソース/ドレイン領域の上面の面積は、第1又は第2のMOSトランジスタの柱状半導体層のそれぞれの上面の面積よりも大きく、第1のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部と第2のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部とを接続するシリサイド層が形成される。

(もっと読む)

半導体装置

【課題】ゲルマニウム層に浅いn型不純物拡散領域を形成可能とした半導体装置を提供する。

【解決手段】ゲルマニウムを主成分とするp型半導体と、前記p型半導体の表面に選択的に設けられた一対のn型不純物拡散領域と、前記一対のn型不純物拡散領域により挟まれた前記p型半導体の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上に設けられたゲート電極と、を備え、前記n型不純物拡散領域の少なくとも一部は、シリコン及び炭素から選択された少なくともいずれかの添加元素を含有していることを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置

【課題】縦型MOSトランジスタの小型化、及びそれに伴って増加する寄生抵抗、寄生容量を低減すること。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成されるドレイン又はソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成されるソース又はドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部と第2のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部とを接続するシリサイド層が形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】SGOI(110)基板上のp、n両領域で高移動度の半導体装置を実現する。

【解決手段】Si1-xGex(0.25≦x≦0.90)の(110)面を表面に有する半導体基板(1,2,3)と、(110)面上に形成されたn及びpチャネル型MISFETとを具備し、両MISFETは、[−110]方向が[001]方向より長い線状で、(311)若しくは(111)面のファセットを有する活性領域(5,6)を有し、活性領域の[−110]方向に、ソース領域・チャネル領域・ドレイン領域が形成され、nチャネル型MISFETのチャネル領域(5C)はSiで形成され、pチャネル型MISFETのチャネル領域(6C)はSi1-yGey(x<y≦1)で形成され、両MISFETのチャネル領域は、活性領域の[−110]方向に、一軸圧縮ひずみを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】強度の低下を抑制しつつ、オン抵抗を低減することが可能な半導体装置およびその製造方法を提供する。

【解決手段】SBD1は、SiC基板10と、SiC基板10の一方の主面10A上に形成されたn−SiC層20とを備えている。SiC基板10の、一方の主面10Aとは反対側の主面である他方の主面10Bには複数の凹部11が形成されている。そして、凹部11には、SiC基板10を構成するSiCよりも電気伝導率の高い高伝導率材料が充填されている。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに導電型の同じMISトランジスタを備えた半導体装置において、互いに閾値電圧の異なるMISトランジスタを精度良く且つ高性能に実現する。

【解決手段】第1のMISトランジスタLTrは、第1の活性領域1aに形成された第1のチャネル領域3aと、第1のチャネル領域上に形成された高誘電率絶縁膜からなる第1のゲート絶縁膜4aと、第1のゲート絶縁膜上に接する第1の導電部12aと、第2の導電部13aとを有する第1のゲート電極20Aとを備え、第2のMISトランジスタHTrは、第2の活性領域1bに形成された第2のチャネル領域3bと、第2のチャネル領域上に形成された高誘電率絶縁膜からなる第2のゲート絶縁膜4bと、第2のゲート絶縁膜上に接する第3の導電部12bと、第4の導電部13bとを有する第2のゲート電極20Bとを備え、第3の導電部は、第1の導電部よりも薄い膜厚で且つ第1の導電部と同じ組成材料からなる。

(もっと読む)

アレイ基板

【課題】半導体層にゲルマニウムを添加した際、ゲート絶縁膜のリークによるTFT特性劣化を抑制する。

【解決手段】非晶質シリコンの固相成長の低温化を図るため、TFT33の半導体層35にゲルマニウムを添加し、かつゲート絶縁膜20bのゲートリーク電流を抑えるため、窒化物を主成分とするゲート絶縁膜20bを用いる。

(もっと読む)

薄膜トランジスタ、マトリクス基板、電気泳動表示装置および電子機器

【課題】有機半導体膜を用いた薄膜トランジスタの特性の向上を図る。

【解決手段】本発明に係る半導体装置は、基板の上方に、対向して配置されたソース電極(7s)およびドレイン電極(7d)と、ソース電極およびドレイン電極間に配置された有機半導体膜(5)と、有機半導体膜の第1面又は前記第1面と逆側の第2面上にゲート絶縁膜(9)を介して形成されたゲート電極(11)と、を有し、ゲート電極は、ソース電極およびドレイン電極間と、有機半導体膜とが重なるチャネル領域に、開口部(11a)を有する。かかる構成によれば、上記開口部を介して光が入射し、チャネル領域にトラップされたキャリア(電子又はホール)をデトラップすることができる。よって、薄膜トランジスタの特性劣化を低減できる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】ゲート絶縁膜上に密着性良好な金属単層膜から成るソース/ドレイン電極を確実に形成し得る電界効果型トランジスタの製造方法を提供する。

【解決手段】電界効果型トランジスタの製造方法は、(A)基体11の表面にシランカップリング処理を施す工程と、(B)シランカップリング処理された基体11上にゲート電極12を形成する工程と、(C)ゲート電極12上にゲート絶縁膜13を形成する工程と、(D)ゲート絶縁膜13の表面にシランカップリング処理を施す工程と、(E)シランカップリング処理されたゲート絶縁膜13上に、金属単層膜から成るソース/ドレイン電極14を形成する工程と、(F)ソース/ドレイン電極14間のゲート絶縁膜13上に、半導体材料層から成るチャネル形成領域15を形成する工程から成る。

(もっと読む)

半導体集積回路装置

【課題】シェアードコンタクトと不純物拡散領域との接触抵抗を小さくする。

【解決手段】半導体基板301上に、ゲート絶縁膜312を介して形成された第1のゲート電極310と、ゲート絶縁膜322を介して形成された第2のゲート電極320と、第1および第2のゲート電極310および320の間の半導体基板301表面に形成された不純物拡散領域と、第2のゲート電極320と不純物拡散領域との間を接続するシェアードコンタクト224とを備える半導体記憶装置において、シェアードコンタクト224は、セルフアラインコンタクト手法による開口と、第2のゲート電極320と接続を取るための開口とにより形成される。このセルフアラインコンタクト手法を用いることで、シェアードコンタクト224と不純物拡散領域との接触面積が最大限確保され、接触抵抗が低減される。

(もっと読む)

1,001 - 1,010 / 2,575

[ Back to top ]