国際特許分類[H01L29/778]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 二次元電荷担体ガスチャンネルをもつもの,例.HEMT (1,960)

国際特許分類[H01L29/778]に分類される特許

1,951 - 1,960 / 1,960

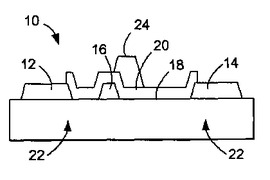

シングルゲートまたはマルチゲートフィールドプレート製造

電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセス。本製造プロセスのは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。  (もっと読む)

(もっと読む)

窒化物半導体装置

HEMTは、シリコン基板(1)、窒化物半導体から成るバッファ領域(2)、窒化物半導体領域(3)、ソース電極(4)、ドレイン電極(5)、ゲート電極(6)、絶縁膜(7)、導体膜(8)及びコンタクト電極(9)を有している。バッファ領域(2)はシリコン基板(1)の上に複数回繰返して成長されたAINから成る第1の層(13)とGaNから成る第2の層(14)とから成る。半導体領域(3)は電子走行層(15)と電子供給層(16)とを有している。バッファ領域(2)及び半導体領域(3)の側面(17)は傾斜している。この傾斜側面(17)に絶縁膜(7)を介して導体膜(8)が対向している。導体膜(8)はコンタクト電極(9)を介してシリコン基板(1)に接続され、側面(17)における漏れ電流の低減に寄与する。 (もっと読む)

半絶縁性GaNおよびその製造方法

電子および/または光電子用途用のGaNデバイスを作製するための基板を形成するために有用に用いられる大面積単結晶半絶縁性窒化ガリウムを開示する。大面積半絶縁性窒化ガリウムは、たとえばMn、Fe、Co NiおよびCuなどの深いアクセプタドーパント種で、成長している窒化ガリウム材料をその成長中にドープして、窒化ガリウムにおけるドナー種を補償しかつ窒化ガリウムに半絶縁特性を付与することによって、容易に形成される。  (もっと読む)

(もっと読む)

スプリットチャネル高電子移動度トランジスタデバイス

トランジスタ構造体であって、ガリウムヒ素(GaAs)半導体基板と、インジウムアルミニウムガリウムヒ素(InAlGaAs)格子整合層と、格子整合層の上に配設されるインジウムアルミニウムヒ素(InAlAs)バリア層と、バリア層上に配設されるInyGa1−yAs下部チャネル層であって、yは下部チャネル層のIn含有量のモル分率である、InyGa1−yAs下部チャネル層と、下部チャネル層上に配設されるInxGa1−xAs上部チャネル層であって、xは上部チャネル層のIn含有量のモル分率であり、xはyと異なる、InxGa1−xAs上部チャネル層と、InxGa1−xAs上部チャネル層上のInAlAsショットキー層とを有するトランジスタ構造体。下部チャネル層は、上部チャネル層のバンドギャップより大きいバンドギャップを有し、下部チャネル層は、上部チャネル層のバルク電子移動度より低いバルク電子移動度を有する。 (もっと読む)

化合物半導体層の表面処理方法及び半導体装置の製造方法

【課題】窒素を含む化合物半導体層の表面に生じた、エッチングによるダメージを除去あるいは軽減し、ゲート電極に良好なショットキ特性を有する半導体装置を形成する。

【解決手段】ドライエッチングにより、第1化合物半導体層22のゲート電極形成予定領域36の表面を露出するとともに、コンタクト層32を形成する。次いで、この第1化合物半導体層22の露出した表面に対するアニール処理を行う。前述のドライエッチングの際に第1化合物半導体層22の表面に生じたダメージを、窒素プラズマを用いた表面処理を行うことにより、良好な電気特性をもつ第1化合物半導体層22の表面を形成する。この窒素プラズマを用いた表面処理を行った第1化合物半導体層22の表面上にゲート電極38を形成し、良好なショットキ特性を有するゲート電極を具えたリセス型HEMT10を形成する。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】耐圧性、特性安定性に優れ、ゲートリーク電流が低減されたヘテロ接合型電界効果トランジスタを提供すること。

【解決手段】半導体基板上にバッファ層と、チャネル層と、スペーサ層と、キャリア供給層と、ショットキーバリア層と、高濃度不純物ドープキャップ層とが順次堆積され、ソース電極及びドレイン電極がキャップ層表面に形成され、ソース電極とドレイン電極の間のキャップ層にショットキーバリア層に達する開口部が形成され、開口部に露出したショットキーバリア層表面にゲート電極が形成されているヘテロ接合型電界効果トランジスタであって、キャップ層が複数の細線で構成され、細線間はショットキーバリア層が露出し、ソース電極及びドレイン電極が、細線と細線間に露出したショットキーバリア層との両方に接触していることを特徴とするヘテロ接合型電界効果トランジスタを構成する。

(もっと読む)

ヘテロ接合電界効果トランジスタ

【課題】 ゲート耐圧を十分に高く維持しながら、ソース抵抗の大幅な低減により高性能化が可能なヘテロ接合電界効果トランジスタを提供する。

【解決手段】 C面サファイア基板1上に、バッファ層を介して、アンドープGaN層2、アンドープAl0.3 Ga0.7 N層3、アンドープGaNチャネル層4、アンドープAl0.15Ga0.85Nスペーサ層5、n型Al0.15Ga0.85N電子供給層6、傾斜組成アンドープAlz Ga1-z N障壁層7およびn型Al0.06Ga0.94Nコンタクト層8を順次積層し、n型Al0.06Ga0.94Nコンタクト層8上にゲート電極9、ソース電極10およびドレイン電極11を設け、AlGaN/GaN HEMTを構成する。傾斜組成アンドープAlz Ga1-z N障壁層7のAl組成zはn型Al0.15Ga0.85N電子供給層6からn型Al0.06Ga0.94Nコンタクト層8に向かって0.15から0.06まで連続的に減少させる。

(もっと読む)

電子波方向性結合素子

半導体装置の製造方法

ヘテロ接合電界効果トランジスタ

1,951 - 1,960 / 1,960

[ Back to top ]