国際特許分類[H01L29/792]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 電荷トラッピングゲート絶縁体,例.MNOSメモリトランジスタ,を有するもの (4,374)

国際特許分類[H01L29/792]に分類される特許

1,001 - 1,010 / 4,374

垂直形不揮発性メモリ装置及びその製造方法

【課題】垂直形不揮発性メモリ装置及びその製造方法を提供する。

【解決手段】半導体基板100上に垂直に備わるフィラー形状の単結晶半導体チャンネルと、単結晶半導体チャンネルの側面に一定間隔を有しながら積層される第1〜第n+1階(nは2以上の自然数)層間絶縁膜(パターン)122a−122eと、層間絶縁膜(パターン)122a−122e上に備わる電荷トラップ膜170と、電荷トラップ膜170上に備わるブロッキング絶縁膜175、ブロッキング絶縁膜175上に備わっている第1〜第n層コントロールゲート電極パターン185a−185dを含む。また、最下位及び最上位層間絶縁膜上に電荷トラップレイヤーのないGSL及びSSLゲートを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】HV系トランジスタでの閾値電圧の上昇を防止する半導体装置とその製造方法を提供する。

【解決手段】半導体基板10と、トランジスタ領域の半導体基板10を素子領域に分離する素子分離絶縁膜204と、トランジスタ領域に設けられた複数のトランジスタと、素子分離絶縁膜204の下に形成された反転防止拡散層209とを具備し、トランジスタは、素子領域上に形成されたゲート絶縁膜11と、ゲート絶縁膜11上に形成され素子分離絶縁膜204上に延びるゲート電極203と、ゲート電極203を挟むように半導体基板10表面に形成された拡散層18を有し、素子分離絶縁膜204は、素子領域に隣接する領域204−1と、領域204−1の底部より深い底部を有する領域204−2とを有し、反転防止拡散層209は、領域204−2の下に形成されている。

(もっと読む)

選択的プラズマ窒化処理方法及びプラズマ窒化処理装置

【課題】 シリコン表面とシリコン化合物層とが露出した被処理体に対して、選択的にシリコンを高い窒化レートと高い窒素ドーズ量でプラズマ窒化処理する方法を提供する。

【解決手段】 選択的プラズマ窒化処理は、処理圧力を66.7Pa以上667Pa以下の範囲内に設定し、載置台2の電極42に高周波電源44から被処理体の面積当り0.1W/cm2以上1.2W/cm2以下の高周波電力を供給して行う。この高周波電力によってウエハWへバイアス電圧が印加され、高いSi/SiO2選択比が得られる。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】酸化処理前における基板表面の初期酸化を抑えることができるとともに、自然酸化膜を除去できるようにする。

【解決手段】表面に少なくとも金属原子を含まずシリコン原子を含む層と、金属原子を含む層とが露出している基板を処理室内に搬入する工程と、処理室内に酸素含有ガスと水素含有ガスとを供給して基板表面を酸化処理する工程と、酸化処理後の基板を処理室内より搬出する工程とを有し、酸化処理工程では、処理室内の圧力を1333Pa(10Torr)以下とすると共に、酸素含有ガスの流量Aに対する水素含有ガスの流量Bの流量比B/Aを2以上とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】 製造工程数の増加を招くことなく形成可能であり、かつ、所望の抵抗値を得ることが可能な抵抗素子を備えた不揮発性半導体記憶装置を提供する。

【解決手段】

半導体基板上に形成されたメモリセルトランジスタと、抵抗素子とを備え、

抵抗素子10は、抵抗体30と、抵抗体30上の前記抵抗体両端部に形成された絶縁膜31と、第1絶縁膜31上に形成され、第1絶縁膜に形成された開口部を介して抵抗体30と接続されたポリシリコン電極層37と、ポリシリコン電極層37に電気的に接続されたコンタクトプラグCP3、CP4と、抵抗体30上の第1絶縁膜31の間の領域に形成された絶縁膜32と、絶縁膜32上に形成されたポリシリコン電極層38と、ポリシリコン電極層38に電気的に接続されたコンタクトプラグCP5と、を有することを特徴とする不揮発性半導体記憶装置。

(もっと読む)

窒化珪素膜の成膜方法および半導体メモリ装置の製造方法

【課題】 トラップが豊富に存在し、不揮発性半導体メモリ装置の電荷蓄積層として有用な窒化珪素膜をプラズマCVD法により成膜する方法を提供する。

【解決手段】 複数の孔を有する平面アンテナにより処理容器内にマイクロ波を導入してプラズマを生成して成膜を行うプラズマCVD装置においてシリコン原子と塩素原子からなる化合物のガスと窒素ガスを含む処理ガスを用い、処理容器内の圧力を0.1Pa以上8Pa以下の範囲内に設定してプラズマCVDを行うことにより、多くのトラップを含む窒化珪素膜を成膜する。

(もっと読む)

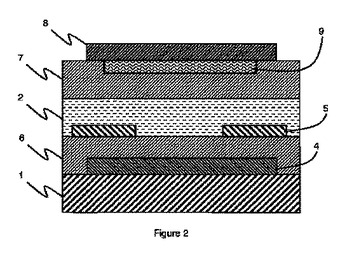

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置100は、ビット線BLと、ソース線SLと、複数のメモリトランジスタMTrを直列に接続されたメモリストリングMSと、ドレイン側選択トランジスタSDTrと、ソース選択トランジスタSSTrと、読出動作を制御する制御回路15とを備える。制御回路15は、非選択メモリストリングMS(unselO1)、MS(unselO2)に接続されたドレイン選択トランジスタSDTr(unsel)、SDTr(unselMB)を導通状態とし、、非選択メモリストリングMS(unselO1)、MS(unselO2)に接続されたソース選択トランジスタSSTr(unsel)、SSTr(unselMB)を非導通状態とする。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトを高密度に形成することができる半導体装置及びその製造方法を提供する。

【解決手段】NAND型フラッシュメモリ1において、単一の層間絶縁膜中に形成された全てのコンタクト、すなわち、ビット線コンタクトCB及び非ビット線コンタクトCNを、方向V1に沿って周期P1で配列されると共に方向V2に対して交差する方向V2に沿って周期P2で配列された2次元格子Lの複数の格子点LPの一部に配置する。そして、アクティブエリアが延びる一方向におけるビット線コンタクトCBの位置を、連続して配列された3本以上のアクティブエリアを基本単位として周期的に変位させる。また、同一の電位が供給される導電性部材に、2以上のコンタクトを接続する。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルの閾値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、半導体基板表面のウェル上に第1の絶縁膜を介して形成され周囲から絶縁された電荷保持層と、前記電荷保持層との間に第2の絶縁膜を介して設けられた制御ゲートと、を有し、且つ前記電荷保持層に保持された電荷量に応じた閾値電圧に対応して情報が記憶されるメモリセルトランジスタと、前記制御ゲートに印加する電圧、および前記ウェルに印加する電圧を制御することにより、前記メモリセルトランジスタの動作を制御する制御回路と、を備える。

(もっと読む)

1,001 - 1,010 / 4,374

[ Back to top ]