国際特許分類[H03F1/07]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみ,半導体装置のみまたは汎用素子のみを用いた増幅器の細部 (3,631) | 能率を上げるための増幅器の変形,例.A級段で用いるもの,補助振動を用いるもの (912) | 電子管増幅器におけるもの (233) | 変調された無線周波の増幅の能率を上げるためのもの;変調器としても動作する増幅器の能率を上げるためのもの (233) | ドハティ型増幅器 (149)

国際特許分類[H03F1/07]に分類される特許

1 - 10 / 149

増幅器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

ドハティ増幅器

【課題】 単純な回路構成を有し、調整が容易なドハティ増幅器を提供する。

【解決手段】 第1の入力信号を増幅するキャリアアンプ12と、飽和出力電力がキャリアアンプと異なり、第2の入力信号を増幅するピークアンプ22とを有し、キャリアアンプは、第1のトランジスタと、第1のトランジスタと同一のパッケージ内に設けられた第1の内部変換回路とを含み、ピークアンプは、第2のトランジスタと、第2のトランジスタと同一のパッケージ内に設けられた第2の内部変換回路とを含み、第1及び第2の内部変換回路は、第1及び第2のトランジスタの出力インピーダンスを互いに異なる値に変換する。

(もっと読む)

電力増幅回路、および無線通信装置

【課題】回路面積を縮小しつつ、電力効率の向上を図ることが可能な電力増幅回路を提供する。

【解決手段】電力増幅回路は、シリコン基板上に集積された電力増幅回路である。電力増幅回路は、入力が第1の信号入力端子に接続された第1のアンプを備える。電力増幅回路は、入力が第2の信号入力端子に接続された第2のアンプを備える。電力増幅回路は、入力が前記第1のアンプの出力に接続され、出力が前記第2のアンプの出力に接続されたアンプ出力移相器を備える。電力増幅回路は、一端が電源に接続され、他端が前記アンプ出力移相器の出力に接続された一次側巻線と、一端が第1の信号出力端子に接続され、他端が第2の信号出力端子に接続された二次側巻線と、を有するトランスフォーマと、を備える。

(もっと読む)

半導体パッケージ、及び半導体パッケージの製造方法

【課題】高周波電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージ(P)を提供すること。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

(もっと読む)

電子機器及び増幅器制御プログラム

【課題】3つ以上の増幅素子を使ったドハティ増幅器の電力効率を向上させる。

【解決手段】3Wayドハティ増幅器は、入力電力の増加にともなって順次動作し、並列接続されたFET202,204,206を備える。また、3Wayドハティ増幅器は、FET202,204,206のうち、中間で動作するFET204の直前で動作するFET202の出力が飽和したことを検出する制御回路224を備える。また、制御回路224は、中間で動作するFET204の直前で動作するFET202の出力が飽和したことを検出したら、電圧制御回路226に制御信号を出力し、FET204に供給する電源電圧を増加させる。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

ドハティ増幅器

【課題】広帯域化と小型化を図ることのできるドハティ増幅器を得る。

【解決手段】単位ドハティ増幅器100a,100bにおけるピーク増幅器2a,2bの入力側に、これらピーク増幅器2a,2bが共用する1/4波長線路3を設ける。単位ドハティ増幅器100a,100bのキャリア増幅器1a,1bの出力側にはそれぞれ1/4波長線路6a,6bが設けられ、キャリア増幅器1a,1bの出力とピーク増幅器2a,2bの出力とは信号合成器7で合成される。これにより広帯域化を図ることができると共に、ピーク増幅器2a,2b入力側の1/4波長線路を削減することができるため、小型化を図ることができる。

(もっと読む)

増幅装置

【課題】 より高効率で動作することができる増幅装置を得る。

【解決手段】 本発明による増幅装置は、入力信号を2分岐した一方の信号をA,BまたはAB級増幅するキャリア増幅器1と、2分岐した他方の信号に対して並列に設けられC級増幅する複数のピーク増幅器2及び3とを含み、複数のピーク増幅器2及び3の出力の合成に90°ハイブリッドカプラ5を用い、90°ハイブリッドカプラ5による複数のピーク増幅器2及び3の合成出力とキャリア増幅器1の出力とを負荷14に供給する。

(もっと読む)

ドハティ増幅器

【課題】2つのピーク増幅器のデバイス特性差による出力電流の違いから生ずる負荷変動の影響を低減して、相互変調歪み特性を改善すること。

【解決手段】分配回路により分配された第1の信号を増幅するキャリア増幅器と、キャリア増幅器の出力電力が飽和状態に近づいた場合に、上記分配された第2の信号を増幅する第1のピーク増幅器と、同分配された第3の信号を増幅する第2のピーク増幅器と、第1のピーク増幅器と第2のピーク増幅器との各出力信号を合成する第1の合成回路と、キャリア増幅器と第1の合成回路との各出力側のそれぞれから合成点に向かって整合を取ってキャリア増幅器と第1の合成回路との各出力信号を合成して出力する第2の合成回路とを具備し、第1の合成回路は、キャリア増幅器の出力の飽和時から所定の値だけバックオフしたバックオフ時に、合成点から第1及び第2のピーク増幅器側を見たインピーダンスを無限大に調整可能とする。

(もっと読む)

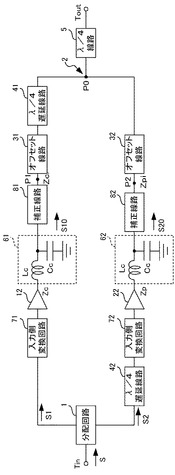

ドハティ増幅器及びドハティ増幅器のバイアス設定方法

【課題】ドハティ増幅器において、デバイスにばらつきがある場合にも、バイアス電圧を最適に設定できると共に、調整工数を削減できるようにする。

【解決手段】キャリア増幅器12とピーク増幅器13とで、ウェハロットや製造時期等のデバイスに関する共通要素を持つものを用い、ピーク増幅器13に対するバイアス電圧Vg2を、キャリア増幅器12に対するバイアス電圧Vg1と、所定のオフセット電圧Voffsetとから生成する。デバイスのばらつきに係わらず、ピーク増幅器13に対するバイアス電圧とピンチオフ電圧との差は同じになり、ピーク増幅器13のバイアス電圧が最適に設定される。また、キャリア増幅器12を構成するFETのゲートに印加するバイアス電圧を調整することで、同時に、ピーク増幅器13を構成するFETのゲートに供給するバイアス電圧も調整できる。

(もっと読む)

1 - 10 / 149

[ Back to top ]