国際特許分類[H03F3/30]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | シングルエンデットプッシュプル増幅器;そのための位相分割器 (77)

国際特許分類[H03F3/30]の下位に属する分類

電子管のみをもつもの

国際特許分類[H03F3/30]に分類される特許

1 - 10 / 77

電源回路

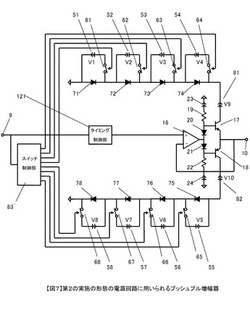

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

電力増幅器のバイアス回路および電力増幅器

【課題】コンプリメンタリSEPP回路において、出力抵抗を高くすることなくバイアス電流の安定したバイアス回路を提供する。

【解決手段】バイアス電流を検出する差動増幅器と、所定の電圧値と差動増幅器の出力電圧値との差分を増幅する演算増幅器と、演算増幅器の出力信号を絶縁伝達する絶縁伝達器と、絶縁伝達器の出力に応じたバイアス電圧を出力するバイアス電圧源とを備えたコンプリメンタリSEPP回路のバイアス回路。差動増幅器、演算増幅器、絶縁伝達器の動作により、バイアス電圧源は、バイアス電流が増加すると出力するバイアス電圧を低下させる。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

高線形性相補型増幅器

【課題】サブミクロンCMOSプロセスで製造されることができかつ良好な線形性および信頼性を有する相補型増幅器を提供する。

【解決手段】PMOSトランジスタ422とそれにスタック結合されたNMOSトランジスタ412で構成した相補型増幅器400で、NMOSトランジスタ412およびPMOSトランジスタ422は、別々のバイアス電圧を有し、それらのバイアス電圧は、各トランジスタの相互コンダクタンスの低高および高低遷移をオーバーラップさせるように選択され、各トランジスタの幅および長さ寸法は、中反転領域におけるNMOSトランジスタ412の入力容量の変化および相互コンダクタンスの変化を中反転領域におけるPMOSトランジスタ422の入力容量の変化および相互コンダクタンスの変化と整合させるように選択される。それによりほぼ一定の総入力容量およびほぼ一定の総相互コンダクタンスを有しうる。

(もっと読む)

出力回路

【課題】より十分な出力電流を流せる出力回路を提供する。

【解決手段】PMOSトランジスタ12のドレイン電流が大きい場合、PMOSトランジスタ13は非飽和領域で動作する。このときNMOSトランジスタ14及び17のゲート電圧は電源端子電圧付近まで上昇している。このため、NMOSトランジスタ17のゲート・ソース間電圧は大きくなり、十分な出力電流が流れる。

(もっと読む)

増幅回路

【課題】SEPP回路の温度上昇の熱が放熱器を介してバイアス回路に伝わるまでの熱結合によるタイムラグを解消して、熱暴走の発生を未然に防止する。

【解決手段】トランジスタ素子を有して構成されるトランジスタQ1と、トランジスタQ1のトランジスタ素子とは逆極性のトランジスタ素子を有して構成されるトランジスタQ2と、が直列接続されると共に、両端が電源に接続されたシングルエンデッド・プッシュプル回路と、トランジスタQ1回路にバイアス電圧を印加するバイアス回路を構成するトランジスタQ5と、トランジスタQ2にバイアス電圧を印加するバイアス回路を構成するトランジスタQ6と、トランジスタQ1のベース電圧を検出してトランジスタQ5にフィードバックする直列接続の抵抗R3、R4と、トランジスタQ2のベース電圧を検出してトランジスタQ6にフィードバックする直列接続の抵抗R5、R6と、を備えている。

(もっと読む)

音響用擬似三極管特性増幅装置および音響用擬似三極管特性プッシュプル増幅装置

【課題】半導体素子を用いた音響用増幅装置において、その特性を三極管アンプの特性に近似させると共に、負荷に供給される出力信号の歪み成分を低減することを目的とする。

【解決手段】入力端子T1は、差動増幅回路12の正相端子に接続されている。差動増幅回路12の逆相端子はトランジスタ10のエミッタ電極に接続され、出力端子はトランジスタ10のベース電極に接続されている。トランジスタ10のコレクタ電極と入力端子T1との間には、入力側抵抗器R2が接続され、入力端子T1と接地導体との間には副入力側抵抗器R3が接続されている。トランジスタ10のエミッタ電極と接地導体との間には出力側抵抗器R1が接続されている。そして、トランジスタ10のコレクタ電極には、負荷端子TLが接続されている。

(もっと読む)

出力回路及び増幅回路

【課題】出力ダイナミックレンジを低下させることなく出力インピーダンスを変化させることができる出力回路及び増幅回路を提供する。

【解決手段】実施形態によれば、可変抵抗回路と、第1のトランジスタと、プッシュプル回路と、を備えたことを特徴とする出力回路が提供される。前記可変抵抗回路は、第1の抵抗と前記第1の抵抗に接続された第1のスイッチ素子とを有する。前記第1のトランジスタは、前記可変抵抗回路と直列的に接続され、前記第1の抵抗の抵抗値よりも出力抵抗の大きい状態にバイアスされる。前記プッシュプル回路は、前記第1のトランジスタにより駆動される。

(もっと読む)

1 - 10 / 77

[ Back to top ]