国際特許分類[H03H7/32]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | 回路網の部品として受動的電気素子のみを含む多端子対回路網 (1,834) | 時間遅延回路網 (17) | 集中インダクタンスと集中キャパシタンスをもつもの (4)

国際特許分類[H03H7/32]に分類される特許

1 - 4 / 4

差動遅延線およびコモンモードフィルタ

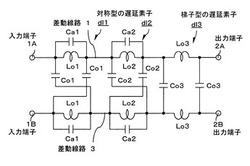

【課題】 超高速性および群遅延特性に優れた超小型の差動遅延線を実現する。

【解決手段】 直列素子としてのインダクタLoは一対の差動線路1、3に各々挿入される。交差素子としての交差キャパシタCoは、一方の差動線路1にあるインダクタLoの入力側と他方の差動線路3にあるインダクタLoの出力側間と、一方の差動線路1にあるインダクタLoの出力側と他方の差動線路3のインダクタLoの入力側間に各々接続される。並列キャパシタCaは、交差素子としての交差キャパシタCoの値よりも小さい値を有し、インダクタLoに並列接続される。これらの構成を1区間の対称格子型の差動遅延素子として複数区間縦続接続するとともに、少なくとも1区間以上、梯子型の差動遅延素子を縦続接続させる。

(もっと読む)

ジョセフソン分布出力増幅器のための方法および装置

本開示は、概して高速、低信号電力増幅を提供する方法および装置に関する。1つの例示的実施形態において、本開示は、第1の伝送線を第2の伝送線と並列に形成することによる、信号の広帯域増幅を提供する方法に関し、第1の伝送線および第2の伝送線の各々は、複数の超伝導伝送要素を有し、各伝送線は伝送線遅延を有し、複数の増幅段を第1の伝送線と第2の伝送線との間に挿入し、各増幅段は共振回路遅延を有する共振回路を有し、複数の増幅段のうちの少なくとも1つに対する共振回路遅延を超伝導伝送線のうちの少なくとも1つの伝送線遅延と、実質的に整合させる。  (もっと読む)

(もっと読む)

遅延線

【課題】簡単な構成で、通過帯域の広帯域化、絶対遅延時間偏差の低減化、絶対遅延時間の増大化を実現させる。

【解決手段】遅延線10Aは、第1の遅延回路12と第2の遅延回路14とを有する。第1の遅延回路12は、入力端子16と出力端子18とを有する帯域通過遅延線やその他の遅延線で構成される。第2の遅延回路14は、入力端子20、第1の出力端子22a、第2の出力端子22b及びアイソレーション端子24を備えたハイブリッドカプラ26と、第1の出力端子22aに接続された第1のリアクタンス部28Aと、第2の出力端子22bに接続された第2のリアクタンス部28Bとを有する。さらに、第1の遅延回路12の出力端子18と第2の遅延回路14におけるハイブリッドカプラ26の入力端子20とが電気的に接続されている。

(もっと読む)

電磁遅延線のインダクタンス素子

【課題】 集中定数型電磁遅延線のインダクタンス素子において、チップ状の超小型化が容易で、各区間を好ましい結合状態にできるようにする。

【解決手段】 第1の絶縁基板15にスパイラル状のインダクタL0B、L4A、L4Bを形成し、インダクタL4AとL4Bを直列接続する。第2、第3の絶縁基板22、33にスパイラル状のインダクタL1、L3、L5を形成する。第4の絶縁基板41にスパイラル状のインダクタL2A、L2B、L6Aを形成し、インダクタL2A、L2Bを直列接続する。第1〜第4の絶縁基板15〜41を重ね、インダクタL0B〜L6Aを縦続接続する。インダクタL2AとL2B、L4AとL4Bを平面的に2分割して1区間を形成し、平面的に分割されない前後の区間と正結合させる。

(もっと読む)

1 - 4 / 4

[ Back to top ]