国際特許分類[H03K17/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 完全導通状態を確保するための変形 (176)

国際特許分類[H03K17/06]に分類される特許

171 - 176 / 176

電力スイッチを操作するための方法及び装置

本発明は半導体電力スイッチを操作するための方法であって、この方法によって半導体電力スイッチのスイッチング区間(E−A)の抵抗は制御電圧(Vst)によって電力スイッチ(S1、S2)のチップ温度(T1ist、T2ist)が予め設定される目標温度(Tsoll)を超えないように制御され、この目標温度(Tsoll)に到達した場合にはスイッチング区間(E−A)の抵抗が高められる。この方法を実施するための装置は半導体電力スイッチとしてトランスファーゲート(TG)を使用し、このトランスファーゲート(TG)はチャージポンプ(LP)によって制御され、半導体電力スイッチとしてのこのトランスファーゲート(TG)において統合された温度センサを有する商用トランジスタが使用される。  (もっと読む)

(もっと読む)

低電力高性能記憶回路及び関連方法

第1NMOSトランジスタ、第1PMOSトランジスタ、第2NMOSトランジスタ、第2PMOSトランジスタ、第2PMOSの第1ソース/ドレインに接続された第1バイアス電圧ノード、第1PMOSトランジスタのゲートに接続された第3バイアス電圧ノード、第1PMOSトランジスタのゲートに接続された第4バイアス電圧ノード、第1NMOSトランジスタの第2ソース/ドレインを第1PMOSトランジスタの第1ソース/ドレインに接続するプルアップノード、第2PMOSトランジスタの第2ソース/ドレインを第2NMOSトランジスタの第1ソース/ドレインに接続するプルダウンノード、入力ノード、第1PMOSトランジスタの第2ソース/ドレインを第2NMOSトランジスタの第2ソース/ドレインに接続する記憶ノード、出力ノード、入力データ値を入力ノードから第1NMOSトランジスタのゲートと第2PMOSトランジスタのゲートに制御可能に伝達するべく接続された入力スイッチ、及び保存されているデータ値を記憶ノードから出力ノードに制御可能に伝達するべく接続された出力スイッチを有する集積回路である。  (もっと読む)

(もっと読む)

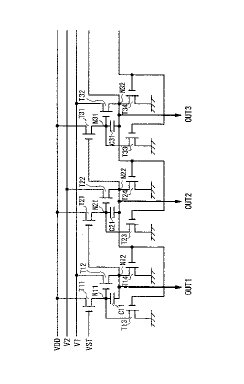

信号伝送回路、固体撮像装置、カメラおよび表示装置

【課題】回路電源を高速化または低電圧化しても安定な動作が可能で、高速化または低消費電力化に適した信号伝送回路を提供する。

【解決手段】複数の単位回路で構成され、駆動パルスに従って単位回路からパルス電圧が順次出力される。単位回路は、駆動パルスをドレインに入力して、パルス電圧としてソースから出力する第1の出力トランジスタ(T12)と、第1の出力トランジスタのゲートとソースとの間に接続された第1のブートストラップ容量(C11)と、第1のブートストラップ容量を充電するために、ソースが第1の出力トランジスタのゲートに接続され、ドレインが電源線または接地線あるいは充電パルス線に接続された充電トランジスタ(T11)と、一端が充電トランジスタのゲートに接続された第2のブートストラップ容量(C22)とを備える。

(もっと読む)

信号増幅用回路、及びアクティブマトリクス装置における同回路の使用

増幅回路はキャパシタ構造(42)と切替装置とを備える。キャパシタ構造は、電圧依存性静電容量を有する第一のキャパシタ(C2)と第二のキャパシタ(C1)(これもまた電圧依存性としてよい)とを有する。同回路は2つのモードで、すなわち少なくとも第一のキャパシタの一端子に入力電圧が提供される第一のモードと、切替装置によって第一及び第二のキャパシタ同士の間で電荷の再配分が起こることにより、第一のキャパシタにかかる電圧が変化し第一のキャパシタの静電容量が減少し、出力電圧が第一のキャパシタにかかる電圧に依存する第二のモードとで、動作可能である。本発明は電圧制御静電容量をキャパシタ間の電荷共有と併せて使用するものであり、これにより、結果的に電圧増幅特性が提供される。よってこの機構は、アナログ電圧の増幅に、または固定レベル(すなわちデジタル電圧)の昇圧に利用できる。よって本発明の回路は、レベルシフトまたは増幅のために、例えばアクティブマトリクスアレイ装置のピクセルでの用途に使用できる。  (もっと読む)

(もっと読む)

トラック/ホールド回路

スイッチ(10)とキャパシタ(12)を備えるトラック/ホールド回路である。第1のブートストラップスイッチ(14a)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第1のブートストラップスイッチ(14a)から出力されるクロック信号clkbootは、スイッチ(10)のゲートに印加される。第1のブートストラップスイッチ(14a)は、電流源(20)という形のレベルシフト手段及びバッファ手段(30)を介して、当該回路の入力Vinと出力Vsとの間に接続されている。第2のブートストラップスイッチ(14b)が設けられており、第2のブートストラップスイッチ(14b)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第2のブートストラップスイッチ(14b)から出力される逆位相クロック信号clknbootは、スイッチ(10)のいずれかの側に接続されている2つのダミースイッチ(16)のゲートに印加される。  (もっと読む)

(もっと読む)

エレクトロルミネッセンス表示パネル駆動回路

【目的】消費電力を節減しICチップへの高密度集積化に適したEL表示パネル駆動回路を提供することにある。

【構成】エレクトロルミネッセンス(EL)表示パネル駆動回路のレベルシフト出力電圧が入力側に帰還されて入力信号INのロウ(L)レベル対応の接地電位を不明確にすることがないように基準電位線を入力側の接地配線GND1と出力側の接地配線GND2とに分離するとともに、出力トランジスタP103/N103駆動用のレベルシフト回路10の前段に補助レベルシフト回路20を配置した。これにより、高圧電源側の接地電位GND2が変動しても高圧側のレベルシフト回路10の誤駆動が回避でき出力トランジスタP103/N103における不要な電流が回避できる。

(もっと読む)

171 - 176 / 176

[ Back to top ]