国際特許分類[H03K17/687]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114) | 装置が電界効果トランジスタであるもの (1,712)

国際特許分類[H03K17/687]の下位に属する分類

制御回路と出力回路の間が電気的に絶縁されたもの

いくつかの入力または出力端子をもつスイッチング装置,例.マルチプレクサ,分配器 (320)

誘導性負荷をもつもの (196)

国際特許分類[H03K17/687]に分類される特許

1,191 - 1,196 / 1,196

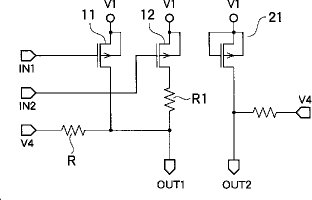

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

Hブリッジ回路における誤動作防止回路

スイッチング電源装置

【目的】 電力変換トランスのスイッチングスピードをより高速化する。

【構成】 PWM発振回路IC2の出力を信号伝達トランスT1に入力し、信号伝達トランスT1の2次側出力をトランジスタTR2,TR3で増幅して、電力変換トランスT2への入力をスイッチングするMOS−FETで構成した電力半導体素子TR4に入力し電力変換トランスT2の2次側から出力させるスイッチング電源装置であって、信号伝達トランスT1の2次側巻線とトランジスタTR2,TR3によって電力増幅する回路とにPch−FETで構成した巻線短絡素子TR1を接続し信号伝達トランスT1へのPWM駆動信号の入力信号状態により信号伝達トランスT1の2次側巻線を短絡状態とする。

(もっと読む)

スイッチング電源装置

ダブルゲート型半導体装置の制御装置

【目的】 高周波に応用においても、スイッチングロスの少ないなどの多くの優れた特性を有するダブルゲート型半導体装置を従来のIGBTなどと同様に1つの制御信号で、確実に制御可能な制御装置を実現する。

【構成】 制御装置20を入力端子P1に入力される制御信号からゲートG1に制御信号を供給する第1ゲート制御回路21と、同じ入力端子P1に入力される制御信号からゲートG2に制御信号を供給する第2ゲート制御回路22とにより構成する。第1ゲート制御回路21には、ディレイ回路31を設置し、ゲートG2にオフ信号が供給されサイリスタ状態からトランジスタ状態に移行した後にゲートG1にオフ信号を供給し、ダブルゲート型半導体装置を確実に停止させる。

(もっと読む)

フローティングウェルCMOS出力ドライバ

【目的】 異なるボルトで作動するよう設計されたチップ同士を簡単にインタフェースさせること。

【構成】 VO−VPがその閾電圧を超えた時にトランジスタQ1がオンになる問題を解決するためにVFGフローティングゲート回路が提供される。VOがバイアス電圧Vdd以下であれば、VFG電圧はVPとなろう。しかし、VOがVddを上回ると、VFG電圧はVOに追従してVOと等しくなる。このように、VFG回路はVOが3.3ボルト以上の論理1である時にトランジスタQ1がオンになることを妨ぐ。同様に、トランジスタQ1の寄生ダイオードの前傾斜の問題を解決するために、VFWフローティングウェル回路を提供する。VOがVdd以下の時は、VFWの電圧はVddと等しい。しかし、VOがVddを上回ると、VFWはVOに追従してVOに等しくなる。VFW回路はVOがVddを上回る論理1である時にトランジスタQ1の寄生ダイオードが前傾斜するのを防ぐ。

(もっと読む)

1,191 - 1,196 / 1,196

[ Back to top ]