国際特許分類[H03K17/693]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114) | 装置が電界効果トランジスタであるもの (1,712) | いくつかの入力または出力端子をもつスイッチング装置,例.マルチプレクサ,分配器 (320)

国際特許分類[H03K17/693]に分類される特許

1 - 10 / 320

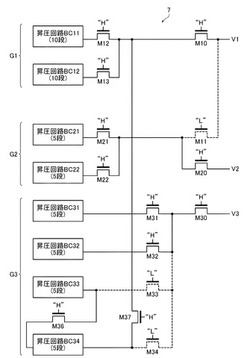

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

高周波半導体スイッチ、端末装置

【課題】スイッチ回路の誤動作の発生を防止する。

【解決手段】一つの実施形態によれば、シリアル・パラレル変換回路は、第一の高電位側電源が供給され、シリアルデータ信号が入力され、パラレルデータ信号を生成する。電源回路は、第二の高電位側電源が供給され、第二の高電位側電源に基づいて第一の正電圧、第二の正電圧、及び負電圧を生成する。ドライブ回路は、第一の正電圧が電源として供給され、パラレルデータ信号が入力されるインバータと、第二の正電圧及び負電圧が電源として供給され、パラレルデータ信号及びインバータの出力信号が入力される差動型レベルシフタを含むレベルシフト回路が設けられ、第二の正電圧をハイレベルの信号としてスイッチ回路に出力し、負電圧をローレベルの信号としてスイッチ回路に出力する。

(もっと読む)

高周波スイッチ

【課題】通過損失を低減するためにオン状態時の抵抗を小さくしても、十分なアイソレーション量を確保する高周波スイッチを得る。

【解決手段】トランジスタ5a,5bのオフ容量Coffと同一の容量Ccを有するクロスカップルキャパシタ8a,8bを設ける。

クロスカップルキャパシタ8a,8bにより、トランジスタ5a,5bのオフ容量Coffをキャンセルすることができるので、アイソレーションを大きく改善することができる。したがって、通過損失を低減するためにトランジスタ5a,5bのオン抵抗Ronを小さくしても、十分なアイソレーション量を確保することができる。

(もっと読む)

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

スタック電圧耐性を高めるためのキャパシタンス調整

【課題】 印加されるRF電圧Vswに制御可能に耐えるRFスイッチ、又はこのようなスイッチの製造方法を提供する。

【解決手段】 スイッチは直列接続された構成FETのストリングを有し、このストリングのノードは隣接するFETの各対の間にある。方法は、各構成FETにわたって分布するRFスイッチ電圧の不一致を減らすよう、容量的にストリングを有効に調整すべくストリングの異なるノードの間のキャパシタンスを制御し、それによって、スイッチ・ブレイクダウン電圧を高める。キャパシタンスは、例えば、ストリングのノードの間に容量特性配置することによって、及び/又は異なる構成FETの設計パラメータを変化させることによって、制御される。各ノードについて、ノードに現れるVswの比率による各有意なキャパシタの積の和は、おおよそ零になるよう制御され得る。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

電子式スイッチ

【課題】半導体スイッチング装置を制御する制御装置の動作用電力を負荷の形態にかかわらず安定に確保し、もって、負荷を安定に制御することが可能な電子式スイッチを提供する。

【解決手段】負荷8がLED電球のように負荷電流が小さく、第2の制御用電源装置15では制御装置9に十分な動作用電力を供給できない場合には、切換え装置16を操作して制御用電源装置10から制御装置9に給電可能にする。本体1の制御電力入力端子13、14に、外部の交流電源17からの給電線を接続する。

(もっと読む)

電源回路、電源回路の信号切替方法、帯電装置、画像形成装置

【課題】負荷の増加に伴い、駆動用ドライバをICの外付け素子として用いる場合でも、専用ICを新たに作成するまたは駆動用ドライバに対するプリドライバおよび端子を別途設けることなく、ICと出力端子を共用することで設計およびチップ製作にかかるコストを低減する。

【解決手段】入力信号2,3を切替選択信号22によって切り替え、出力信号13〜16を出力する信号切替ブロック12と、出力信号13〜16をそれぞれチャンネルの異なるスイッチング素子に入力する複数のD級アンプと、を備え、信号切替ブロック12は、複数のD級アンプを、負荷を駆動するための駆動用ドライバ、または外付けされた駆動用ドライバ回路に対するプリドライバとするかを前記切替選択信号により切り替える。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】電源回路と、駆動回路と、スイッチ部と、第1の電位制御回路と、を備えた半導体スイッチが供給される。前記電源回路は、負の第1の電位を生成する第1の電位生成回路と、電源電位を降圧した正の第2の電位を生成する第2の電位生成回路と、を有する。前記駆動回路は、前記第1の電位と第3の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第3の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて複数の高周波端子のいずれか1つに共通端子を接続する。前記第1の電位制御回路は、第1のトランジスタを有する分割回路と、第2のトランジスタを有する増幅回路と、を有する。

(もっと読む)

半導体スイッチ回路

【課題】簡易な構成によりスイッチ切替時間のさらなる高速化を図る。

【解決手段】外部から供給される外部制御信号に応じて、高周波スイッチ回路101のFET1,2のオン、オフ状態を制御する駆動制御信号を出力する論理制御回路104と、FET1,2が論理制御回路104によりオフ状態からオン状態とされる際にパルス電圧を出力する切替加速回路102,103とは、それぞれの出力信号が共にFET1,2の駆動制御信号として、それぞれへ印加可能に設けられ、論理制御回路104は、定常状態においてFET1,2をオン状態とする電源電圧とほぼ等しい駆動制御信号を出力するよう構成され、切替加速回路102,103は、ピークが電源電圧を超えるパルス電圧を出力する一方、そのパルス電圧が論理制御回路104の出力信号の電圧レベルを下回った際には、その出力が遮断されるよう構成されたものとなっている。

(もっと読む)

1 - 10 / 320

[ Back to top ]