国際特許分類[H03K23/42]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 計数連鎖を包含するパルス計数器;計数連鎖を包含する周波数分割器 (291) | ゲート信号またはクロック信号がすべての段に印加されるもの,すなわち.同期形計数器 (94) | 位相ずれのゲートまたはクロック信号が計数段に印加されるもの (39)

国際特許分類[H03K23/42]の下位に属する分類

電界効果トランジスタを用いるもの (31)

電荷転送デバイス,すなわち,BBD,CCDを用いるもの

国際特許分類[H03K23/42]に分類される特許

1 - 8 / 8

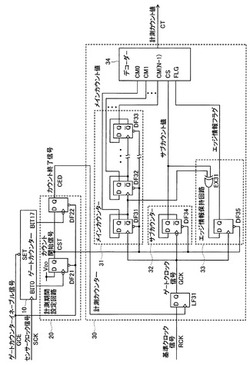

カウンター回路

【課題】回路規模及び/又は消費電力を従来よりも低減しながら、倍精度の計測を行うカウンター回路を実現する。

【解決手段】このカウンター回路は、計測期間において、クロック信号の立ち上がりエッジに同期してパルス数をカウントすることにより、第1カウント値を生成する第1の回路と、計測期間において、クロック信号の立ち下がりエッジに同期してパルス数をカウントすることにより、第2カウント値を生成する第2の回路と、計測期間におけるクロック信号の立ち上がりエッジと立ち下がりエッジとの前後関係を表すフラグ情報を保持する第3の回路と、フラグ情報に従って第1カウント値及び第2カウント値をデコードすることにより、クロック信号の周期に対して倍精度の計測カウント値を出力する第4の回路とを含む。

(もっと読む)

分周回路、分周装置及び電子機器

【課題】位相同期した出力信号及びその反転信号を生成・出力できる分周回路の実現。

【解決手段】分周回路1は、クロック信号生成部10と、分周信号生成部20と、出力信号生成部30とから構成される。出力信号生成部30からは、共通のクロック信号CLOCKによって動作/不動作が切り替えられるクロックドインバーターX15,X19によって、位相がほぼ完全に一致した出力信号OUT,XOUTが生成・出力される。

(もっと読む)

同期出力を有する周波数分周器

【解決手段】周波数でクロック信号を分周し、優れた信号特性を有する差動信号を供給し得る分周器が記述される。1つの典型的な設計では、分周器はシングルエンド分周器及び同期回路を含む。シングルエンド分周器は、周波数でクロック信号を分割し、タイミングスキューを有する相補型信号である第1及び第2信号を供給する。同期回路は、クロック信号に基づき第1、第2信号をリサンプリングし、低減したタイミングスキューを有する差動信号を供給する。1つの典型的な設計では、同期回路は第1及び第2スイッチ、並びに第1及び第2インバータを含む。第1スイッチ及び第1インバータによって第1サンプリング−保持回路又は第1信号をリサンプリングする第1ラッチが形成される。第2スイッチ及び第2インバータによって、第2サンプリング−保持回路又は第2信号をリサンプリングする第2ラッチが形成される。 (もっと読む)

高速カウントを生成するための方法および回路

【課題】メモリデバイスでの動作タイミングを制御するための複数のビットを伴うデジタルカウントを生成する、高速計数回路

【解決手段】計数回路は、2つの位相シフトクロックによって駆動される一連のレジスタを含む。計数回路中のクロックジェネレータは、各レジスタを駆動するための4つの非対称クロック信号を生成する。レジスタは、入力および出力ステージから形成され、各ステージは、2組のスイッチを備える。各ステージ中の第1の組のスイッチは、非対称クロックに応答して、ステージ出力に供給電圧を与える。第2の組のスイッチは、非対称クロックに応答して、グラウンドをステージ出力に与える。スイッチング回路の応答を速めるために、第2の組のスイッチの切換え中に、分離スイッチが、各対における第1の組のスイッチをステージ出力から減結合し、その結果、第2の組のスイッチによるステージ出力の負荷を除去する。

(もっと読む)

直交クロック分周器

n分周プロセスは、4/nスケールプロセス(110,210,310)及び後続する4分周プロセス(120,220,320)によって行われる。直交入力クロックは、クロック位相選択プロセスによって、4/nスケールプロセスを容易にする。終わりの4分周プロセスを組み込むことによって、直交出力信号は簡単に供給される。3分周直交分周器は、3つごとの直交クロック位相の選択によって4/nスケールプロセスを行い、4分周プロセスの直交出力は、この3つごとのクロック位相選択を行うために制御信号を供給する。  (もっと読む)

(もっと読む)

カウンタ及びこれを含む光学式測定装置

【課題】 回路規模を大きくせずに計数の高速化が可能なカウンタを提供する。

【解決手段】 レーザ走査型の光学式測定装置に組み込まれるカウンタ41は、位相分割方式で下位ビットデータD0〜D2が生成され、単相方式で中位ビットデータD3及び上位ビットデータD4〜D15が生成される。下位ビットデータ生成部61は、互いに異なる位相のクロック信号CK1〜CK4がクロック入力に加えられる初段の四つのフリップフロップ及2段目の四つのフリップフロップ備え、加算回路ADDで得られる0〜4までの値と、減算回路SUBで得られる5〜7までの値をセレクタ回路SELで選択して、下位ビットデータD0〜D2である0〜7までの値を得る。

(もっと読む)

高周波数カウンタ回路

【課題】 より高いクロック周波数で動作可能なカウンタ回路を提供する。

【解決手段】 より高いクロック周波数での動作を可能とするために、入力信号をカウントする第1のカウンタ回路1及び第2のカウンタ回路2と、第1のカウンタ回路1の出力信号と第2のカウンタ回路2の出力信号とを切替えるためのカウンタ出力切替回路3と、によってカウンタ回路を構成する。

(もっと読む)

分周器及びそれを備えた携帯機器

【課題】 位相誤差・振幅誤差発生の原因となる電圧−電流変換部を共通化することにより、回路構成による出力誤差発生の確率を低減し得る分周器を提供する。

【解決手段】 差動対を成すTr(トランジスタ)Q1・Q2を用いて電圧信号であるクロック信号CLK1とその相補信号であるクロック反転信号CLK2とを電流信号に変換する電圧−電流変換部11と、TrQ1から出力される電流信号i101を入力して互いに180度位相の異なる2つの第1の信号・第2の信号をそれぞれ生成するTrQ11・Q12及びTrQ5・Q6と、TrQ2から出力される電流信号i102を入力して互いに180度位相の異なる2つの第3・第4の信号をそれぞれ生成するTrQ9・Q10及びTrQ7・Q8とを備えたI−Q信号生成部12とを備える。I−Q信号生成部12の第1・第3の信号の位相差が90度であり、第2・第4の信号の位相差が90度である。

(もっと読む)

1 - 8 / 8

[ Back to top ]