国際特許分類[H03K23/44]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 計数連鎖を包含するパルス計数器;計数連鎖を包含する周波数分割器 (291) | ゲート信号またはクロック信号がすべての段に印加されるもの,すなわち.同期形計数器 (94) | 位相ずれのゲートまたはクロック信号が計数段に印加されるもの (39) | 電界効果トランジスタを用いるもの (31)

国際特許分類[H03K23/44]に分類される特許

1 - 10 / 31

半導体装置

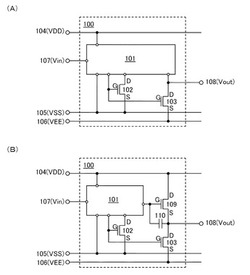

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

分周回路

【課題】分周回路の動作不良を抑制する。

【解決手段】第1又は第2のクロック信号に従って2×X個(Xは2以上の自然数)のパルス信号を生成して出力するシフトレジスタと、2×X個のパルス信号に従って、第1のクロック信号の周期のX倍の周期である第3のクロック信号となる信号を生成して出力する分周信号出力回路と、を具備し、分周信号出力回路は、ゲートのそれぞれに、2×X個のパルス信号における1個目乃至X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第1の電圧に設定するか否かを制御するX個の第1のトランジスタと、ゲートのそれぞれに、2×X個のパルス信号におけるX+1個目乃至2×X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第2の電圧に設定するか否かを制御するX個の第2のトランジスタと、を備える。

(もっと読む)

半導体装置及び電子機器

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジス

タを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、出力端子と接続するノード

を構成するトランジスタのチャネル長を、出力端子として機能するトランジスタのチャネ

ル長よりも大きくする。これによって、該ノードからの電流のリークを抑制して、長期間

にわたって安定して電位を保持することが可能となり、パルス信号出力回路の誤作動を防

止することができる。

(もっと読む)

シフト・レジスタユニット、ゲート駆動回路及び表示装置

【課題】瞬時電流を低減し、シフト・レジスタユニットの消費電力を低減する。

【解決手段】本発明のシフト・レジスタユニットは、第1のクロック信号、第2のクロック信号、フレームスタート信号、高電圧信号および低電圧信号を入力する入力モジュールと、入力モジュールに接続され、複数の薄膜トランジスタを含み、第1のクロック信号、第2クロック信号およびフレームスタート信号に基づいてゲート駆動信号を生成し、薄膜トランジスタが形成した第1のノードのシフト・レジスタユニットの値を求める段階における電圧を電源信号のローレベルより低くなるよう制御し、薄膜トランジスタが形成した第2のノードをリセットするよう制御することを特徴とする。

(もっと読む)

分周回路

【課題】分周回路の動作不良を抑制する。

【解決手段】第1又は第2のクロック信号に従って2×X個(Xは2以上の自然数)のパルス信号を生成して出力するシフトレジスタと、2×X個のパルス信号に従って、第1のクロック信号の周期のX倍の周期である第3のクロック信号となる信号を生成して出力する分周信号出力回路と、を具備し、分周信号出力回路は、ゲートのそれぞれに、2×X個のパルス信号における1個目乃至X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第1の電圧に設定するか否かを制御するX個の第1のトランジスタと、ゲートのそれぞれに、2×X個のパルス信号におけるX+1個目乃至2×X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第2の電圧に設定するか否かを制御するX個の第2のトランジスタと、を備える。

(もっと読む)

電気光学装置、シフトレジスタ回路および半導体装置

【課題】ゲート線駆動回路の領域を効率よく利用できると共に、ゲート線選択信号の立ち上がり速度の低下(立ち上がり遅延)を防止できる電気光学装置、並びに、それに適した単一導電型のトランジスタで構成されたシフトレジスタ回路を提供する。

【解決手段】ゲート線駆動回路30は、複数のゲート線GLの奇数行を駆動する奇数ドライバ30aと、偶数行を駆動する偶数ドライバ30bとから成る。奇数および偶数ドライバ30a,30bの単位シフトレジスタSRの各々は、2行前の選択信号Gk-2を受け、その2水平期間遅れて自己の選択信号Gkを活性化させる。偶数ドライバ30bのスタートパルスSP1は、奇数ドライバ30aのスタートパルスSP2よりも1水平期間だけ位相が遅れている。

(もっと読む)

集積回路装置及び電子機器

【課題】 シリアルデータの遅延時間を減少可能な集積回路装置等を提供する。

【解決手段】 集積回路装置10は、第1〜第N(Nは2以上の整数)のレジスター121、・・・、12Nを有するシフトレジスター18であって、シリアルデータSDを入力し、第1〜第Nのレジスター121、・・・、12Nを介してシリアルデータSDを出力するシフトレジスター18と、シフトレジスター18の出力SRを保持し、シリアルデータSDを出力する専用レジスター19と、を含む。集積回路装置10は、専用レジスター19を介してシリアルデータSDを、カスケード接続される他の集積回路装置に出力信号SOとして出力する。

(もっと読む)

パルス出力回路、シフトレジスタ

【課題】薄膜トランジスタの特性劣化の程度を小さくし、回路内の誤動作を低減し、より確度の高い動作を保証する駆動回路を提供する。

【解決手段】シフトレジスタに設けられたパルス出力回路において、パルスの出力が行われない非選択期間、ゲート電極がオンするように浮遊状態となっているトランジスタのゲート電極が接続されたノードに対し、クロック信号がトランジスタのゲート電極に入力されるように設けることで、定期的に電位を供給する。また、ブートストラップ動作を行うトランジスタのゲートにゲートが固定電位に接続されたトランジスタを設ける。

(もっと読む)

1 - 10 / 31

[ Back to top ]