エヌエックスピー ビー ヴィにより出願された特許

21 - 30 / 125

炭化ケイ素MOSFETの反転層移動度を改善する方法

SiC基板(12)に基づいて半導体デバイスを製造する方法であって、5×1011cm−2未満の界面近傍トラップ密度を達成するのに十分に高い酸化速度でSiC基板(12)のSi終端面上に酸化物層(14)を形成するステップ(201)と、酸化物形成のステップで形成された深いトラップを不活性化し、それによって、改善された反転層移動度と低減された閾値電圧とを有するSiCベースMOSFET(10)の製造を可能にするために、酸化されたSiC基板を水素含有環境でアニールするステップ(202)とを備える方法。SiC基板のSi面が迅速な酸化を受けると、DTの密度は増加するが、NITの密度は減少することが本発明者等によって見いだされた。本発明によれば、迅速な酸化中に形成された深いトラップは水素アニーリングによって不活性化され、それにより、酸化物上に形成された半導体デバイスの閾値電圧は著しく低減され得る。  (もっと読む)

(もっと読む)

無線装置の自動利得制御における、またはそれに関する改善

RF増幅器(38)に接続されたプログラマブル減衰器(36)を備える第1のRF利得ステージ(34)と、所望の帯域幅において信号を増幅するための第2の挟帯域利得制御増幅ステージ(24)と、を有するRF装置を動作させる方法は、所望の信号内の合計雑音を最小化することによって信号対雑音(SNR)を最大化する、第1のRF利得ステージの利得設定と、実質的に一定レベルの出力を供給する、第2の挟帯域増幅ステージの利得設定と、を選択することを含む。第1のRF利得ステージの利得設定を選択するために、RFデバイスは、合計雑音を最小化するようにプログラマブル減衰器に印加される利得設定を選択する際に、第1のRFステージおよび第2の利得制御増幅ステージの利得設定と、歪み雑音(RF入力を参照する)と、熱雑音(RF入力を参照する)とを考慮に入れる制御ステージ(40)を含む。  (もっと読む)

(もっと読む)

電気音響変換器

レーザ源Aと受光器Hとを備える電気音響変換器であって、音場Sが設けられ、音場Sが、レーザ・ビームが音場Sを通過するときにビームの伝搬速度を音圧に従って変調するのに使用されてよい電気音響変換器が提供される。  (もっと読む)

(もっと読む)

音響装置とその製造方法

変換素子(503)を備える振動膜(501)と、収容面に膜(501)を収容するように適合されたフレーム(504)とを備える音響装置(500)であって、この収容面の少なくとも1つの方向に膜(501)の並進運動が可能とされるように膜(501)がフレーム(504)の中に収容される音響装置。  (もっと読む)

(もっと読む)

固体電池を備えるチャージ・ポンプDC−DCコンバータ

DC−DCコンバータを備える電子装置が提供される。DC−DCコンバータはDC−DC変換用にエネルギーを蓄積するための少なくとも1つの固体二次電池(B1、B2)と、出力キャパシタ(C2)とを備える。  (もっと読む)

(もっと読む)

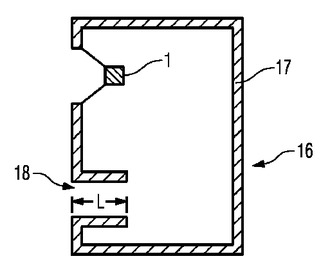

ロッキング傾向を減少させたスピーカ

スピーカ(13, 16) が、エレクトロダイナミック変換器(1) 及びこの変換器を収納したバスレフ型エンクロージャ(14, 17)を有する。変換器のダイヤフラム(2) は、駆動時にロッキング振動数のロッキングモードで振動し、バスレフ型エンクロージャ(14,17) は、ロッキング振動数に同調される。  (もっと読む)

(もっと読む)

静電容量MEMSセンサデバイス

本発明は、力学的量を検知する静電容量MEMSセンサデバイスに関する。機械的過負荷状況後の(近接)付着からの急速回復を可能にする、このような静電容量MEMSセンサデバイスを提供するために、第1のバイアス電圧(Vbias1)を、MEMS検知素子の第1のプレートに供給する第1のバイアス電圧ユニット(V1)と、第2のバイアス電圧(Vbias2)を、MEMS検知素子の第2のプレートに供給する第2のバイアス電圧ユニット(V2)と、電気量を処理して出力信号(Vout)にする信号処理(20)ユニットと、MEMS検知素子(10)の過負荷状態の検出のために、出力(Vout)信号を、基準信号(Vref)と比較するとともに、比較器信号を出力する比較器ユニット(21)と、過負荷状態の場合に、第1の時間間隔(T1)中に第1のプレートを第1の放電端子(D)に、および第2の時間間隔中(T2)に第2のプレートを第2の放電端子(D)に接続することによって、比較器信号により示された過負荷状態の場合に、MEMS検知素子(10)の放電を制御する制御ユニット(22)と、を備える、センサデバイスが提案されている。  (もっと読む)

(もっと読む)

ノイズ分散を推定するための方法および装置

本発明は、直交拡散符号による符号多重通信システムの受信機におけるノイズ分散を推定するための方法および装置に関し、実質的に同一の振幅を有する2つの推定されるシンボルの和および差の各実数部および虚数部を決定し、決定した和および差の実数部および虚数部の各最小エネルギー成分を決定する。各最小エネルギー成分を最終的に組み合せてノイズ分散を得る。それによって、ノイズ分散を加算および比較の操作だけに基づいて推定することができ、複雑さと処理負荷を軽減させることができる。  (もっと読む)

(もっと読む)

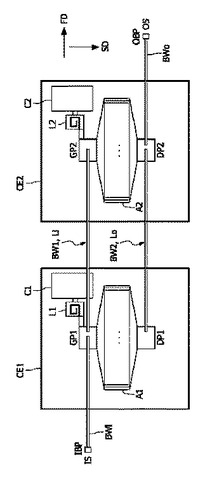

高出力集積RF増幅器

入力ボンド・パッド(IBP)と第1の方向(FD)に互いに変位された複数のセル(CE1、CE2)と出力ボンド・パッド(OBP)とをこの順序で第1の方向(FD)に備えた集積HF増幅器構造体。セル(CE1、CE2)の各々は入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)とを有する増幅器を備える。アクティブ領域(A1、A2)は、入力パッド(GP1、GP2)と出力パッド(DP1、DP2)の間に配置され、入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)は第1の方向(FD)に対してほぼ直角な第2の方向(SD)に互いに変位される。第1の回路網(N1)は、複数のセル(CE1、CE2)のうちの隣接するセルの入力パッド(GP1、GP2)を相互接続するための第1の相互接続手段(Li、Ci;Li1、Li2、Ci1)を備え、且つ第1の方向(FD)に延びる。第2の回路網(N2)は、複数のセル(CE1、CE2)のうちの隣接するセルの出力パッド(DP1、DP2)を相互接続するための第2の相互接続手段(Lo、Co;Lo1、Lo2、Co1)を備え、且つ第1の方向(FD)に延びる。第1の回路網(N1)及び第2の回路網(N2)は、すべての相互接続されたセル(CE1、CE2)について、出力ボンド・パッド(OBP)にて、入力ボンド・パッド(IBP)での同じ入力信号(IS)に対して等しい位相シフト及び振幅を有する出力信号(OS)を得るように構成される。特定のバイアス及び位相シフト条件において、構造体は出力バックオフでの効率が改善されたドハティ増幅器を実現する。  (もっと読む)

(もっと読む)

ドハティ増幅器

集積ドハティ増幅器構造体は、入力ボンドパッド(IBP)と、出力ボンドパッド(OBP)とを備える。第1のトランジスタ(T1)は、ドハティ増幅器のピーク増幅段を形成し且つドハティ増幅器の入力信号である第1の入力信号(IS1)を受け取るための制御入力(G1)とドハティ増幅器の出力で増幅された第1の入力信号(OS1)を供給するための出力(D1)とを有する。第2のトランジスタ(T2)は、ドハティ増幅器のメイン増幅段を形成し且つ第2の入力信号(IS2)を受け取るための制御入力(G2)と増幅された第2の入力信号(OS2)を供給するための出力(D2)とを有する。第1の入力信号(IS1)と第2の入力信号(IS2)とは90度の位相オフセットを有する。第1のボンドワイヤ(BW1)は、第1のインダクタンス(L1)を形成し、第1の方向に延在するとともに、入力ボンドパッド(IBP)と第1のトランジスタ(T1)の制御入力(G1)との間に配置される。第2のボンドワイヤ(BW2)は、第2のインダクタンス(L2)を形成し、第1の方向に延在するとともに、出力ボンドパッド(OBP)と第1のトランジスタ(T1)の出力(D1)との間に配置される。第3のボンドワイヤ(BW3)は、第3のインダクタンス(L3)を形成し、第1の方向に対して略垂直な第2の方向に延在するとともに、第1のトランジスタ(T1)の出力(D1)と第2のトランジスタ(T2)の出力(D2)との間に配置される。  (もっと読む)

(もっと読む)

21 - 30 / 125

[ Back to top ]