インターナショナル・ビジネス・マシーンズ・コーポレーションにより出願された特許

3,021 - 3,030 / 4,084

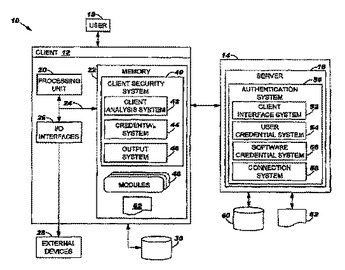

クライアントをネットワークに接続する方法、システム、及びプログラム製品

本発明では、接続が許可される前にユーザ・クレデンシャル及びソフトウェア・クレデンシャルの両方が認証される。この点で、1つ以上のユーザ・クレデンシャルがクライアントで(例えば、ユーザから)受け取られる。その後、通常はクライアント上で動作するソフトウェア・エージェントは、所要ソフトウェア・モジュールのリストにおいて特定されている1つ以上のソフトウェア・モジュールがクライアントにインストールされているか否かを判定する。クライアントにインストールされている各ソフトウェア・モジュールについて、そのエージェントはソフトウェア・クレデンシャルを生成する。ユーザ・クレデンシャルとソフトウェア・クレデンシャルとはサーバに送られ、これは、ユーザ・クレデンシャルが有効であって所要ソフトウェア・モジュールのリストにおいて特定されている各ソフトウェア・モジュールについて有効なソフトウェア・クレデンシャルが提供されるならば接続を許可する。  (もっと読む)

(もっと読む)

アプリケーション環境に基づいて、ウィンドウIDを動的にプログラミングするための装置及び方法

【課題】 カラー・バッファ及びオーバーレイ・バッファの各々についてのWIDを識別するのに用いられるビット数を、その時点でアクティブなアプリケーション環境に基づいてグラフィックス・アダプタにプログラムすることができる機構を提供する。

【解決手段】 本発明の装置及び方法を用いて、プログラム可能WATカラー・サイズ選択装置が、グラフィックス・アダプタのRAMDAC内に構成される。このプログラム可能WATカラー・サイズ選択装置は、WIDバッファからのWIDの様々なビット分割を用いてカラーWATテーブル及びオーバーレイWATテーブルへの異なる索引を取得するように、動的にプログラムすることができる。このように、例えば8ビットWIDの異なる分割を、プログラム可能WATカラー・サイズ選択装置の設定に基づいて取得し、様々なカラー及びオーバーレイ能力が動的に得られるようにすることができる。  (もっと読む)

(もっと読む)

拡大縮小可能ななマルチプロセッサコンピュータの効率的な仮想タイムベースのための方法、機器、およびプログラム

【課題】データ処理システムにおいて、論理的に分割したデータ処理システムの仮想タイムベースを提供するための方法、機器、およびコンピュータプログラム製品を提供する。

【解決手段】複数のプロセッサコアの各々についてタイムベースを判定する。このタイムベースを使って、タイムベースを判定するプロセッサコアのうちのひとつに現在の時間を示す。プロセッサコアの各々が同期タイムベースのそれ自身のコピーを備えるように、プロセッサコアのタイムベースを互いに同期させる。プロセッサコアのうちのひとつについて、同期タイムベースとは異なるが、同期タイムベースの少なくとも一部とは同期したままの仮想タイムベースを生成する。プロセッサコアは、プロセッサコアに現在の時間を示すために、同期タイムベースの代わりに仮想タイムベースを利用する。同期タイムベースと仮想タイムベースの一部は互いに同期したままである。

(もっと読む)

カレンダーおよびスケジューリング・アプリケーションでの複数の時間帯の視覚化

【課題】 C&Sアプリケーションと、C&Sアプリケーションが管理するイベント・スケジュールと、C&Sアプリケーションに結合している複数の時間帯処理ロジックとを含むことができる複数の時間帯を視覚化するための方法、システムおよび装置を提供する。

【解決手段】 複数の時間帯処理ロジックは、定義したイベントへの各参加者の時間帯を決定することができる。複数の時間帯処理ロジックは、さらに、各参加者の定義したイベントに対する好適な時間に対応する決定した時間帯での現地時間を示すユーザ・インタフェースを提供することができる。例えば、ユーザ・インタフェースは、各参加者に対する並置した時間の範囲の配置を含むことができる。この場合、各時間の範囲に対する現地時間が、好適な時間に対応するように、時間の範囲はずれた外観を有する。

(もっと読む)

画像表示システム、および画像表示装置

【課題】ホストからディスプレイ方向へ大容量からなる画像データの転送と、その逆方向のはるかに少量のデータ転送とを最大限の効率で実現する。

【解決手段】アプリケーションを実行するホスト側10と、このホスト側10に接続されたディスプレイ側30と、ホスト側10とディスプレイ側30とを接続するインターフェイスを備え、ディスプレイ側30に対して画像を表示するための画像表示システムであって、このインターフェイスは、ホスト側10からディスプレイ側30に対して大容量のデータ転送を実行するデジタルI/F50と、ディスプレイからホストに対して、第1のインターフェイスの容量よりも遥かに少ないがゼロではない小容量のデータ転送を実行するための制御信号線60とを備え、デジタルI/F50は、データをパケット化して転送する。

(もっと読む)

同時マルチスレッド(SMT)プロセッサにおいてスレッドごとのプロセッサ・リソース使用率を決定するためのアカウンティング方法および論理

【課題】 SMTプロセッサにおけるプロセッサ時間使用率をアカウントすることが可能な方法および装置を提供すること。

【解決手段】 同時マルチスレッド(SMT)プロセッサ内でのスレッドごとのプロセッサ・リソース利用を決定するためのアカウンティング方法および論理回路は、プログラムおよびプログラム内のスレッドによるプロセッサ・リソース使用率をアカウントするためのメカニズムを提供する。相対的なリソースの使用は、依然としてプロセッサ・リソースを占有しているアイドル状態のスレッドを含む場合のある、プロセッサ内でアクティブな複数のスレッドに対する命令ディスパッチを検出することによって決定される。命令がすべてのスレッドにディスパッチされている場合、またはどのスレッドにもディスパッチされていない場合、プロセッサ・サイクルはすべてのスレッドに対して均等にアカウントされる。別の方法では、どのスレッドもディスパッチ状態にない場合、アカウンティングは以前の状態を使用して行われるか、またはスレッドの優先順位レベルの比率に合わせて行われる。1つのスレッドのみがディスパッチしている場合、そのスレッドにプロセッサ・サイクル全体がアカウントされる。複数のスレッドがディスパッチしているが、(2つより多くのスレッドをサポートしているプロセッサにおいて)ディスパッチしているのがすべてのスレッドではない場合、プロセッサ・サイクルはディスパッチしているスレッドにまたがって均等に請求される。スレッドについて複数のディスパッチが検出され、各スレッドに対して分数のリソース使用率を決定する場合があり、カウンタはそれらの分数の使用率に従って更新することができる。  (もっと読む)

(もっと読む)

直接実行機能を提供するためのシステム、コンピュータシステム、方法およびプログラム

【課題】直接実行機能をインプリメントするためのオペレーティングシステムを開示する。

【解決手段】オペレーティングシステムは、直接実行機能をインプリメントするための以下の新規で独創的な機能コンポーネント: メモリ/ファイルマネジャと少なくとも1個のファイルシステムドライバとの間のファイルシステムのダイレクトアクセスインターフェースであって、ファイルシステムのダイレクトアクセスインターフェースが、指定オフセットにおける指定ファイルの内容のシステムメモリアドレスを検索する機能を提供するファイルシステムのダイレクトアクセスインターフェースと、 少なくとも1個のファイルシステムドライバと、少なくとも1個のメモリアドレス指定デバイスに対するアクセスを提供する少なくとも1個のデバイスドライバとの間のデバイスダイレクトアクセスインターフェースである。

(もっと読む)

改善されたセル安定性及び性能のためのハイブリッド・バルク−SOI6T−SRAMセル

【課題】 改善されたセル安定性及び性能を示すハイブリッド・バルクSOI 6T STRAMセルを提供すること。

【解決手段】 本発明は、同じ結晶配向又は異なる結晶配向を有するSOI領域及びバルク−Si領域を含む基板と、バルク−Si領域からSOI領域を分離する分離領域と、SOI領域内に配置された少なくとも1つの第1デバイス及びバルク−Si領域内に配置された少なくとも1つの第2デバイスとを含む、6T−SRAM半導体構造体を提供する。SOI領域は、絶縁層の上にシリコン層を有する。バルク−Si領域はさらに、第2デバイスの下にあるウェル領域と、浮遊体効果を安定化させる、ウェル領域へのコンタクトとを含む。ウェル・コンタクトはまた、バルク−Si領域内のFETの閾値電圧を制御して、SOI領域のFET及びバルク−Si領域のFETの組み合わせから構築されたSRAMセルのパワー及び性能を最適化するためにも用いられる。

(もっと読む)

相互接続構造体及びその製造方法

【課題】 改善された拡散障壁で覆われた相互接続構造体を提供すること。

【解決手段】 ダマシン配線及び該配線を形成する方法である。この方法は、誘電体層の上面にマスク層を形成するステップと、マスク層内に開口部を形成するステップと、誘電体層がマスク層によって保護されていない誘電体層内に、トレンチを形成するステップと、マスク層の下でトレンチの側壁を凹ませるステップと、トレンチ及びマスク層の全ての露出面上に、共形の導電性ライナを形成するステップと、トレンチをコア導電体で充填するステップと、誘電体層の上面の上に延びている導電性ライナの部分を除去し、マスク層を除去するステップと、コア導体の上面に導電性キャップを形成するステップとを含む。この構造体は、導電性ライナ内のコア導体クラッドと、導電性ライナで覆われていないコア導体の上面と接触している導電性キャップ層と、を含む。

(もっと読む)

共有リソースの同時アクセス

【課題】 マルチスレッド化されたコンピュータにおいて実行される多数のスレッド又はプロセスによる共有リソースへのアクセスを調整する改善された方法を提供する。

【解決手段】 共有リソースを使用する要求を受け取る順番と、こうした要求を受け取った後にそれらの要求の処理が完了する順番との両方を追跡するアトミック・オペレーションの効果的な組み合わせにより、マルチスレッド化されたコンピュータにおける複数のプロセスによる共有リソースへのアクセスを管理する装置、プログラム及び方法である。要求のディスパッチは、最近完了された要求より前に受け取った、ディスパッチされていない要求の処理が完了するまで、効果的に据え置かれる。多くの場合、要求の処理の完了は、非アトミックに行うことができ、それにより共有リソースに関して生じる競合が減少する。さらに、要求のディスパッチは、個々のディスパッチ動作に関連するオーバーヘッドを減少させるためにバッチで行われてもよい。  (もっと読む)

(もっと読む)

3,021 - 3,030 / 4,084

[ Back to top ]