ザインエレクトロニクス株式会社により出願された特許

1 - 10 / 61

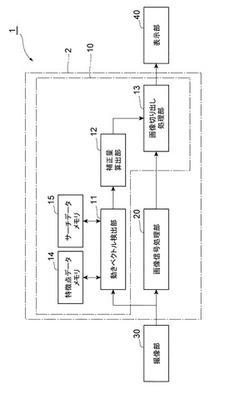

手振れ補正処理装置および手振れ補正処理方法

【課題】フレームメモリを使用することなく手振れ補正処理を行うことが可能な手振れ補正処理装置を提供する。

【解決手段】手振れ補正処理装置10は、動きベクトル検出部11,補正量算出部12,画像切り出し処理部13を含む。動きベクトル検出部は、画像フレームF(n)の画素データを入力する際の初期期間に入力した第1エリアの画素データと、画像フレームF(n−1)中の第1エリアの特徴点に関する情報とに基づいて、期間T(n)の画像の動きベクトルを検出する。補正量算出部は、動きベクトル検出部により検出された画像の動きベクトルに基づいて画像フレームF(n)についての切り出し位置を算出する。画像切り出し処理部は、補正量算出部により算出された切り出し位置に基づいて、画像信号処理部20から出力された画像フレームF(n)中の部分範囲の画素データを切り出す。

(もっと読む)

半導体記憶装置およびデータ書込み方法

【課題】MOS構造を有する各メモリセルにおいて信頼性が高い2ビットのデータの記憶が容易な半導体記憶装置およびデータ書込み方法を提供する。

【解決手段】MOS構造を有するメモリセル10は、ゲート電極13の第1半導体領域121側に設けられた第1記憶部141と、ゲート電極13の第2半導体領域122側に設けられた第2記憶部142とを有する。第1記憶部141に電子を保持させる第1電荷移動ステップと、第2記憶部142に電子を保持させる第2電荷移動ステップとを交互に行うことで、第1記憶部141および第2記憶部142の双方に所定量の電子を保持させる。

(もっと読む)

送信装置、受信装置および送受信システム

【課題】符号化処理と復号化処理との間の同期をより確実なものとして受信エラーを抑制することができる送受信システムを提供する。

【解決手段】送受信システム1Aは送信装置10Aおよび受信装置20Aを備える。送信装置10Aは、符号化部11、シリアライザ12および送信部13を備える。受信装置20Aは、復号化部21、デシリアライザ22、受信部23、エラー検出部24及びリセット指示部25を備える。符号化部11は、符号化部11の符号化処理と復号化部21の復号化処理との間の同期を確立するための同期信号(符号復号同期信号)を符号化データとして定期的に送信部13から受信装置20Aへ送信させる。符号化部11は、リセット指示信号を受信装置20Aのリセット指示部25から受け取ったときにも、符号復号同期信号を符号化データとして送信部13から受信装置20Aへ送信させる。

(もっと読む)

レベルシフト回路

【課題】更なる消費電力低減および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2Aは、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41および第2NMOSトランジスタ42を備える他、第3NMOSトランジスタ43および第4NMOSトランジスタ44をも備える。第1PMOSトランジスタ31および第2PMOSトランジスタ32それぞれのソース端子は、第1基準電位Vddlより高い第2基準電位Vddhに接続される。第3NMOSトランジスタ43および第4NMOSトランジスタ44それぞれのドレイン端子も第2基準電位Vddhに接続される。

(もっと読む)

送信装置および送受信システム

【課題】受信装置の終端抵抗器の抵抗値がばらついている場合であっても安定した通信を行うことができる送信装置を提供する。

【解決手段】送信装置10Aは、第1トランジスタ11、第2トランジスタ12、電流源13、送信回路14、差演算部15および電流調整部16を備える。トランジスタ11,12は差動対を構成している。差演算部15は、トランジスタ11,12のうちの一方がオン状態で他方がオフ状態であるときの第1出力端10aおよび第2出力端10bそれぞれからの出力電圧値を入力して、これら2つの出力電圧値の差(対象電圧)を求める。電流調整部16は、この対象電圧を入力するとともに、参照電圧入力端10dに入力された参照電圧を入力して、参照電圧に基づいて対象電圧を評価し、その評価結果に基づいて、対象電圧が目標値または目標範囲内となるように電流源13の出力電流値を調整する。

(もっと読む)

保護回路

【課題】より効果的に逆起電圧の発生を抑え、過電圧による素子の破壊を防ぐことが可能な保護回路を提供する。

【解決手段】第1の実施形態の保護回路2は、抵抗値可変スイッチ10,過電流検出部20,制御電圧印加部30,容量部40,制御端子電圧変更部50および外部端子11を備える。抵抗値可変スイッチ10は、制御端子10a,第1端子10bおよび第2端子10cを有する。制御端子電圧変更部50は、抵抗値可変スイッチ10の制御端子10aと基準電位端子との間に直列的に設けられたスイッチ51および抵抗器52を含む。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

送信装置、受信装置および送受信システム

【課題】回路規模の増大を抑制しつつEMIノイズの低減を図ることができる送信装置を提供する。

【解決手段】送信装置10Aは、送信データ生成部11および出力バッファ部12Aを備える。送信データ生成部11は、受信装置へ送出すべきデータdata1およびクロックclock1を生成し、これらを出力バッファ部12Aへ出力する。出力バッファ部12Aは、データ送信部13およびクロック送信部14Aを含む。クロック送信部14Aは、間欠的に位相シフトを与えられたクロックを生成して送出する。データ送信部13は、クロック送信部14Aにより送出されるクロックに同期してデータを送出する。

(もっと読む)

送受信システム

【課題】高品質の信号伝送を行うことができる送受信システムを提供する。

【解決手段】送受信システム2は、導線11〜17が並列配置されてなる配線部材10を介して送信装置20から受信装置50Aへ電気信号を伝送する。受信装置50Aにおいて、導線11はコネクタ52および抵抗器71を介して接地され、導線14はコネクタ52および抵抗器74を介して接地され、また、導線17はコネクタ52および抵抗器77を介して接地されている。

(もっと読む)

多相クロック生成装置

【課題】回路の規模を増大させることなく多相クロック信号を生成できる多相クロック生成装置を提供する。

【解決手段】、多相クロック生成装置1では、基準となるクロック信号のうち選択回路4にて2つが選択され、この2つのクロック信号のうち多相クロック生成部5a〜5cにて何れか一つを選択されると共に、選択された2つのクロック信号の中間位相を有するクロック信号が生成されて出力され、このクロック信号の何れか一つのクロック信号が位相選択部6dにて選択されることで所定の位相の出力クロック信号が生成されている。このように、簡易な構成で多相の出力クロック信号を生成することができる。そのため、多段的に並列に位相混合器を接続する従来の構成に比べて、回路の規模の増大を抑制できる。

(もっと読む)

1 - 10 / 61

[ Back to top ]