パワー・インテグレーションズ・インコーポレーテッドにより出願された特許

81 - 90 / 125

電力変換器コントローラの単一端子から複数の電圧値を検知するための方法及び装置

【課題】電力変換器コントローラの単一端子から複数の電圧値を検知するための方法及び装置を提供する。

【解決手段】本発明の態様による例示的な電力変換器用コントローラは、電力スイッチを切り換えて電力変換器の出力を調整するスイッチング制御装置を含む。コントローラは、制御装置の単一端子から信号を受信するように結合されたセンサをも含む。単一端子からの信号は、電力スイッチのオン時間の少なくとも一部にわたって電力変換器の線間入力電圧を表す。単一端子からの信号は、また、電力スイッチのオフ時間の少なくとも一部にわたって電力変換器の出力電圧を表す。スイッチング制御装置は、センサに応答する。

(もっと読む)

電力変換器の最大出力電力を制御するための方法及び装置

【課題】電力変換器用の制御器を提供すること。

【解決手段】本発明の態様による一例の回路制御器は電力変換器の入力電圧を表す入力信号を受信するように連結される入力電圧センサを含む。電流センサも含まれ、電力スイッチ内を流れる電流を感知するように連結される。オン時間の間中オン状態に、オフ時間中オフ状態に電力スイッチをドライブするようにドライブ信号発生器が連結される。この制御器は時間で乗算された入力信号の値に比例するように電力スイッチのスイッチング・サイクル周期を調整するように連結される。この時間は電力スイッチがオン状態にあるときに電力スイッチ内を流れる電流が2つの電流値の間で変化するのにかかる時間である。

(もっと読む)

ダイオード導通デューティ・サイクルを調節する方法及び装置

【課題】電力コンバータの制御方法及び装置が開示される。

【解決手段】本発明の態様に従った電力コンバータで使用するための制御回路は、制御回路に結合される電力スイッチのスイッチングを制御するクロック信号を生成するように結合されたクロック信号発生器を含む。帰還回路は、電力スイッチのオフ時間の帰還部分の間中の電力コンバータの出力を表す帰還信号を受け取るように結合されている。帰還回路は、帰還信号に応答して、全電力スイッチのスイッチング・サイクル周期の一部として電力スイッチのオフ時間の帰還部分のデューティ・サイクルを調節するために、クロック信号発生器を制御するように結合されている。

(もっと読む)

高電圧電源回路のための方法及び装置

【課題】電源で使用するための制御回路を提供すること。

【解決手段】本発明の例示的な制御回路は、制御回路に結合される電力スイッチのスイッチングを制御するための、出力信号を発生するように結合された信号発生器を含む。フィードバック回路は、電力スイッチのオフ・タイムのフィードバック部の間に、電源の出力を表すフィードバック信号を受け取るように結合される。信号発生器は、フィードバック信号が閾値より高い電力スイッチのオフ・タイムのフィードバック部のある部分と、フィードバック信号が前記閾値より低い電力スイッチのオフ・タイムのフィードバック部の別の部分とを制御するために、フィードバック回路に応答して出力信号を発生する。

(もっと読む)

低コストの電圧降下を伴う電流電圧感知回路のための方法および装置

【課題】電圧降下補償を備えた電流および電圧感知回路を提供すること。

【解決手段】電圧降下による回路の電流および電圧を感知する方法および装置である。本発明の一形態では、感知回路は、感知すべき電流の経路内に直列に結合されたダイオードおよび抵抗を備え、この直列結合の両端間の電圧が、発光ダイオード(LED)を駆動するために結合されている。

(もっと読む)

共振モードパワーコンバータのための制御構成

LLCコンバータ(11)のスイッチング周波数は制御装置(61)によって制御され、この制御装置には、フィードバック回路(52−54)が、コンバータの出力電圧に依存する第1の電流(Ifdbk)を与える。発振器回路(84−88)は、第1の電流に依存する周波数において、抵抗器(50)によって設定される第2の電流(Ifmax)と等しい限界に至るまで、鋸歯状波形(Lrmp)を生成する。2つの相補型スイッチ制御信号(A,B)が、鋸歯状波形の交代のサイクルで伝導するようコンバータの2つのスイッチ(29,31)を制御するために生成される。タイマ(63)は、第2の電流に依存して2つの相補型スイッチ制御信号間の無駄時間を生成する。別の抵抗器(51)が第1の電流の最小値を構成する電流を与え、抵抗器(55)に直列のキャパシタ(56)の充電電流が、コンバータのソフトスタートのために第1の電流を修正する。  (もっと読む)

(もっと読む)

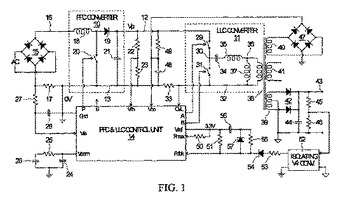

カスケード結合されたPFCおよび共振モードパワーコンバータ

カスケード結合されたPFCおよびLLCコンバータ(10,11)を制御する制御装置(14)であって、LLCコンバータの入力はPFCコンバータの出力(12,Vp)に結合され、スイッチング周波数の増大とともに低下する出力電圧を与える。この制御装置は、フィードバック信号(Fdbk)に依存して、LLCコンバータスイッチング周波数、したがってその出力電圧を制御するために、線形ランプを備えた鋸歯状波形(Lrmp)を生成する。制御装置はさらに、鋸歯状波形のそれぞれ異なるサイクル中にPFCコンバータのスイッチ(21)をオンオフするようにこれらの異なるサイクルにおいて2つのしきい値(Pmul,Vtp)と線形ランプとを比較することによって、PFCコンバータのために、LLCコンバータスイッチング周波数に等しい周波数またはその整数分の1である周波数を備えたPWM信号(P)を生成する。論理回路(211〜216)は、PFCコンバータスイッチ遷移がLLCコンバータのスイッチ遷移と同時に生じるのを妨げる。  (もっと読む)

(もっと読む)

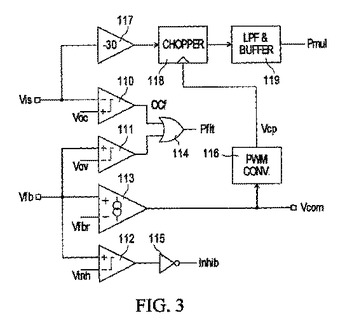

PFC−PWMパワーコンバータのための制御構成

PFC(力率補正)コンバータ制御装置(60)において、PWM(調整されたパルス幅)信号(Vcp)は、相互コンダクタンス増幅器(113)によって生成されるPFCコンバータ出力電圧誤差信号(Vcom)を、PFCコンバータとカスケードカスケード結合される共振モードコンバータの制御装置(61)からであり得るランプ信号(Lrmp)と比較することにより生成される。比較された信号の振幅範囲を一致させるためにレベルシフト(140〜141、160、165、166)が用いられる。PFCコンバータの入力電流を表わし、電流ミラー(121〜123)によって生成される電流は、PFCコンバータのための制御信号を構成する平滑化された電圧(Pmul)を生成するために、PWM信号によって並列の抵抗(126)およびキャパシタンス(127)にスイッチング(125)される。  (もっと読む)

(もっと読む)

相補的な差動入力段を有する比較器

比較器は、ともに略レールトウレール(rail to rail)に広がる、重なり合う共通モード入力電圧範囲を有する相補的な(たとえば、NMOSおよびPMOS)比較器セル(40,41)を備える。エッジ検出器(42,43)、ゲート(44,45)、ラッチ(48)を有するデジタルロジック配列は、比較器セルの出力での遷移に応答し、最も早い立上りエッジに応答してラッチをセットし、最も早い立下りエッジに応答してラッチをリセットする。ラッチの出力は、比較器の出力を構成する。その結果、比較器は、幅広い共通モード入力電圧範囲のために最適化された速度でエッジに敏感となる。追加のロジックゲート(46,47)は、ラッチのレベルに敏感な制御を提供することができる。  (もっと読む)

(もっと読む)

スナバを有する電力コンバータ

第1のインダクタ(10)と、制御されたスイッチ(12)と、メインダイオード(14)と、出力キャパシタ(16)とを備える降圧または昇圧コンバータは、損失を減少させるためのスナバ回路を含む。スナバ回路は、コンバータのスイッチおよびメインダイオードと直列の経路に設けられた第2のインダクタ(20)と、第2のインダクタと並列に直接的に接続され、直列接続された抵抗(22)およびダイオード(24)と、メインダイオードと並列に設けられ、メインダイオードの寄生容量によってその一部または全部が構成されるキャパシタンス(28)とを含む。  (もっと読む)

(もっと読む)

81 - 90 / 125

[ Back to top ]