プラスティック ロジック リミテッドにより出願された特許

1 - 10 / 18

層選択レーザーアブレーションパターニング

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

フレキシブルタッチスクリーンディスプレイ

【課題】抵抗膜式タッチスクリーン技術を用いて、フレキシブルタッチスクリーンコンポーネントをフレキシブルディスプレイと一体化し、フレキシブルな組み合わせデバイスを製作する。

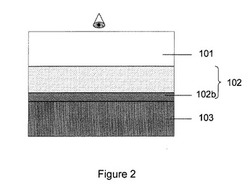

【解決手段】タッチセンシティブアクティブマトリックスディスプレイデバイスであって、第1のフレキシブル基板102b上に作製され、画面を有するディスプレイ101と、前記ディスプレイ101の下にあり、第2のフレキシブル基板を備えたタッチセンシティブセンサ103とを備える。

(もっと読む)

エッジシールを有する電気光学表示素子

【課題】エッジシールを有する電気光学表示素子の提供。

【解決手段】電気光学表示素子(100)は、バックプレーン(102)と、バックプレーン(102)に隣接する電気光学層(112)であって、電気光学層(112)の縁を越えて延在するバックプレーンの外周部を残すように、バックプレーン(102)よりも小さい電気光学層(112)と、バックプレーン(102)からは電気光学層(112)の反対側に配置された保護層(118)とを備え、保護層(118)の外周部は、電気光学層の縁を越えて延在し、(120において)バックプレーン(102)に接着される。

(もっと読む)

トランジスタ制御表示装置

【課題】高い開口率となる薄膜トランジスタ装置を提供する。

【解決手段】溶液堆積(deposited)によって形成される下側導電性層と、前記下側導電性層の上に設けられかつそれと導電性相互接続を介して1つ以上の絶縁層を通じて電気的に接続されている上側導電性層とを備える電子装置を製造する方法であって、前記相互接続の作成は、下側導電性層と前記1つ以上の絶縁層とを区別する光溶発技術を使って少なくとも下側導電性層の一部へと下向きに延びる孔を前記少なくとも1つの絶縁層に定義する工程、およびその後前記孔に導電性材料を堆積する工程を含むことを特徴とする方法。

(もっと読む)

自己整合印刷

【課題】表面エネルギーパターンの手助けなしに印刷材料の第1および第2の領域を分離するマイクロメータおよびサブマイクロメータの寸法の臨界形状を形成することのできる方法を提供する。

【解決手段】 溶液処理および直接印刷によって導電性、半導体および/または絶縁性の層を蒸着する工程、および第2の材料の溶液をはじく第1のパターンの周りに表面エネルギー障壁を自己整合的に形成することによって電気活性ポリマーの高解像度パターンを形成する工程を含む、有機性または部分的に有機性のスイッチング装置を形成する方法。

(もっと読む)

オフセット上部画素電極構成

本発明は、上部画素電極が共通(COM)電極および隣接素子のゲート電極に重なるようなオフセット構成で配置された半導体構造体に関する。このような構成により素子性能の向上が可能となり、その結果、蓄積容量が大きくなる等の特徴が得られる。  (もっと読む)

(もっと読む)

デバイスのパターニング

【課題】有機スイッチングデバイスまたは部分有機スイッチングデバイスを形成する方法である。

【解決手段】前記方法は、少なくとも1つのパターニング層を含む電気デバイスを基板上に形成する方法であって、前記基板上の第1の材料層を光ビームに露光して、前記第1の層の物理的特性を改変するように、前記第1の層のパターニングを行う工程を含み、前記光ビームの一部は、前記基板上の事前堆積されたパターンによってブロックまたは減衰され、これにより、前記光がブロックまたは減衰されない領域においてのみ前記基板上の第1の層を改変する、方法である。

(もっと読む)

歪み耐性ピクセル構造

本発明は、フレキシブル基板における歪みを補償するピクセル構造、前記ピクセル構造を含む表示装置を製造する方法に関する。本発明は、フレキシブル表示装置のフレキシブル基板における歪みを補償するピクセル構造を提供し、薄膜トランジスタ(TFT)を含むフレキシブル基板上の第1層、前記第1層上に設けられ前記TFTに接続されて前記TFTからの信号を受信するピクセル電極を含む第2層、前記ピクセルによって表示された光をフィルタするカラーフィルタを有する第3層を有し、前記第3層は、前記カラーフィルタが前記ピクセル電極に対して実質的に位置調整されるように前記第2層に対して位置調整され、前記位置調整は前記フレキシブル基板における歪みによって生じた前記第1層における歪みを補償するものである。  (もっと読む)

(もっと読む)

歪み許容プロセシング

本発明は、フレキシブル基板又は歪みを受けやすい基板を組み入れる集積回路の歪み許容プロセシング方法に関する。具体的に本発明は、フレキシブルディスプレイを駆動する集積回路(IC)を製造する方法が与える。これは、基板平面内の2つの直交方向(x,y)の双方において実質的には規則的に反復することがない、空間的に非反復なフィーチャのパターンをフレキシブル基板上の第1層に堆積することと、空間的に反復なフィーチャのパターンを前記第1層上の第2層に堆積することと、前記非反復なフィーチャと前記反復なフィーチャとの電気的接続を可能とするべく前記第2層と前記第1層とのアラインメントをとることとを含み、前記アラインメントを可能とするべく前記反復なフィーチャの堆積中に歪み補償が適用される。  (もっと読む)

(もっと読む)

自己整合電極を有するデバイスの作製方法

本発明は、薄膜トランジスタ、特に、パターニング技術が、下地電極に対して正確に整列される必要がある電極パターンの画定に使用される薄膜トランジスタなどの電子デバイスの作製に関する。作製方法は、狭い線幅を有する構造を形成することができない、及び/又は、先に堆積されたパターンに対してあまり正確に位置決めすることができない、レーザアブレーションパターニング技術または溶液ベースの直接書き込み印刷技法などの種々のパターニング技術に適用可能である。こうして、本発明者等は、減算的技法によるゲートパターニング、特に、選択的レーザアブレーションパターニングと、印刷などの加算的技法によるゲートパターニングの両方について適用可能である自己整合ゲート技法を述べる。技法は、低解像度ゲートパターニングの使用を容易にする。  (もっと読む)

(もっと読む)

1 - 10 / 18

[ Back to top ]