次世代半導体材料技術研究組合により出願された特許

1 - 10 / 82

絶縁膜評価方法およびテスト素子

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体装置、及びその製造方法

【課題】多孔質低誘電率絶縁膜が用いられていても、絶縁破壊耐性に優れた配線構造の半導体装置を提供する。

【解決手段】CMP処理工程を経て配線膜が構成される半導体装置の製造方法であって、CMP処理によって汚染された多孔質低誘電率絶縁膜に対して、酸処理、アニール処理、あるいは汚染個所の清浄化処理工程を施し、前記多孔質低誘電率絶縁膜表面の有機成分量、水分量、銅、ナトリウム、カリウム等の残存量を規定値以下に低減する。

(もっと読む)

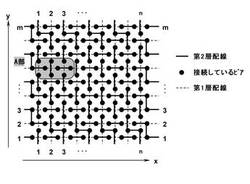

TEG構造、及び層間剥離箇所探索方法

【課題】配線層とビア層との剥離箇所を簡単に特定できる技術を提供する。

【解決手段】第1層配線層のパターンの導体部は、所定の方向Xに沿って、複数本、点線状に設けられた導体部と、前記方向Xに交差する所定の方向Yに沿って、複数本、点線状に設けられた導体部とを具備し、第2層配線層のパターンの導体部は、所定の方向Xに沿って、複数本、点線状に設けられた導体部と、前記方向Xに交差する所定の方向Yに沿って、複数本、点線状に設けられた導体部とを具備し、前記方向X(方向Y)に沿って設けられた第1層配線層と第2層配線層とは、平面視において、互いに、食い違うように、かつ、全体で、一つの連続した線が描かれるように設けられてなり、第1層配線層と第2層配線層とは、両方向ともに平面視において共通する或る位置において、電気的に接続し一つのラインに沿った一つの導通ラインが構成されている。

(もっと読む)

表面特性観察方法、表面特性観察方法に供される試料の製造方法、及び表面特性観察方法に供される試料

【課題】nmオーダーの表面傷の観察が可能な技術を提供することである。

【解決手段】基体の表面特性を観察する方法であって、基体の表面に、該基体表面を構成する材料の仕事関数と異なる仕事関数を有する材料で構成される膜を設ける成膜工程と、前記成膜工程において設けられた前記基体表面に存する凹部を埋めた該膜の構成材料が残存するように該基体表面に設けられた膜を除去する膜除去工程と、前記膜除去工程後の基体の表面を電子顕微鏡で観察する観察工程とを具備する。

(もっと読む)

半導体集積回路用テスト回路

【課題】トランジスタの特性と配線系における配線負荷の特性とを高精度で分離でき、配線負荷に大きな影響を及ぼす層間絶縁膜等の特性を評価できる技術を提供することである。

【解決手段】(2k+1:kは1以上の整数)個のインバータを具備したリング発振回路を有してなり、隣接するインバータの間に、各々、同一インピーダンス値の負荷回路が設けられてなる半導体集積回路用テスト回路。

(もっと読む)

デバイス、及びデバイスの層間剥離判定方法

【課題】電気的不良な現象を伴わない層間剥離をも高精度で効率良く見付けることが可能な技術を提供することである。

【解決手段】基板上に積層された複数の層を具備するデバイスにおける層間剥離判定方法であって、基板側から赤外線を照射する赤外線照射工程と、前記赤外線照射工程による赤外線照射で得られる画像におけるモアレの有無をチェックするモアレ有無チェック工程とを具備する

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

応力測定方法、応力測定用センサ、及び残留応力評価用デバイス

【課題】ビアチェーンを設けた基板に応力を加えた際に可逆的な抵抗変化が見出されたことを利用して、基板やこの基板を固定した測定対象物に加わる応力をビアチェーンの抵抗変化に基づいて測定する応力測定方法を提供する。

【解決手段】所定の基板10上にビアチェーン15とこれに接続するパッド17、18を備えたものを測定対象物に固定し、パッド間の電気抵抗を測定することにより、測定対象物に加わる応力が同時に基板10にも加わる中、この応力の大きさに対応したビアチェーン15の抵抗変化を外部から検知できることとなり、あらかじめ応力の変化とビアチェーン15の抵抗変化との関係を把握しておくことでビアチェーン15の抵抗値から応力の値を取得でき、同じ応力に対しピエゾ抵抗効果の場合に比べ大きく抵抗が変化する性質に基づいて、感度よく測定対象物に加わる応力の測定が行える。

(もっと読む)

パターン形成方法

【課題】誘電率の大幅な増大や絶縁性の大幅な劣化が引き起こされること無く、レジストのLERが抑制され、正確な微細加工が可能になる技術を提供することである。

【解決手段】露光・現像後にポストベークしてレジストを所定パターンに加工するパターン形成方法において、

前記ポストベークは、第1のポストベークと、この第1のポストベークの後に行われる第2のポストベークとを具備し、

前記第2のポストベークの温度は前記第1のポストベークの温度よりも高い。

(もっと読む)

研磨方法

【課題】CMP工程における膜剥がれを抑制すると共に、研磨圧力の低下に伴う減少した研磨速度を高めることが出来る技術を提供することである。

【解決手段】基板に対してCMPを施して加工するCMP方法であって、前記CMPに際して、前記基板の中央部において加える圧力を0.05〜1.5psiとなし、前記基板の外周に配置したリテーナリングに加える圧力を、前記基板の中央部において加えた圧力の3〜15倍とする。

(もっと読む)

1 - 10 / 82

[ Back to top ]