アーテー・ウント・エス・オーストリア・テヒノロギー・ウント・ジュステームテッヒニク・アクチェンゲゼルシャフトにより出願された特許

11 - 19 / 19

非粘着性材料、平面材料層の一部を除去する方法、多層構造体、およびそれらの使用

本発明は、実質的平面材料層(2)の一部(11)を除去する間に使用される非粘着性材料に関し、実質的平面材料層(2)は、接続段階において、少なくとも1つのさらなる実質的平面材料層(9)に接続される。本発明によれば、非粘着性材料(8)は、隣接する実質的平面材料層(2、9)とは異なる極性を有する。本発明はまた、実質的平面材料層(2)の一部(11)を除去する方法、相互に接続される少なくとも2つの実質的平面材料層(2、9)から構成される多層構造体、および特に多層プリント回路基板におけるその使用に関し、実質的平面材料層(2)は、接続段階において、少なくとも1つのさらなる実質的平面材料層(9)に接続される。  (もっと読む)

(もっと読む)

フレキ−リジッドプリント回路基板を製造する方法、およびフレキ−リジッドプリント回路基板

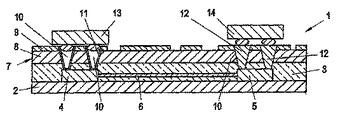

本発明は、フレキ−リジッドプリント回路基板を製造する方法に関し、プリント回路基板の少なくとも1つのリジッド領域(1、17、18)が、プリント回路基板の少なくとも1つのフレキシブル領域(7)に非導電性材料の層または誘電体層(13、15)を介して接続されて、少なくとも1つのリジッド領域は、プリント回路基板のフレキシブル領域(7)に接続されており、プリント回路基板のリジッド領域(1)は、次いで切り開かれ、プリント回路基板の個々のリジッド部分領域(17、18)間の接続は、それらに接続されたフレキシブル領域(7)を介して確立される。本発明によれば、プリント回路基板の少なくとも1つのリジッド領域(1、17、18)とプリント回路基板の少なくとも1つのフレキシブル領域(7)との間の接続は、リジッド領域を切り開く前に接着することによって確立される。本発明はまた、位置合わせ精度の向上を可能にし、製造することが簡単で、プリント回路基板の少なくとも1つのリジッド領域(1、17、18)とフレキシブル領域(7)との間の接続(15)の層厚が低減された上記タイプのフレキ−リジッドプリント回路基板に関する。  (もっと読む)

(もっと読む)

プリント回路基板上に電子部品を固定する方法ならびにプリント回路基板および少なくとも1つの電子部品を有するシステム

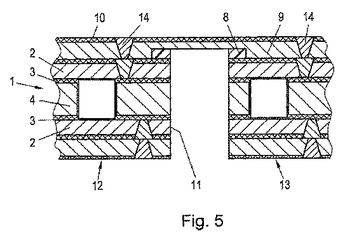

プリント回路基板2に電子部品3を固定し、電子部品3をプリント回路基板2へ接触・接続する方法では、複数の接触および接続パッド8を有するプリント回路基板2を提供するステップと、プリント回路基板2の複数の接触および接続パッド8に対応する複数の接触および接続位置5を有する電子部品3を、プリント回路基板2の接触および接続パッド8の間隔に比べて減少した相互間隔で提供するステップと、プリント回路基板2の接触および接続パッド8と電子部品3の接触および接続位置5の位置の間に、電子部品3の接触および接続位置5をルーティングするための少なくとも1つの中間層4を配置または形成するステップとを提供する。ルーティングのための中間層4の製造方法ならびにプリント回路基板2とルーティングのために中間層4を使用する電子部品3を有するシステムも提供される。  (もっと読む)

(もっと読む)

光電子素子及び光導波路を有するプリント回路基板素子

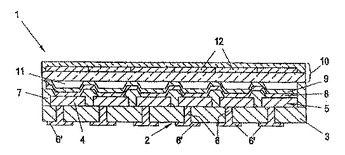

本発明に係るプリント回路基板素子(10)は、光学的に光重合可能な材料層(13)内に埋設された少なくとも1つの光電子素子(1)と、光電子素子(1)と光学的に結合され、光子の照射により光重合可能材料層(13)内に形成された少なくとも1つの光導波路(14)を含み、光電子素子(1)は、その光出力面(3)上に湾曲状の偏向ミラー(5)を備え、出力光(15)を例えば90°の角度偏向する。  (もっと読む)

(もっと読む)

導電性の試験領域を有する多層プリント回路基板及び中間層のミスアライメントを測定する方法

中間層の推定されるミスアライメント又は中間層構造のミスアライメントのそれぞれを測定する少なくとも1つの中間層(2)の上に導電性の試験領域(7)を備える多層プリント回路基板(1)であって、上記導電性の試験領域は、列を成して並べられ、あらゆる大きさの非導電性の領域(8.i)を内側に規定するリング構造(7.i)で構成され、試験領域の辺りに導通用貫通穴(5)を有し、ミスアライメントが無い又は無視して良い場合、当該貫通穴(5)は、非導電性の領域の内側で構成され、さらに、ごくわずかなミスアライメントもない場合には、少なくとも1つの貫通穴(5)は、1つの導電性のリング構造(7.i)の辺りに存在し、リング構造(7.i)と導電的に接続している。リング構造の試験領域(7.i)は、円周方向に分割されたセグメント(a、b、c、d)で構成され、上記セグメント(a、b、c、d)は、非伝導性の分離領域(9)で円周方向にお互いに分離されている。  (もっと読む)

(もっと読む)

回路基板エレメントの製造方法および回路基板エレメント

導体層(13)を備えた回路基板エレメント(11)およびその製造法(ここで、回路基板支持体(12)に構築された導体層(13)に貴金属(16)を付与する)を開示する。導体層(13)は、好ましくはその構築後、その表面が粗面化され、この構築および粗面化した導体層(13)の本質的に全体に貴金属を層(16)として付与する。その際、貴金属層の表面には対応の凹凸(8’)が与えられる。  (もっと読む)

(もっと読む)

少なくとも一つの光導波路を含むプリント回路基板エレメント、およびそのようなプリント回路基板エレメントの製造方法

光導波路および埋め込まれた光電子エレメントを備えるプリント回路基板エレメントを開示する。

(もっと読む)

(もっと読む)

薄膜アセンブリおよび薄膜アセンブリの製造方法

基材(2)および、薄膜技術によって基材上に設けられた少なくとも1つの電子薄膜構成要素(8)、を有する、薄膜アセンブリ(1)であって、ここでベース電極(4)が基材上に提供されており、その上に、薄膜構成要素の一部を形成する、ベース電極薄膜層(21)が、上部トップ電極(9)と併せて配置されており;

この基材(2)は、絶縁材ベース体(3)と、導体層(5)としての金属コーティングと、を有する、従来知られているプリント回路基板(2)から構成され、

この導体層(5)は、ベース電極(4)を形成し、そしてこの目的のために、少なくとも薄膜構成要素(8)の位置上はスムージングされており、および

接触層(18)が、スムージングされ、必要に応じて補強された導体層(5)と、薄膜構成要素(8)の積層薄膜層(21)と、の間に、薄膜技術によって提供されており、ここで接触層が、ベース電極(4)の表面に、物理的または化学的に吸着されている、薄膜アセンブリ。

(もっと読む)

(もっと読む)

印刷回路板(PCB)を製造するためのブランクの被覆方法

本発明は耐酸抵抗性であり、かつ少なくとも2層から成り互いに下と化学的に接続しおよび/またはPCBブランクの金属表面に接続している保護層を含有するPCBブランクに関する。本発明はまた、耐酸抵抗性でありかつ少なくとも2層から成る保護フィルムでPCBブランクを塗布する方法を提供する。 (もっと読む)

11 - 19 / 19

[ Back to top ]