サンディスク コーポレイションにより出願された特許

91 - 100 / 175

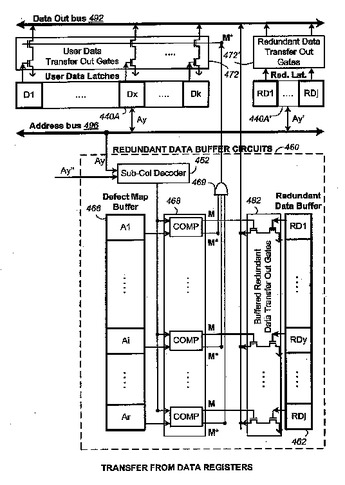

冗長データがリモートバッファ回路にバッファされる不揮発性メモリおよび方法

メモリは、そのユーザ部分に、冗長部分に存在する冗長位置により置換可能な欠陥位置を有する。ユーザ部分および冗長部分の列回路に存在するデータラッチは、メモリから感知されるかあるいはメモリに書き込まれるべきデータがデータバスとの間で交換されることを可能にする。リモート冗長方式は、任意の数の列回路がアクセスし得る中央バッファから入手できる冗長データを有する。冗長データバッファ回路は、データが中央バッファから取られるときに、欠陥位置を除いてユーザデータラッチからのデータとのバス交換を可能にする。このようにしてユーザ部分のためのアドレス指定だけがバス交換のために使用される。また、冗長データへのアクセス可能性は、冗長データラッチに関しての列回路の位置によって制限されず、バッファされた冗長データは、列回路により課される粒状度より精細な粒状度でアクセスされ得る。  (もっと読む)

(もっと読む)

プログラミング速度を向上させるプログラミング電圧に応じたプログラム時間調整

不揮発性メモリシステムでプログラムパルスに配分されるプログラム時間を所要のポンプパルスの電圧レベルとの関係で調整することにより、電荷蓄積素子を所要のしきい値電圧までプログラムするにあたって必要となる総ポンプパルス数は減少する。例えば、所要のポンプパルスの電圧レベルの増加にともないプログラム時間を増やすことができる。プログラムパルスのプログラム時間の値を増加させることにより、高振幅プログラムパルスで所望のプログラミング電圧に達するまでのチャージアップ時間の増加を補償することができる。  (もっと読む)

(もっと読む)

不揮発性メモリの代替の感知技術

本発明により、メモリセルの感知方式が提供される。選択メモリセルは、チャネルを通って接地に放電され、次いで、従来のソースにかかる電圧レベルと、コントロールゲートにかかる別の電圧レベルとを有し、セルビット線を充電する。次いで、メモリセルのビット線は、ビット線電圧が、任意のさらなるセル伝導を遮断できるほど高くなるまで充電される。ビット線電圧は、セルのデータ状態に依存して、あるレートであるレベルまで上昇し、次いで、基板効果の影響を受けたメモリセルしきい値が、電流が本質的に遮断される点に達すのに十分高いレベルにビット線が達すると、セルは遮断される。特定の実施形態は、複数のこのような感知サブ動作を実行し、各動作で異なるコントロールゲート電圧を用い、複数の状態は、すでに放電されたセルをそれらのソースを通して充電することによって、各動作において感知される。  (もっと読む)

(もっと読む)

短距離無線通信機能を有するネスト状メモリシステム

大容量記憶メモリカードは、それがともに使用されるホスト装置に対して機能を追加する。大量のユーザファイルを記憶しかつそれらを不正な複製から保護する能力に加えて、本発明による大容量記憶装置は、短距離無線通信を、別の状況ではそのような機能を有しない携帯形電子装置との間で行えるようにする。好ましい一実施形態において、大容量記憶装置は、マザー/ドーター構成を有し、ドーターカードは、独立して使用可能な完全に機能するマイクロSDカードである。マザーカードは、SDカードスロットに受け入れることが可能であり、SDプロトコルを介して通信する。ドーターカードがマザーカード内にあるかどうかに関わらず、ホストは、その内部の大容量記憶装置とともに、短距離無線通信を行うことが可能になる。このような通信は、ピア・ツー・ピアであってもよく、電子財布の類として商品またはサービスを購入するために使用することができる。装置のコントローラも、装置およびホストを電子財布として使用する場合に行われた金融取引を調整、制御、および保護するように動作可能である。  (もっと読む)

(もっと読む)

不揮発性メモリにおける改善されたプログラムベリファイ操作のための方法および装置

交互に、プログラミングパルスを加え、プログラミングをベリファイすることを含む不揮発性メモリのプログラミングにおいて、メモリセルの状態に依存してベリファイ操作の一部が不必要であると認識されて省かれるとき、プログラムベリファイ部分で時間が節約される。好ましくは、2つのメモリ状態を区別するための境界しきい値レベルに関してのプログラムベリファイ操作に関して、このベリファイ操作は一連の2つのベリファイサブサイクルを含み、第1のサブサイクルは、その境界しきい値レベルから所定のマージン下の第1のしきい値レベルに関してのベリファイを実行し、第2のサブサイクルは、その境界しきい値レベルと同一である第2のしきい値レベルに関してのベリファイを実行する。従来の場合とは違って、そのグループのいずれか1つのメモリセルが第1のしきい値を通過したとベリファイされるまでは第2のサブサイクルは実行されない。  (もっと読む)

(もっと読む)

不揮発性メモリにおける補償感知のための基準センス増幅器および方法

不揮発性メモリの伝導電流を感知するための1つ以上のセンス増幅器は、同様の特性および動作条件を有する基準センス増幅器によって時間を定められる信号によって制御される。一態様において、感知期間は、基準電流を感知する基準センス増幅器が期待された状態を検出したときにより決定される。他の一態様において、増幅された出力のための積分期間は、基準センス増幅器が期待された状態を出力したときにより決定される。1つ以上のセンス増幅器を制御するためにこれらの決定されたタイミングが使用されるとき、環境全体の変動が追跡される。  (もっと読む)

(もっと読む)

論理アドレス形ファイル記憶

ホストによって論理アドレス範囲にマッピングされるファイルは、メモリシステムへ送信される前に論理的に断片化される。その後、論理的に断片化した部分はメモリシステムのブロックに格納されるときに再度組み立てられる。ホストはデータの送信に先立ち、データのファイル−論理マッピングに関する情報をメモリシステムに提供する。メモリは、データが属するファイルに基づきデータの格納位置を選択する。  (もっと読む)

(もっと読む)

レガシーホストのための方法およびメモリシステム

不揮発性メモリデバイスはコントローラを備え、メモリ動作を制御しかつレガシーメモリデバイスのメモリおよび通信特性を模倣する方法を含む。かくして、メモリデバイスは、レガシーメモリデバイスとともに動作するように本来設計されたホストに適合する。とりわけコントローラは、マルチビットメモリ、誤り訂正要求、メモリの上書き支援状況、消去可能なブロックサイズ等の差異を考慮に入れながらホストに対し模倣を遂行する。  (もっと読む)

(もっと読む)

再対象化可能なメモリセル冗長性を備えたメモリ

冗長列を有するメモリアレイにおいて、ある技法により、欠陥セルを冗長列内の冗長セルに個別に再マッピングすることが可能となる。1つの冗長列内の冗長セルを、複数の非冗長列の欠陥セルに置換する。再マッピングは初期試験および設定の一部として行われる。この技法のために専用ハードウェアを用いることもできるし、メモリコントローラ内のファームウェアによってこの技法を実施することもできる。  (もっと読む)

(もっと読む)

低ギャップフィルアスペクト比のフラッシュデバイスのための集積化フロー

フローティングゲート間に浅溝素子分離構造(STI)を有し、浅溝素子分離誘電体がエッチングされるフローティングゲート間に延びるコントロールゲートを有する不揮発性メモリが形成される。エッチング深度の制御は、イオン注入を使用して、基礎をなす誘電体と比較して高いエッチングレートで誘電体の層を作ることによって達成される。導電層は、注入中に基板と重なる。メモリアレイ内に少量のポリシリコンという特徴を有し、周辺領域の大量のポリシリコンという特徴を有する基板は、周辺領域における突起部と、突起部が除去されると停止するソフト化学的機械的研磨ステップとを使用して正確に平坦化される。  (もっと読む)

(もっと読む)

91 - 100 / 175

[ Back to top ]