エヌエックスピー ビー ヴィにより出願された特許

21 - 30 / 657

リーダ及び/又はトランスポンダによりサポートされるアプリケーションを隠蔽するリーダ及びトランスポンダとその方法

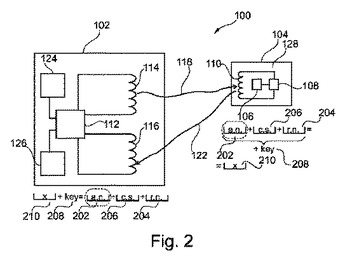

複数の異なるアプリケーションを格納した記憶装置(106)を備えるトランスポンダ(104)であり、該トランスポンダは、リーダ(102)のリクエストに応答して、該トランスポンダ(104)と前記リーダ(102)の双方が知っている暗号化スキームを用いて解釈可能なレスポンスを生成する処理装置(108)と、前記レスポンスを前記リーダ(102)に送信するように構成された送信装置(110)とを備え、前記リーダ(102)が、前記暗号化スキームを用いて前記レスポンスを解析することによりアプリケーションが当該トランスポンダ(104)によりサポートされているかどうかを決定することができるように構成されている、トランスポンダ。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法および半導体デバイス

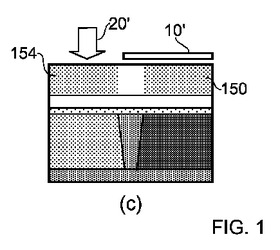

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

バーチカル型相変化メモリセル

バーチカル(垂直)型相変化メモリセル(2)は相変化メモリ材料の活性領域(24)を有し、この活性領域(24)は、相変化メモリ材料の一部上にのみ延在する接点を設ける、または相変化メモリ材料の一部のみを露出させる絶縁層を設けることのいずれかで画定する。1個のセルには1個以上の活性領域(24)が存在し、各セルに1ビット以上のデータを格納することができる。  (もっと読む)

(もっと読む)

多重ビット相変化メモリセル

【解決手段】相変化メモリセルは、1個またはそれ以上のメモリ領域(14,18)を有し、これらメモリ領域は第1および第2の電極(4,6)間に延在する相変化メモリ材料(2)の狭窄部分とする。複数個のメモリ領域(14,18)はそれぞれ、電流および/または電圧の適切なプログラミング条件を加えることで、低抵抗状態または高抵抗状態にプログラムすることができる。高抵抗状態の抵抗および高抵抗状態を低抵抗状態に変換するプログラミング条件は、前記複数個のメモリ領域毎に異ならせる。  (もっと読む)

(もっと読む)

相変化材料層を有する多層構造およびその製造方法

本発明は多層構造の製造方法を提供し、該方法は、サブストレート上に相変化材料層を形成する工程と、保護層を形成する工程と、該保護層上に他の層を形成する工程と、該他の層をパターン形成する第1パターン形成工程と、前記保護層および前記相変化材料層をパターン形成する第2パターン形成工程と、を有する。特に、第1パターン形成工程は、化学エッチング液を用いるエッチング工程とすることができる。さらに、相変化材料層を形成する前に、複数の電極を基板上に形成することができ、例えば、複数の電極を同一レベルになるよう形成し、例えば、複数の電極が平面構造を形成し、垂直構造にならないようにする。  (もっと読む)

(もっと読む)

出力回路網を最小にした3ウェイドハティ増幅器

3ウェイドハティ増幅器は増幅器入力端と増幅器出力端とを有する。この増幅器は、主ステージと、第1のピークステージと、第2のピークステージとを有する。この増幅器は、前記増幅器入力端を前記ステージの入力端に接続する入力回路網と、前記ステージを前記増幅器出力端に接続する出力回路網とを有する。この出力回路網は、主ステージの出力端と増幅器出力端との間で90°の移相を実行し、第1のピークステージの出力端と増幅器出力端との間で180°の移相を実行し、第2のピークステージの出力端と増幅器出力端との間で90°の移相を実行する。  (もっと読む)

(もっと読む)

デューティサイクル変調伝送

デューティサイクル変調ビットシグナリング方法及び回路であり、該方法及び回路は、デューティサイクル比でビットシグナリングを行うステップを含み、該ステップにおいて前記デューティサイクル比がシグナリングの伝送レートに依存して変化される。ビット周期は短位相部と長位相部を含み、長位相部の持続時間と短位相部の持続時間との比が伝送速度の減少に対して増大するように、長位相部と短位相部との間のデューティサイクルが変化される。デューティサイクル比は伝送レートの一つ以上のレンジに従ってシグナリングの伝送レートに依存して変化される。高伝送レートレンジではデューティサイクルは固定比として規定され、低伝送レンジではデューティサイクルはビット周期の短位相部の固定長により規定される。  (もっと読む)

(もっと読む)

PCBに基づく自動トレーサビリティのためのシステム、装置及び方法

PCB素子をアンテナとして用いてUHF帯域でRFID通信を達成するシステム、装置及び方法を提供する。本発明は、PCBの各製造段階で、PCBを含む製品が何処にあるか及びその現在の検査状態がどうであるかが正確に分かるように、アセンブリレベルでのPCBの追跡を可能にすることにより、PCB及びPCBを含む製品のサプライチェーンマネジメントを可能にするものである。一実施例では、PCBの現存のグランドプレーンを用い、PCBの全ての層のグランドプレーンを分割し、ダイポール構造が受信したエネルギーレベルにより回路をオン状態に附勢し、これにより、RFID/電子製品コードトランザクションを可能にする。他の実施例では、現存の又は追加した配線を、スプリット(分割した)グランドプレーンの代わりに、RFID‐ICに対するアンテナとして用いる。サプライチェーンマネジメントでは、ITネットワークに接続された専用のRFIDインタロゲータを採用し、このインタロゲータによりPCBのアセンブリ処理の間中、部品表を自動的に満足させるようにしうる。最終製品の製造者も、在庫、出荷及び返品を含む自身の最終製品項目基準のサプライマネジメントシステムにおいてRFID‐ICを用いうる。  (もっと読む)

(もっと読む)

多原色ディスプレイのための最適な空間分散

表示される画像について優れた解像度/シャープネスを持つため(例えばナイキスト限界問題を持つパターンを表示する場合における低干渉バンディング)、多原色ディスプレイ100は、3色より多い加色法原色R、C、G、Bを持ち、それぞれの原色についての対応する駆動信号rが最大である場合に3色より多い加色法原色R、C、G、Bの最も高い出力輝度を持つ前記原色の半数C、Gが、略等距離のサブ画素位置Ddにおける前記ディスプレイのサブ画素104、108により生成可能である。  (もっと読む)

(もっと読む)

トラステッドアプリケーションに対するアクセス権を管理する方法、システム、トラステッドサービスマネジャー、サービスプロバイダ及びメモリ素子

セキュアエレメント(SE)内に記憶されたサービスプロバイダ(SP1、SP2)のアプリケーション(appSP1.1、appSP1.2、appSP2.1)に対するこのサービスプロバイダ(SP1、SP2)のアクセスのトラステッドアプリケーション(SP1_WL)を許可する方法が、前記サービスプロバイダ(SP1、SP2)により、そのアプリケーションに対するアクセスを許可するための要求(REQ1)をトラステッドサービスマネジャー(TSM)に送信するステップと、このトラステッドサービスマネジャー(TSM)により、アクセス権コード(AC1)を発生させるとともに、このアクセス権コードを前記サービスプロバイダ(SP1、SP2)に且つ前記セキュアエレメント(SE)内のサービスマネジャー(SM)に送信するステップと、前記サービスプロバイダ(SP1、SP2)により、前記トラステッドアプリケーション(SP1_WL)を発生させ、このトラステッドアプリケーションにアクセス権コード(AC1)を与え、このトラステッドアプリケーションを前記セキュアエレメント(SE)に送信するステップとを具えており、前記トラステッドアプリケーション(SP1_WL)が、前記アクセス権コード(AC1)を有する前記サービスマネジャー(SM)に接続され、その時点でこのサービスマネジャー(SM)が前記アプリケーション(appSP1.1、appSP1.2、appSP2.1)に対するワレット(SP1_WL)のアクセスを許可するようにする方法を提供する。  (もっと読む)

(もっと読む)

21 - 30 / 657

[ Back to top ]