エイ・アイ・エル株式会社により出願された特許

1 - 7 / 7

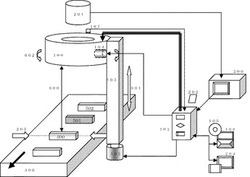

検査装置用照明システム

【課題】検査装置における照明装置の煩雑・且つ経験や勘に頼る非効率、不確実な調整作業を軽減し、論理的に最適化し、検査における生産性を向上させ、結果として不良率を下げ、稼働率を上げる。

【解決手段】センシングの為のカメラやセンサ200,201を備えた、検査装置に於いて、単色〜主に多色、異波長の光源を備えた照明100と100を複数軸方向に可動する機能102、103、104、場合により専用受光センサ107を備えた照明部分とそのコントローラ101とPC用ソフトウエア105を考案し、照明100の発光色、発光波長、発光光量、照射距離/範囲、照射角度、などを能動的に変化させ、記憶し、呼び出し、比較し、判断する機能を有する。

(もっと読む)

表示装置

【課題】アクリル板等による導光手段の端面よりLED等の光源により光乱反射素材を光らせる表示装置において、光源の点灯時には前記光乱反射素材を明るく輝かせ、光源の消灯時にはその存在が判別できない程度に見えなくする表示装置を提供する。

【解決手段】平板の導光手段1と光源2を有する装置において、導光手段表面12にフィルム貼り付けまたは印刷等により光乱反射素材3を設置して文字または図形を成し、前記文字または図形の1個以上を線幅2ミリメートル程度以下の細い形状とし、なおかつ前記光乱反射素材を白色素材とし前記光源を白色光源とすることにより、光源の点灯時には前記文字または図形が白く輝き、光源の消灯時には線幅2ミリメートル以下の文字または図形が灰色の細線となって背景に溶け込みその存在がほぼ判別できなくなる。

(もっと読む)

表示装置

【課題】バックライト型チャンネル文字の視覚表現効果である文字周りの光の縁取りをより薄型軽量のパネル型サインで実現し、設置自由度の改善と製造期間およびコストの削減を図る。

【解決手段】平板の導光手段と光源を有する装置において、導光手段の第一表面にフィルム貼り付けまたは印刷等により光乱反射素材を設置して文字または図形を成し、導光手段の第二表面側に光乱反射面を設置することにより、導光手段の内部を伝搬してきた光の一部が光乱反射素材で乱反射してさらに光乱反射面で再び反射して導光手段の第一表面側に出てくることで、導光手段の第一表面側から見たときに光乱反射素材の構成する文字または図形の周囲に光の縁取りを現出させる。

(もっと読む)

論理回路

【課題】CMOS半導体集積回路において、パリティ検査等の高速化のために排他的論理和の多段接続回路を高速化する。

【解決手段】2入力排他的論理和が2段以上連続する部分の各々の排他的論理和を相補入出力排他的論理和、すなわち2組の相補信号入力と1組の相補信号出力を有するものとして実現し、かつ正と負の前記相補信号出力を生成するために各々1個ずつのAOI22論理ゲートすなわちAND−OR−NOT複合論理ゲートまたはOAI22論理ゲートすなわちOR−AND−NOT複合論理ゲートを用いることで、排他的論理和1段あたりのゲート段数を削減し高速化する。

(もっと読む)

半導体集積回路

【課題】スタンダードセル方式のCMOS半導体集積回路にて、近接位置にある論理ゲートセル間の配線接続においても上層配線の配線資源を消費していたことにより、配線資源不足で論理ゲートセルの敷詰め密度を上げられず、レイアウト面積の増大を招いていた。

【解決手段】論理ゲートセルの端子構造を特別なものとし、論理ゲートセル同士を特定の近接位置に配置したときに、第一および第二の金属配線層のみで配線接続を完結することにより、上層の配線資源を増加させることでレイアウト面積を削減する。

(もっと読む)

半導体チップ搭載基板

【課題】半導体チップ搭載基板で、ワイヤーボンディング接続するときの金属ワイヤーの長さに制限をなくし、基板製造コストの上昇を防止する手段を提供する。

【解決手段】ボンディングワイヤー15により基板11上電極13とチップ12上電極14とを接続する過程で、基板上電極とチップ上電極の中間位置にて金属ワイヤーの一部がワイヤー固定手段16を介して基板に接する構造を形成する。これにより金属ワイヤーの形状が安定し長い金属ワイヤーが使えるため、離れた位置にある細密ではない形状の基板電極と接続が可能になり、基板製造コストが削減される。

(もっと読む)

パイプライン演算器

【課題】パイプライン演算器の構成と演算要素間の関係がある特定のものであるとき、演算要素を前段のパイプラインステージに移設することにより、演算機能の等価性を保ちつつ動作速度を向上する。

【解決手段】前段のパイプラインステージにある演算要素の入力部分に後段のパイプラインステージから演算要素を移設するときに、前記入力部分の入力数に応じて移設対象を複製し、また後段のパイプラインステージ数が複数あるときには、移設先演算要素を複製してパイプライン構造の組み替えを行い機能の等価性を確保しつつ高速化を果たす。

(もっと読む)

1 - 7 / 7

[ Back to top ]