マイクロン・テクノロジー・インコーポレーテッドにより出願された特許

11 - 20 / 55

微細形状ワークピースを機械的及び/又は化学機械的に研磨するためのアンダーパッドを含む研磨機及び方法

【課題】微細形状のワークピースを研磨するための研磨機及び方法を提供する。

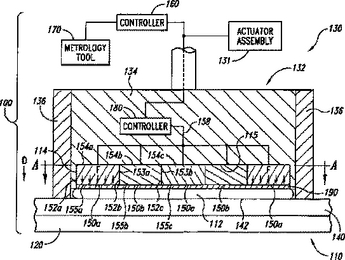

【解決手段】微細形状ワークピース(112)を機械的及び/又は化学機械的に研磨するための研磨機及び方法。一実施形態では、機械は、支持面を有するテーブル、支持面に担持されたアンダーパッド、及びテーブルの上のワークピースキャリアアセンブリ(130)を含む。アンダーパッド(150)は空洞(152)を有し、キャリアアセンブリは、微細形状ワークピースを担持するように構成されている。機械は、更に、空洞に磁場を発生するように構成された磁場供給源(170)と空洞内の磁気流動流体(160)とを含む。磁気流動流体は、磁場供給源の影響を受けて空洞内の粘性を変化させる。  (もっと読む)

(もっと読む)

微細形状ワークピースを機械的及び/又は化学機械的に研磨するためのシステム及び方法

【課題】微細形状のワークピースを研磨するためのシステム及び方法を提供する。

【解決手段】微細形状ワークピースを研磨するためのシステム及び方法。一実施形態では、方法は、微細形状ワークピースの特徴の状態を判断する段階と、微細形状ワークピースの特徴の状態を判断した後に、キャリアヘッド及び/又は研磨パッドを他方に対して移動して研磨パッドに対して微細形状ワークピースを擦る段階とを含む。キャリアヘッドはまた、複数の圧電部材を担持している。本方法は、更に、複数の圧電部材の少なくとも1つに電圧を印加することにより、判断された特徴の状態に応じて微細形状ワークピースの裏面に圧力を加える段階を含む。別の実施形態では、システムは、ワークピースキャリアアセンブリ、複数の圧電部材、研磨パッド、特徴の状態を判断するための測定ツール、及びコントローラを含む。コントローラは、上述の方法を実行するための命令を収容したコンピュータ可読媒体を有することができる。  (もっと読む)

(もっと読む)

抵抗メモリ検出時の電力消費量低減化方法

抵抗メモリを検出する際の電力消費量を低減させる装置及び方法を提供する。一端がノードにおける容量性素子(415)の端子に結合されるスイッチ(405)は、その他端から抵抗メモリアレイ(450)のビットラインに結合されている。ノードには更に、センス装置(425)が接続されており、このセンス装置において、スイッチが閉じたり開いたりして、ビットラインを経て転送される電圧信号をサンプリングして容量性素子に記憶させる。サンプリングされた信号は次にセンス装置(414)に転送され、このセンス装置が信号に関するセンス処理を実行する。  (もっと読む)

(もっと読む)

高速DRAMにおいて所望の読出しレイテンシを確立し維持する方法及び装置

【課題】メモリーデバイスにおいて、読出しクロックのデータフローに対する時間遅れ量の変動を補償して、指定の読出しレイテンシを維持する方法及び装置を提供する。

【解決手段】読出しクロックのデータフローに対する時間遅れ量の不確定性及び変動を補償して指定の読出しレイテンシを達成するために、外部クロック信号から導出した内部クロック信号の可変タイミングを管理する方法及び装置を提供する。DRAMの初期化において発生されるラスター信号が、外部クロックのサイクル数をカウントする第1カウンタを始動させ、遅延ロックループのスレーブ遅延線を通過して第2カウンタも始動させる。これらのカウンタは一旦始動すると連続的に動作し、これらのカウント値の差が内部遅延を外部クロック信号のサイクル数で表わす。内部読出しレイテンシを用いていずれかのカウンタをオフセットさせて、DRAM回路の内部読出しレイテンシを表わす。一旦、オフセットされていないカウンタがオフセットされたカウンタに等しくなると、読出しデータが指定の読出しレイテンシで出力線上に出て、外部読出しクロックと同期する。  (もっと読む)

(もっと読む)

堆積チャンバーの表面強化およびその結果得られる堆積チャンバー

基板上に薄膜を堆積させる装置内の露出表面を不動態化する方法が開示される。堆積チャンバーおよびその堆積チャンバーと連通している導管の内部表面が堆積プロセス中で使用される反応体および反応生成物が上記内部表面に吸着または化学吸着しないように不動態化される。これらの内部表面は、この目的にために、表面処理、ライニング、温度調節またはそれらの組み合わせによって不動態化することができる。ある表面を反応体および反応生成物の蓄積を最低限に抑えるように保持する温度または温度範囲を決める方法も開示される。堆積チャンバーおよびガス流路内に不動態化表面を有する堆積装置も開示される。  (もっと読む)

(もっと読む)

低電圧センス増幅器および方法

第1センス増幅器(110)は、一対の相補センス線(S、S*)間に接続された相補入力および出力を有する。各センス線(150、152)は、結合トランジスタを介して、各相補ディジット線(D、D*)に接続される。結合トランジスタは、初期センス期間に起動され、ディジット線からの差動電圧をセンス線に接続する。その後センス線は、ディジット線から分離され、ディジット線の容量からの負荷を受けることなく、第1センス増幅器を差動電圧に対応させる。また、センス線は、ディジット線に接続された相補出力を有する第2センス増幅器の相補入力に接続される。第2センス増幅器(120)をディジット線ではなくセンス線に接続することにより、第2センス線に印加された差動電圧は、ディジット線間の差動電圧よりも早く増加する。  (もっと読む)

(もっと読む)

異なったメモリ・アレイのカラムにより共有される電流制限ブリーダ・デバイスのための装置および方法

異なるメモリ・アレイのカラムの間で共用され、電源にかかる電流負荷を制限し、修復可能なメモリ・デバイスの故障を防止する電流制限ブリーダ・デバイスのための装置及び方法。メモリ・デバイスは、ローとカラムとに配列されたメモリセルを有する第一及び第二メモリ・アレイを含み、第一及び第二メモリ・アレイのカラムの各々は、それぞれのカラムを予備充電するための平衡回路を有する。ブリーダ・デバイスは、予備充電電圧源に結合され、第一メモリ・アレイ中のカラムの少なくとも一つの平衡回路及び第二メモリ・アレイ中のカラムの少なくとも一つの平衡回路にさらに結合され、予備充電電圧源から平衡回路へ流れる電流を制限する。  (もっと読む)

(もっと読む)

調整可能出力ドライバ回路

【課題】同期ダイナミックランダムアクセスメモリ(SDRAM)などの同期メモリにおける高速データ通信のための制御および論理レベル調整を提供する出力ドライバ回路。

【解決手段】レベル調整は、端末抵抗器と、出力ノードとVDDおよびVSS電源との間の制御可能なインピーダンスとの間の抵抗分割によって得られる。制御機能は、入力信号における遷移に応答して出力トランジスタを順次的にオンあるいはオフにすることによる出力ノードでの信号のスルーレート修正を含む。出力トランジスタの重み付けの異なる構成は、出力信号の異なる特性を得る。負荷整合回路および電圧レベル変換回路が、高周波数動作を改善するために記載される。

(もっと読む)

高速データ・サンプリング・システム

【課題】相対的に低速の回路を利用して相対的に高レートでアナログまたはディジタル・データ信号をサンプリングするシステムを提供する。

【解決手段】システム40はデータ信号を受信する複数のサンプル・アンド・ホールド回路42〜50を含んでいる。これらサンプル・アンド・ホールド回路は同一周波数であるが、相互に対して等位相でずれている、それぞれのクロック信号Φ1 …Φn によってクロックがとられている。サンプル・アンド・ホールド回路の各々は一連のシフト・レジスタ62〜70に接続されている。これらのシフト・レジスタは、それぞれのサンプル・アンド・ホールド回路によってとられたサンプルS1 …Sn を順次に格納するように動作する。シフト・レジスタの出力82〜90を、マトリックス・ディスプレイの列ドライバに印加する。

(もっと読む)

モジュール・レジスタを介する能動終端の制御

メモリーに能動終端制御信号を与えるモジュール・レジスタによりメモリーの能動終端制御を行う方法及び装置が提供される。モジュール・レジスタは、読出し及び書込みコマンドに関してシステム・コマンド・バスをモニターする。読出しまたは書込みコマンドを検知すると、モジュール・レジスタはメモリーへの能動終端制御信号を発生する。メモリーは、その1つまたは2つ以上のモード・レジスタにプログラムされている情報に基づき能動終端をターン・オンする。メモリーは、その1つまたは2つ以上のモード・レジスタにプログラムされている情報に基づき能動終端を所定の時間オン状態に維持する。  (もっと読む)

(もっと読む)

11 - 20 / 55

[ Back to top ]