サーノフ コーポレーションにより出願された特許

11 - 20 / 59

背面照射型撮像センサのスミアを低減する方法および装置

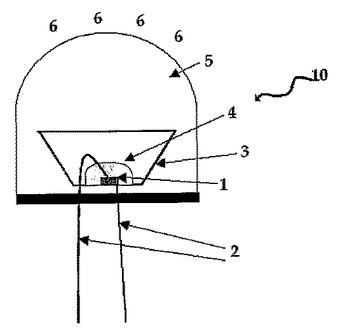

背面照射型半導体撮像デバイスを製作する方法および結果としてもたらされる撮像デバイスが開示される。この方法は、前面および背面を有する基板を設けるステップと、実質的に基板の前面の上に重なるエピタキシャル層を成長させるステップと、実質的にエピタキシャル層の中に少なくとも1つの障壁層を形成するステップと、少なくとも1つの電荷転送領域を備え、エピタキシャル層の上に重なり、かつエピタキシャル層中へ広がる少なくとも1つの撮像構造を製作するステップであって、少なくとも1つの障壁層が、少なくとも1つの電荷転送領域の下に実質的に存在するステップとを含み、基板の背面に入射する光が電荷担体を生成し、該電荷担体が、少なくとも1つの障壁層によって少なくとも1つの電荷転送領域から進路をそらされる。エピタキシャル層の少なくとも一部分は、エピタキシャル・ラテラル・オーバーグロース技法を用いて成長される。障壁層は、実質的にエピタキシャル層中に形成された高エネルギー・インプラント、光不透過材料で製作され酸化物で全側面を囲まれた光学シールドまたは両方の組合せであり得る。撮像構造は、CCDまたはCMOSの撮像構造であり得る。  (もっと読む)

(もっと読む)

クランプの静電放電保護

【課題】集積回路の保護回路内のSCRなどのESDクランプ用の、ESD保護回路を提供すること。

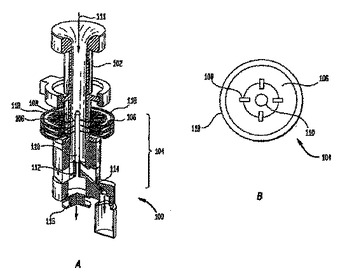

【解決手段】本発明の一実施形態では、SCRは、第1の低濃度ドープ領域内に形成された少なくとも1つの散在する第1の高濃度ドープ領域と、第2の低濃度ドープ領域内に形成された少なくとも1つの散在する第2の高濃度ドープ領域とを有する。回路は、SCRの高速かつ容易なトリガを実現するために、ESD電流を集めるように、SCRの少なくとも1つのトリガ・タップに接続された、少なくとも1つのガードリングをさらに備える。

(もっと読む)

ラッチアップのリスクが低減された静電放電保護構造

【課題】本発明は、保護された回路を有する半導体集積回路(IC)内のESD保護回路であって、ESDクランプの誤トリガが防止されるESD保護回路を提供する。

【解決手段】回路は、ESDクランプとして、第1の電圧源に結合するように適合されたアノードおよび第2の電圧源に結合するように適合されたカソードを有するSCRを含む。回路はまた、SCRの少なくとも1つの第1のトリガ・タップと第1の電圧源の間に結合された少なくとも1つのノイズ電流バッファ(NCB)を含み、SCRの第1のトリガ・タップは電源に結合されるようになる。

(もっと読む)

電力状態の検出によるESDクランプ制御

本発明によれば、デバイスの望ましくないトリガリングを防止するためのトリガ回路を制御することにより、ESD保護回路に対する改善が提供される。回路はESDクランプを備えており、該クランプにトリガ回路が結合されている。クランプおよびトリガ回路は、いずれも第1の基準電位に結合されている。回路は、さらに、トリガ回路に結合された制御ラインを備えている。制御ラインは第2の基準電位に結合されており、この第2の基準電位に電力が供給されるとトリガ回路を不能にし、また、第2の基準電位に電力が供給されない場合、トリガ回路を使用可能状態にするようにトリガ回路の挙動をさらに制御している。  (もっと読む)

(もっと読む)

湿気保護蛍光体およびLED照明デバイス

本発明によれば、酸化物のコーティングでコーティングされたフォトルミネセント・蛍光体であって、(1)(a)金属チオガレイト・蛍光体および(b)金属硫化物蛍光体から選択される無機蛍光体と、(2)少なくとも1つの酸化物を有する少なくとも1つの層を備えたコーティングとを備えたフォトルミネセント・蛍光体が提供される。本発明によるコーティングされたフォトルミネセント・蛍光体は、コーティングされていない場合より耐水誘導劣化性が優れている。  (もっと読む)

(もっと読む)

金属ケイ酸塩ハロゲン化物蛍光体およびそれを使用するLED照明デバイス

本発明は、いくつかの金属ケイ酸塩ハロゲン化物(ハロシリケート)蛍光体、酸化物被覆を備えた蛍光体、蛍光体の作製方法、および蛍光体により変更された発光ダイオード(LED)ベースの照明デバイスに関する。  (もっと読む)

(もっと読む)

ハイブリッドのピクセル配列を有するCMOSイメージ・センサ

本発明の実施形態は、高速度、高解像度イメージ処理のためのシステムと方法に関し、それは、少なくとも1つのマクロピクセル、およびマクロピクセル・セレクタ・モジュールを含むマイクロピクセル配列と、マクロピクセル配列と結合されており、少なくとも1つのマイクロピクセル、マイクロピクセル・セレクタ・モジュール、およびアナログ・デジタル変換器を含むマイクロピクセル配列と、グローバル・バンチ・カウンタとを含む。  (もっと読む)

(もっと読む)

ビデオ・テストのためのエラー可視性の強化方法

テスト中のデコーダを評価するシステムおよび方法は、第1イメージを含む第1テスト・フレーム部分を作成するために、ビデオ・シーケンスの第1区分を記憶するステップと、第2イメージを含む第2テスト・フレーム部分を作成するために、ビデオ・シーケンスの第2区分を記憶するステップと、第1テスト・フレーム部分と第2テスト・フレーム部分とを組み合わせて視覚化区分にするステップと、視覚化区分をデコーダに流入させるステップと、結果として生じたテスト中のデコーダからの出力ストリームを表示するステップと、表示されたデコードされた出力ストリームの中に欠陥が存在するかどうかを判定するステップとを含むことが可能である。欠陥が存在するかどうかを判定するステップは、表示された視覚化区分のディスプレイが安定した画像を示す場合に、デコードされた画像の中に欠陥があると判定するステップと、視覚化区分のディスプレイが明滅または点滅している細部を示す場合に、デコードされた画像の中に欠陥があると判定するステップとを含むことが可能である。  (もっと読む)

(もっと読む)

静電放電保護回路

本発明は、マルチトリガリング問題を低減しかつ回路のESD性能を増大するために異なるフィンガまたはSCRを結合する利点を有する、複数のSCRフィンガ(SCR)を有するシリコン制御整流器(SCR)を有する静電放電(ESD)保護回路を提供する。さらに、ブースト回路が導入されることができ、またはさらに、複数SCRが、共通ベースを通して固有に結合されることができる。  (もっと読む)

(もっと読む)

静電式粒子捕集システムのためのバラスト回路

本発明は、多電極コロナ放電アレイのためのバラスト回路およびそれを製造するための方法を提供する。この回路は、導電性プラスチック材料と導電性プラスチック材料から突き出ている少なくとも1つのコロナ電極とを備える。プラスチック材料とコロナ電極との間の距離は電気抵抗を変化させて制御し、回路の電圧絶縁破壊を決定する。さらに粒子捕集表面を備える。粒子捕集表面は、回路設計および構成に応じて、導電性プラスチック材料の内部に配置したり、あるいは電性プラスチック材料から離して配置することができる。  (もっと読む)

(もっと読む)

11 - 20 / 59

[ Back to top ]