Fターム[2G132AC09]の内容

Fターム[2G132AC09]の下位に属するFターム

実回路からの出力を解析するもの (42)

回路設計のためのもの (122)

ハードウェアシミュレーション、模擬回路 (31)

Fターム[2G132AC09]に分類される特許

1 - 20 / 136

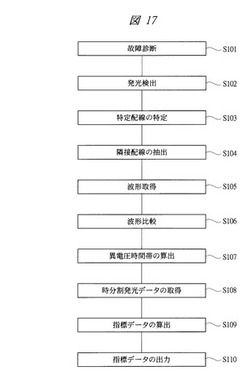

半導体装置の不良解析方法ならびに不良解析装置および不良解析プログラム

【課題】半導体装置の不良解析技術において、解析成功率の向上や解析時間の短縮を図ることができる技術を提供する。

【解決手段】ショートしていると推測される一方の特定配線を特定(S103)し、その相手と推測される隣接配線の抽出(S104)をおこない、両配線間において電圧状態(論理状態)が異なる異電圧時間帯の算出(S107)をし、その異電圧時間帯で発生する発光現象の頻度を調査することにより、上記一方の特定配線に対して、どの隣接する配線がショートしているのかを短時間で確実に推定する。

(もっと読む)

故障箇所推定システム、故障箇所推定方法及び故障箇所推定用プログラム

【課題】テスト時間の増大を抑制し、スキャンチェーンの故障診断を容易化し故障箇所推定用の故障診断時間の短縮を図る。

【解決手段】スキャンチェーン上の故障の範囲を絞り込むシステムは、バイパステストモードでのテストパタンと、圧縮テストモードでのテストパタンの両方で故障候補スキャンFFを絞り込む手段24と、圧縮テストモードとバイパステストモードでのスキャンチェーン構造の差異から圧縮テストモードにおける故障スキャンチェーンを特定して記憶部に記憶する手段23と、バイパステストモードの故障候補の範囲を圧縮テストモードのスキャンFFの範囲に変換する手段27と、圧縮テストモードのテストパタンを用いて故障候補を含むスキャンチェーンの故障シミュレーションを実行し、圧縮テストモードのテスト結果と照合し、照合結果を出力装置に出力する手段25を備える。

(もっと読む)

半導体集積回路及びその設計方法

【課題】半導体集積回路の外部端子としてTRSTがなくても、論理シミュレーションの際に、タップコントローラのステートを確定する。

【解決手段】タップコントローラ2は、リセット端子(端子p4)を有し、回路部3は、タップコントローラ2における状態遷移を制御するステート制御信号と、クロック信号を入力し、ステート制御信号とクロック信号に応じて、リセット端子p4にリセット信号を供給することで、タップコントローラ2のステートを確定する。

(もっと読む)

故障箇所推定装置と方法並びにプログラム

【課題】スキャンテスト設計が施された機能ブロックと付加回路とを含む論理回路全体を故障診断を可能とし、診断処理時間を大幅に短縮可能とする装置、方法の提供。

【解決手段】論理回路内のスキャンフリップフロップで構成されるスキャンチェーンの構成情報、論理回路の設計情報を入力データ1として入力し、論理回路においてパラレル領域以外の回路部をシリアル領域として抽出することで、前記論理回路を前記パラレル領域とシリアル領域に分割する回路分割手段2と、正常回路における論理値を期待値として求める期待値計算手段3と、テストパタンに対する論理回路のテスト出力を入力データ1として入力し、テスト出力および、シリアル領域とパラレル領域の期待値を用いて、パラレル領域およびシリアル領域を故障診断し、出力部に出力する故障診断手段4とを備える。

(もっと読む)

解析プログラム,解析装置および解析方法

【課題】スピードパス解析の解析精度を向上させる技術を提供する。

【解決手段】第1の解析部15は,パス遅延情報記憶部120から,テスト対象回路に対するディレイテストの結果から得られるパス遅延の実測値を取得する。第1の解析部15は,予測値記憶部130から,テスト対象回路に対するタイミング解析により得られるパス遅延の予測値を取得する。第1の解析部15は,特徴値記憶部140から,遅延に影響する要因ごとの特徴値を取得する。第1の解析部15は,取得したパス遅延の実測値と,パス遅延の予測値と,要因ごとの特徴値とを用いて,要因ごとの特徴値からパス遅延の実測値と予測値とのずれを算出するずれ算出モデルを求める。このとき,第1の解析部15は,パス遅延の実測値が得られない活性化パスについて,パス遅延の実測値の代わりにディレイテストで測定した最大周波数に対応する遅延の値を用いて,解析を行う。

(もっと読む)

テスト装置、テスト方法、プログラム及び記録媒体

【課題】 テストパワー考慮型のテスト生成において、テストパターン安全性を保証することを達成するテスト装置等を提供する。

【解決手段】 論理回路の故障の有無を判定するテスト装置であって、初期テストキューブが与えられ、初期未定値ビットに論理値を割り当てて中間テストパターンを生成する手段と、テストパターンが印加された論理回路に故障がなければ危険ビットが存在しないというテストパターン安全性を判定する手段と、テストパターン安全性を保証することに寄与しうる候補ビットを特定する手段と、初期未定値ビットにも候補ビットにも対応した中間テストパターンの入力ビットを新規未定値ビットとして新規テストキューブを生成する手段と、新規未定値ビットに論理値を割り当てて最終テストパターンを生成する手段と、最終テストパターン安全性を判定する手段と、論理回路テストにおいて危険ビットを使用させないマスク手段とを備える。

(もっと読む)

半導体集積回路装置、スキャンテスト回路設計方法、スキャンテスト回路設計装置

【課題】複数のスキャンパスを有するスキャンテスト回路のスキャンテスト時間を短縮する。

【解決手段】半導体集積回路装置は、複数のスキャンフリップフロップと、セレクタとを備える回路ブロックと、制御回路とを具備する。複数のスキャンフリップフロップは、スキャンテストするときに、スキャンフリップフロップがシフトレジスタ状に接続されて形成される複数のスキャンパスのそれぞれに割り当てられ、複数のスキャンパスと同数の複数の部分スキャンパスを形成する。セレクタは、複数の部分スキャンパスの後段に設けられ、複数の部分スキャンパスをバイバスする。制御回路は、セレクタが複数の部分スキャンパスをバイパスするか否かを制御する。

(もっと読む)

テストパタン生成システム、テストパタン生成方法、およびテストパタン生成プログラム

【課題】ATPGにおけるテストパタンの生成時間を短縮するための技術を提供する。

【解決手段】EDAツール(11〜16)と、EDAツール(11〜16)が参照する情報を保持するファイル格納部(9)とを具備するテストパタン生成システムを構成する。そのファイル格納部(9)は、テストパタンの生成の対象となる回路の接続情報を示すネットリスト(21)と、ネットリストに示される回路のうち、故障検出の対象となる故障検出対象領域の起点となる端子を示す始終点リスト(22)とを備えるものとする。そのロジックコーン抽出部(11)は、始終点リスト(22)に示される起点を頂点とするロジックコーン(34)(35)を特定する。また、故障リスト生成部(12)は、組み合わせ回路(32)(33)に含まれる全てのノードから、ロジックコーンに含致しないノードを除外して故障リスト(24)を生成する。

(もっと読む)

カレントプローブモデル化方法、カレントプローブモデル作成装置、シミュレーション方法、シミュレーション装置、及びプログラム

【課題】BCI試験のシミュレーションをより短時間に行えるようにする技術を提供する。

【解決手段】BCI試験で伝送線にバルク電流の注入に用いるカレントプローブは、伝送線にバルク電流を直接、注入する電圧源と見なし、モデル化する。それにより、カレントプローブは電圧源モデル20で模擬する。カレントプローブは電圧の印加により信号線に電流を注入する。そのようにして注入される電流は、周波数と電圧振幅値のテーブルデータ25に格納された周波数と電圧振幅値の組み合わせにより制御する。このために、周波数と組み合わせる電圧振幅値は、その周波数で実際に注入される電流の電流振幅値と、電圧源モデル20と伝送線を含む測定用回路のシミュレーションにより得られるその電流振幅値とが一致するように選択される。

(もっと読む)

回路設計方法、プログラム及び半導体集積回路

【課題】短時間で効率的に回路設計を行う。

【解決手段】階層設計データの各階層(図1の例では、トップ階層と下位階層)の回路ブロックに含まれる試験回路モデル4,5,9,10を、階層内及び階層間でシリアル接続し、自身の階層の試験回路モデル4,5,9,10を経由した試験データ(試験結果)か、自身の階層の試験回路モデル4,5,9,10を経由しない試験データの何れかを選択して出力する選択部6,11を各階層に設ける。

(もっと読む)

活性化パス抽出プログラム,活性化パス抽出装置および活性化パス抽出方法

【課題】実チップの遅延試験の際に信号が伝播した活性化パスを高速に抽出する。

【解決手段】遅延試験の際のテストパターンと実チップのネットリストとに基づき遅延試験のシミュレーションを行なうことにより遅延試験の際に信号値が変化した信号値変化ピンを特定するシミュレーション部11と、このシミュレーション部11によって特定された信号値変化ピンと実チップのネットリストとに基づき信号値変化ピンを辿ることにより活性化パスのトレースを行なうパストレース部12とがそなえられる。

(もっと読む)

タイミング検証装置、及びタイミング検証方法

【課題】アドレスのセットアップ(Setup)違反とホールド(Hold)違反が同じクロックのイベントに対して発生した場合に、アドレスのタイミング違反が発生しても、仮想イベントを発生させることなく、対象の違反アドレスを正しく判定する。

【解決手段】イベントドリブン方式を用いた論理シミュレーションに適用される半導体装置内蔵ランダムアクセスメモリのタイミング検証装置において、クロック信号にイベントが発生した場合、当該ランダムアクセスメモリのアドレス違反処理用レジスタに現状のアドレス情報を格納する。また、アドレスのタイミング違反を確認する。また、タイミング違反を確認した結果に基づき、タイミング違反時にアドレス違反処理用レジスタの値を不定値にする。また、タイミング違反レジスタの値に基づき、違反アドレスをチェックする。

(もっと読む)

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

試験装置

【課題】電源電圧変動を補償可能な試験装置を提供する。

【解決手段】電源補償回路12は、スイッチ素子12b、12cがオンした状態において補償パルス電流ISRC、ISINKを生成する。パターン発生器PGは、ドライバDR1〜DR4が出力すべき試験信号STESTを記述するテストパターンSPTN1〜SPTN4と、ドライバDR5、DR6が出力すべき制御信号SCNT2、SCNT1を記述する制御パターンSPTN5、SPTN6を生成する。電圧測定部20は、キャリブレーション工程において、電源電圧VDDを測定する。電流調節部22は、測定された電源電圧VDDに応じて、キャリブレーション後の試験工程において生成すべき補償パルス電流ISRC、ISINKを調節する。

(もっと読む)

故障診断装置、故障診断方法、及び故障診断プログラム

【課題】実測とシミュレーション結果に不一致が生じた場合に、不一致を生じている経路数だけでなく、不一致の時間的な大小を評価する。

【解決手段】本発明では、回路の後方追跡により抽出した故障候補から、候補の出力側に存在するスキャン回路(SFF)までの故障伝搬経路を、デジタル信号が伝搬する際に費やす遅延時間を求め、実測のテスト結果が不合格である経路の遅延が、合格である経路よりも大きい故障候補を、真の故障であると判定し、その大小関係に逆転(不一致)が生じた場合は、その時間的な逆転が統計的に小さい故障候補を、真の故障であると判定する。遅延が大きい経路は、それが小さい経路に比べて回路動作における時間的なマージンが小さく、遅延故障が発生した場合にテスト結果が不合格になりやすい。そのため、実測のテスト結果の合格/不合格と遅延時間の大小が上記に従う故障候補は、真の故障である可能性が高い。

(もっと読む)

半導体集積回路のシミュレーション装置、シミュレーション方法およびシミュレーションプログラム

【課題】検証対象の回路が要求特性を満たしているか否かを、製造ばらつきを考慮して短時間で実行。

【解決手段】回路のネットリストを格納する回路情報格納部10と、検証する第1回路特性の種類を提供する検証項目提供部20と、各種素子の特性を、製造ばらつき範囲の下限値、Typ値、上限値の複数のパラメータファイルを格納するパラメータ格納部40と、回路に含まれる第1素子及び第2素子のそれぞれに対して、最小値用又は最大値用ばらつき項目リスト生成部50と、最小値と最大値との少なくとも一方を検証することを含むシミュレーション条件提供部60と、最小値と最大値との少なくとも一方を検証する情報に基づいて、製造ばらつき情報を生成する製造ばらつき情報生成部70と、製造ばらつき情報と、ネットリストと、シミュレーション条件とに基づいて、回路シミュレーションを実行する回路シミュレーション実行部90とを具備する。

(もっと読む)

タイミング解析方法、プログラム、及びシステム

【課題】IRドロップの影響を考慮して半導体集積回路のタイミング解析を行うこと。

【解決手段】タイミング解析方法は、(A)遅延変動率と電圧変動との関係を示す遅延電圧関数を算出するステップと、(B)IRドロップによる電圧変動と距離との関係を示す電圧距離関数を算出するステップと、(C)遅延電圧関数と電圧距離関数を組み合わせることによって、IRドロップによる遅延変動率と距離との関係を示す遅延距離関数を算出するステップと、(D)距離に依存するOCV係数を、遅延距離関数を用いることによって補正するステップと、(E)補正後のOCV係数を用いて、対象回路のタイミング解析を実行するステップと、を含む。

(もっと読む)

論理回路の故障箇所推定システムと故障箇所推定方法及び故障箇所推定プログラム

【課題】論理回路内部のスキャン・チェイン上の単一固定故障に対して、スキャン・チェインに特化した故障辞書を用いて、テスト結果と照合することで、処理時間を短縮して推定する。

【解決手段】論理回路の構成情報と、スキャン・テストパタンと、故障スキャン・チェイン特定手段22と、スキャン・チェイン故障辞書を作成しスキャン・チェイン故障辞書記憶部34に記憶するスキャン・チェイン故障辞書作成手段25と、故障スキャンFF絞り込み手段23と、フェイル出力情報を階層毎に比較照合して一致する故障候補箇所のパスビットも含めた一致率を算出し、スキャン・チェイン名(番号)とスキャンFF名とスキャン・ビット番号と信号線と信号線分岐と故障種別と一致率とレイアウト情報と近接信号線情報を、故障推定結果として出力するスキャン・チェイン故障辞書照合手段26を備える。

(もっと読む)

論理検証シナリオ生成装置、及び、論理検証シナリオ生成プログラム

【課題】CPUの論理検証に用いる検証シナリオ、及び期待値の生成負荷を抑える。

【解決手段】RTL記述されたCPUの論理検証のためのテストプログラムを生成する論理検証シナリオ生成装置であって、テストライブラリと、期待値フォーマット記憶部と、検証命令アドレス、前命令空間、後命令空間、データ空間、分岐命令空間、スタック空間とを有するメモリモジュールであって、テストライブラリから順次選択した検証命令と前後命令組合せとに基づいて、検証命令アドレスに検証命令を、前命令空間に前命令を、後命令空間に後命令を記憶し、前命令が分岐命令である場合に前命令の分岐先アドレスに検証命令アドレスを記憶したメモリモジュールをテストプログラムとして生成するテストプログラム生成部と、テストプログラムの各命令について期待値フォーマットを取得し、当該命令をデコードしたデコード情報に基づいて期待値を生成する期待値生成部と、を有する。

(もっと読む)

集積回路、シミュレーション装置、及びシミュレーション方法

【課題】LSIを実際の使用形態に沿って動作させるような入力パターンを用いて、LSI内部の遅延故障をLSI外部において効率良く検出することを目的とする。

【解決手段】開示の装置は、LSIのディレイテスト用のディレイテストパターンを生成する制御を行う。入力パターン制御回路は、被試験対象回路へ供給される入力パターンのサイクル数をカウントし、予め設定されたカウント数と一致した時点で、被試験対象回路への入力パターンの供給を停止し、入力パターン保存回路は、このような入力パターンを保存する。スキャン制御回路は、入力パターン制御回路からの制御信号を受け、被試験対象回路へスキャンシフト信号を供給し、被試験対象回路内のスキャンチェインをシフトさせる。そして、期待値生成回路は、スキャンチェインの出力を期待値データとして保存する。

(もっと読む)

1 - 20 / 136

[ Back to top ]