Fターム[2G132AC11]の内容

Fターム[2G132AC11]に分類される特許

1 - 20 / 122

半導体集積回路設計装置、半導体集積回路設計方法、および、プログラム

【課題】半導体集積回路において、スキャンテスト時における消費電力を削減する。

【解決手段】半導体集積回路設計装置は、第1のスキャンFFのデータ入力端子に接続された第1のロジックコーンの入力端子数である第1の入力端子数と、第1のロジックコーンにデータを設定する第2のスキャンFFのデータ入力端子に接続された第2のロジックコーンの入力端子数である第2の入力端子数とを比較するデザイン解析部と、複数のスキャンFFのそれぞれのデータ入力端子に接続されたロジックコーンの入力端子数、および、複数のスキャンFFのそれぞれを第1のスキャンFFとした場合の前記比較結果に応じて、複数のスキャンFFを複数のグループに分類し、複数のグループのそれぞれに含まれるスキャンFFを相互に接続したスキャンチェーンを複数のグループのそれぞれについて生成するスキャンチェーン構築部と、を備える。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

システムデバッグ装置及びシステムデバッグ方法

【課題】FPGAの回路規模を大きくすることなく、システムLSIの全ての信号をデバッグし得るデバッグシステム装置を提供する。

【解決手段】システムデバッグ装置は、複数のコア回路を備えるシステムLSIと再構成可能回路が積層されて成り、システムLSIは、設計者により選択された複数のコア回路のうちの一部のコア回路に対して入力される入力信号を再構成可能回路に送信する送信手段を備え、再構成可能回路は、複数のコア回路のうち指定されたコア回路を再構成し、システムLSIから送信された入力信号を入力として、再構成回路を動作させて得られる実行信号を出力する出力手段を備える。

(もっと読む)

論理回路検証装置、論理回路検証方法およびプログラム

【課題】論理シミュレーションに基づく論理回路の検証に要する時間を削減すること。

【解決手段】論理回路検証装置は、複数のモジュールを有する論理回路に対する論理シミュレーションを行うとともに、該複数のモジュールのそれぞれに対するコード・カバレッジ(コードの網羅率)を取得する論理シミュレータと、複数のモジュールのそれぞれに対するコード・カバレッジを参照し、コード・カバレッジが所定の割合よりも低いモジュールに対して第1のHDLコードを用いるとともに、それ以外のモジュールに対して第1のHDLコードに対するモデルよりも抽象度の高いモデルに基づく第2のHDLコードを用いて論理シミュレーションを行うように、論理シミュレータに指示するカバレッジアクセラレータと、を備えている。

(もっと読む)

指標算出プログラム及び方法並びに設計支援装置

【課題】半導体装置の故障を減らすために実施すべき設計変更等に対する指標を与える。

【解決手段】本方法は、半導体装置上に実装された回路のグループ毎に当該グループにおいて発生した実故障数と故障要因となる各特徴についての特徴量とを格納する第1データ格納部に格納されているデータを用いて、互いに独立な特徴を抽出するステップと、実故障数の総和を半導体装置の数で除することによって得られる故障発生確率を、抽出された特徴の各々の特徴量と対応する係数との積の和を含む関係で表す故障発生確率モデル式を、第1データ格納部に格納されているデータを用いて回帰計算を実施することで生成するステップと、生成された故障発生確率モデル式から、半導体装置の設計変更のための指標値を算出し、第2データ格納部に格納する指標算出ステップとを含む。

(もっと読む)

シミュレーションネットリスト作成装置、シミュレーションネットリスト作成方法、及びコンピュータプログラム

【課題】 回路における電源制御に関するシミュレーションの時間を削減する。

【解決手段】 回路を構成する部品の「部品情報110、端子情報120、及び端子間の接続情報100」に基づき、探索開始部品を特定する。そして、探索開始部品の電源端子及びリセット端子と、電源回路の制御ネット名とを探索始点とする。また、電源回路の入出力ネット名と、電源ネット名と、グランドネット名と、部品情報110に基づいて特定される探索終了部品とを探索終点とする。そして、探索始点から探索終点までの探索経路にある部品を探索し、当該部品の接続情報を特定し、探索経路にある部品のシミュレーションネットリストを作成する。

(もっと読む)

スキャンチェーン形成方法、プログラム及び設計支援装置

【課題】タイミングエラーを解消しつつも、遅延素子の増加及び試験コストの増大を抑制することのできるスキャンチェーン形成方法を提供する。

【解決手段】複数のスキャンFFを、各スキャンFFのスキャン端子間の配線長が最短となるようにスキャンチェーンを形成する。その後、複数のスキャンFFのうちタイミングエラーの発生した対象スキャンFFを中心とした、タイミングエラーの発生しない座標集合X3を算出し、その座標集合X3内に配置されたスキャンFFの中から、リオーダー処理前のスキャンチェーンのつなぎ順をできる限り保持するように1つのスキャンFFを選択する(ステップS17〜S19,S23)。続いて、その選択したスキャンFFと対象スキャンFFとを接続するようにつなぎ順を変更する(ステップS20)。

(もっと読む)

信号観測装置および信号観測方法

【課題】半導体集積回路を対象とした実機によるレジスタ転送レベルでの動作検証にあたり、回路規模を増大させることなく回路内部の信号の観測を行う。

【解決手段】信号観測回路310のハッシュ値保持部320は、観測期間の開始タイミングに応じて外部から供給される初期ハッシュ値を、現ハッシュ値の初期値として保持する。以降、信号観測回路310のハッシュ値算出部311は、観測対象回路210から入力される観測対象信号と現ハッシュ値を利用して次のハッシュ値を算出する。ハッシュ値保持部320は、保持制御部330の制御に応じて、ハッシュ値算出部311により算出されたハッシュ値を現ハッシュ値として保持する。観測期間が終了した段階において得られている現ハッシュ値Hnが観測対象信号の観測結果となる。

(もっと読む)

モデル式生成方法、装置及びプログラム

【課題】SRAM設計のためのモデル式を生成するために実行するシミュレーション回数を削減する。

【解決手段】所定の指標についての平面における歩留検討対象の四辺形の頂点におけるスタティックノイズマージンSNM及びライトマージンWMのモデル式を生成する場合に、指定頂点の各々におけるSNM及びWM間の推定される関係に応じて予め設定されている重み値に応じて、初期シミュレーション回数を、指定頂点の各々におけるSNM及びWMの各々に配分し、所定パラメータ値を変動させつつ配分回数分シミュレーションを実施させる。また、初期のシミュレーション結果からモデル式を生成し、当該モデル式の近似精度評価指標値を算出し、当該モデル式が、予め定められている歩留モデル式に対する影響の有無を判定する。そして、各モデル式について、近似精度評価指標値及び歩留モデル式に対する影響の有無に応じて追加シミュレーションの要否を判定する。

(もっと読む)

半導体集積回路の論理検証にて使用するテストタスクの生成方法

【課題】SoCデバイスの検証作業において、ハードウェアモデルシミュレーションにて発生した不具合を早急かつ少ない工数で論理検証において再現させることを可能にする。

【解決手段】ハードウェアモデルシミュレーションにて不具合を発生させたテストプログラムにしたがって、そのSoCデバイスのソフトウェアモデルを動作させ、その動作の過程で発生するメモリアクセス、メモリの更新待ち、レジスタアクセス、およびレジスタの更新待ちの各々をRTLに変換しつつその発生順にログに記録する。そして、当該ログをテストタスクとして論理検証を実行する。

(もっと読む)

論理検証実行システム

【課題】

乱数要素を持たせた論理検証において、検証論理にあるフリップフロップのうち全く動作しないものや、動作回数が著しく低いものがある。そして、検証論理に含まれるフリップフロップ全てがあらゆる条件下で動作するまで検証を行うと検証期間の増大する。

【解決手段】

検証論理に入力する命令およびデータのパターンを乱数を用いて生成するための制約条件を定義したシナリオファイルを複数用意し、複数のファイルから実行対象とするファイルをランダムに選び、検証実行時にカバレッジ情報を出力し、蓄積したカバレッジ情報を用いて低動作回数フリップフロップを抽出し、抽出したフリップフロップを動作させたファイルが多く実行されるように動作回数に応じて実行確率を算出する処理を行うことで、抽出したフリップフロップを動作させたファイルの実行回数を上げ、検証論理にある全フリップフロップの動作回数を平均的に上げ、効率がよい論理検証を可能にする。

(もっと読む)

バックアノテーション装置

【課題】効率的にバックアノテーションを実行する。

【解決手段】Pre-layoutシミュレーションを実行し、シミュレーション実行時に電位の変化したノード(アクティブノード)を抽出する(S1)。レイアウトパターンデータに対してレイアウトパターン検証を行なう(S2)。S1のPre-layoutシミュレーション時に抽出されたアクティブノード情報に基づいて、レイアウトパターンデータより寄生素子が抽出され、レイアウトパターンデータのすべてのデバイスと抽出された寄生素子情報を含んだ寄生素子付ネットリストが生成される(S3)。生成されたネットリストに基づいてPost-layoutシミュレーションが実行される(S4)。

(もっと読む)

半導体集積回路の設計装置及び設計方法

【課題】配線混雑を招いたり、他のセルの配置の障害となることなく、且つタイミングエラーを起こさずに複数のタイミング調整用バッファを駆動させることが可能な半導体集積回路の設計装置及び設計方法を提供することを目的とする。

【解決手段】上記課題は、バウンダリスキャン機能を有する半導体集積回路の設計装置であって、複数のタイミング調整用バッファ間の距離を算出する距離算出手段と、前記距離算出手段により算出された距離に基づき、所定期間内にコントロール信号により前記複数のタイミング調整用バッファが駆動するように、複数のバウンダリスキャンレジスタを前記コントロール信号の供給元の後段に挿入する挿入手段と、を有する半導体集積回路の設計装置により達成される。

(もっと読む)

統計SPICEモデルパラメータ算出方法、統計SPICEモデルパラメータ算出装置及びプログラム

【課題】高精度かつサイズ依存性を持ったばらつきモデルを作ることができる統計SPICEモデルパラメータ算出方法の提供。

【解決手段】多点測定した半導体デバイスの素子特性値の実測値をデバイスサイズ毎に主成分分析する(主成分分析工程)。前記デバイスサイズ毎に得られた主成分分析の結果と、予め決定したデバイスサイズ依存性と、に基づいて、複数のデバイスサイズにおける素子特性値のばらつきを再現する統計SPICEモデルパラメータを算出する(パラメータ算出工程)。

(もっと読む)

回路試験装置、回路試験プログラムおよび回路試験方法

【課題】設計対象回路についての故障検出率を省力的かつ効果的に向上させる。

【解決手段】回路試験装置100は、顧客ニーズに応じた機能を備えた設計対象回路の設計データを取得すると、この設計対象回路のうち、試験対象に指定された対象回路102がOR回路かAND回路かに応じて、故障検出を可能にするための回路試験機構110を生成する。また、回路試験装置100は、生成した回路試験機構110によって、対象回路102の動作試験を実行する機能も備えている。

(もっと読む)

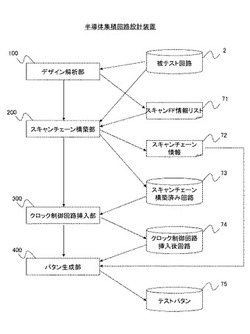

テスト回路設計プログラム、テスト回路設計装置およびテスト回路設計方法

【課題】遅延を発生させることなく、高精度なテスト用クロックを提供すること。

【解決手段】テスト回路設計装置100では、テスト対象回路110の中からテスト対象FF111が指定されると、ネットリスト101を参照して、入力端子(クロック入力端子およびクロック制御信号入力端子)からテスト対象FF111までの間に構成されている論理回路を、テスト対象回路110に入力される各クロック(ここでは、クロックA,B)の中から選択されたクロックをテストクロックとしてテスト対象FF111に入力する機構を備えた回路であるテスト用論理回路に修正したテスト対象回路120を構成する。

(もっと読む)

半導体集積回路の遅延解析方法

【課題】DPSNを考慮した遅延計算と同程度の高い精度を持ちながら、コンピュータの処理時間を短縮した半導体集積回路の遅延解析方法を提供する。

【解決手段】1)DVDAは、半導体集積回路の中から抽出された1つのデータパス回路における遅延差係数を決定するためのみに使用される。2)遅延差係数はAPSNを考慮した遅延計算の結果へ追加される。3) 遅延差係数を決定した後は、DPSNを考慮した遅延計算を省略する。そして、半導体集積回路の残りのデータパス回路(クロックパス回路も含む)について、遅延差係数を用いたAPSNを考慮した遅延計算が行われ、その時に、遅延差係数が複数のデータパス回路に共通に用いられる。

(もっと読む)

故障検出率向上用回路挿入方法

【課題】想定外の遅延による回路のパフォーマンス低下を回避可能な故障検出率向上用回路挿入方法を得ること。

【解決手段】本発明は、HDL記述による論理回路設計において、論理回路の故障検出率を向上させるための故障検出率向上用回路を挿入する場合の故障検出率向上用回路挿入方法であって、コンピュータの制御部が、論理合成により得られるネットリスト3を入力としてATPGを適用して故障検出率を算出し、また、ネットリスト3に基づいて仮配置配線を行い、目標となる故障検出率に達していない場合に、論理設計ファイル1,制約情報2,ネットリスト3,未検出故障情報4,遅延情報ファイル5およびタイミング制約ファイル6等に基づいて、故障検出率向上用回路を挿入する未検出故障箇所を決定する。

(もっと読む)

論理動作検証システム、論理動作検証方法、及びプログラム

【課題】イベント同時発生時の競合状態を全て検出する。

【解決手段】論理動作検証システムは、HDL(Hardware Description Language)言語によって記述された論理シミュレーションを実行するシミュレータと、論理シミュレーションの実行中のイベント時の信号状態及びシミュレーション時刻を示す情報を記憶する信号状態・シミュレーション時刻記憶手段と、現イベント時の信号状態と影響のある信号のイベント時の信号状態とを検証する第1動作検証手段と、現イベント時の時刻と影響のある信号のイベント時の時刻とを比較する第1動作間時刻差検証手段と、現イベント時の信号状態と影響のある信号の前イベント時の信号状態とを検証する第2動作検証手段と、現イベント時の時刻と影響のある信号の前イベント時の時刻とを比較する第2動作間時刻差検証手段とを含む。

(もっと読む)

シミュレーション装置およびシミュレーション方法

【課題】アサーション記述のハードウェア化に伴う回路規模の増大を防ぐ。

【解決手段】プログラマブル回路102は、動作クロック生成回路104のクロック信号に同期して動作する設計対象回路106を実装し、回路106に対するアサーション検証開始の信号を生成するアサーショントリガ検出回路(検出回路)107_1〜107_nおよびアサーション検証の結果判定を行うアサーション条件判定式回路(判定回路)108_1〜108_nを含む。コンピュータ100は、回路106のシミュレーション結果を判定するアサーション結果判定プログラム101を実行する。検出回路によってアサーション検証開始を検出し、コンピュータ100が、アサーション結果の判断タイミングを決定し、判定回路がアサーション検証の結果判定を行い、コンピュータ100が、判断タイミングにおいて結果判定を元にアサーション検証を行う。

(もっと読む)

1 - 20 / 122

[ Back to top ]