Fターム[2G132AK01]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | ICの形、ICの端子の構造 (103)

Fターム[2G132AK01]に分類される特許

1 - 20 / 103

半導体特性測定装置

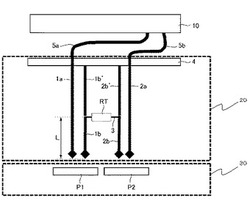

プローブカード、半導体装置、半導体装置の試験方法、及び、半導体装置の製造方法

【課題】差動伝送方式を採用した半導体装置の試験で行われるTDRタイミング測定の校正精度の低減を抑制すること。

【解決手段】複数のプローブ針を有し、プローブ針を半導体装置の電極パッドと接続させて所定の試験を行うためのプローブカードであって、互いに異なる電極パッドP1及びP2に接続するよう配置され、対となっている差動信号入力用の第1及び第2のプローブ針1a及び2aと、互いに異なる電極パッドP1及びP2に接続するよう配置された第3及び第4のプローブ針1b乃至2b´と、第3及び第4のプローブ針1b乃至2b´各々と接続して、第3及び第4のプローブ針1b乃至2b´を導通させる配線3及び抵抗部材RTと、を有し、第3及び第4のプローブ針1b乃至2b´、配線3及び抵抗部材RTは電気的にフローティングな状態となっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積を増大させることなく、針ずれに起因する誤測定や誤検査を防止することができる、半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、内部回路と、内部回路と電気的に接続されるとともに、検査装置に接続された複数の探針がそれぞれ接触する複数のパッドを備える。少なくとも2つのパッド2a、2bの間に、当該2つのパッド2a、2bを電気的に接続するとともに、所定の電流を印加することにより、恒久的に、電気的に切断されるヒューズ素子4が設けられる。パッド2a、2bの間の抵抗値を測定することで、針ずれの有無を検知することができる。その後、ヒューズ素子を切断し、内部回路の検査が実施される。

(もっと読む)

半導体装置

【課題】パッケージ内部の半導体チップが、BGA基板に接触しているか否かを、簡単に把握することが可能技術を提供する。

【解決手段】半導体チップ(2)は、回路接続用電極(4)と、回路から独立に設けられた第1検査用電極(11)と、第1検査用電極(11)に短絡された第2検査用電極(12)とを備える。基板(3)は、回路接続用電極(4)に対応する位置に配置される回路接続用基板側電極(5)と、第1検査用電極(11)に対応する位置に配置される第1検査用基板側電極(21)と、第2検査用電極(12)に対応する位置に配置される第2検査用基板側電極(22)とを備える。第2検査用電極(12)は、半導体チップ(2)と基板(3)とが正常に接続されるとき、第2検査用基板側電極(22)と電気的に絶縁する位置に配置される。

(もっと読む)

半導体装置、半導体装置の検査方法、及び、半導体装置の製造方法

【課題】半導体装置の製造工程の増大を抑制しつつ、パッドの針跡を容易に確認できるようにする。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に形成された回路素子と、半導体基板1上に形成され、回路素子と電気的に接続されたパッド(接続パッド4)と、を有している。パッドは、平面視において、導体が存在する実体パターン41と、前記導体が存在しない開口パターン42と、を含む所定のパターン形状に形成されている。

(もっと読む)

半導体装置及びそのテスト方法

【課題】複数のコアチップが積層された半導体装置において、各コアチップにそれぞれ任意のイネーブル信号を供給するために必要な貫通電極の数を削減する。

【解決手段】インターフェースチップIFと複数のコアチップCC0〜CC7が積層されており、複数のコアチップCC0〜CC7は、貫通電極TSV1を介してインターフェースチップIFに共通接続されており、インターフェースチップIFは、貫通電極TSV1を介して複数のコアチップCC0〜CC7にイネーブル信号TLSEをシリアルに供給し、複数のコアチップCC0〜CC7は、イネーブル信号TLSEを構成する複数ビットのうち当該コアチップに割り当てられたチップ識別情報に対応するビットの論理レベルに基づいて活性化される。本発明によれば、イネーブル信号を供給するために必要な貫通電極の数を削減することが可能となる。

(もっと読む)

半導体装置の検査方法、半導体装置および半導体基板

【課題】半導体装置の小型化を図りつつ、正確な故障箇所の位置の特定を可能とする。

【解決手段】半導体基板10の他面に溝部を形成する工程と、部品20と溝部の位置関係を示すレイアウトデータを取得する工程と、部品20に電圧を印加することにより、部品20の故障箇所50を発光させるとともに、故障箇所50からの発光を溝部の内部へ伝播させる工程と、故障箇所50からの発光により生じる第1の発光部の位置、および故障箇所50からの発光が溝部の内部を伝播することによって生じる第2の発光部の位置を他面側から検出する工程と、第1の発光部の位置および第2の発光部の位置から、溝部の位置を推定する工程と、推定した溝部の位置に対する第1の発光部の相対位置と、レイアウトデータにおける溝部の位置とを用いて、故障箇所を特定する工程と、を備える。

(もっと読む)

半導体装置

【課題】ウェハテストを必要とする半導体装置を縮小化を可能にすること。

【解決手段】半導体装置は、ボンディングパッドと、ボンディングパッドに電気的に接続されたボンディングワイヤと、ボンディングワイヤがボンディングパッドに接続される前のウェハ状態において電気的特性が試験される被試験回路と、被試験回路の試験のための端子となると共に、ボンディングパッドに隣接して配置され、ボンディングワイヤと接触している試験用パッドと、被試験回路の試験時に試験用パッドと被試験回路とを電気的に接続する試験用配線と、被試験回路の試験後に被試験回路と試験用パッドとの電気的接続を遮断する遮断機構と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数を増やさずに、安価な装置を用いてプロ―ビング位置の目視観察を可能にする。

【解決手段】本発明の半導体装置は、多層配線層(図示せず)と、多層配線層の最上層に形成され、ボンディング領域P1と試験用プローブ接触領域P2とを含むボンディングパッド200を有する。ボンディングパッド200には、ボンディング領域P1と試験用プローブ接触領域P2との境界を表す凹部202が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 半導体基板上に形成された半導体集積回路の、特にプローブ検査時間を短縮することができる検査工程を提供する。

【解決手段】 検査対象となる半導体基板には、半導体集積回路本体を含む回路領域2aと、それに隣接するスクライブエリアにTEG3aが形成され、回路領域2aには第1パッド電極5a、5bの列が、またTEG3aには第2パッド電極6の列が設けられる。ここでTEG3aに隣接している方の第1パッド電極5aが第2のパッド電極6に対向しないように配置される。このような状態の第1パッド電極5a、5bおよび第2パッド電極6にプローブ針8a、8b、9を接触させて半導体集積回路の検査とTEGの測定とを同時に行う。

(もっと読む)

段間プローブ用パターン構造、段間測定方法、およびマルチチップモジュール高周波回路

【課題】複数段のトランジスタで構成されるモジュールの段間のSパラメータが測定可能な段間プローブ用パターン構造、段間測定方法、およびマルチチップモジュール高周波回路を提供する。

【解決手段】誘電体基板と、誘電体基板の第1表面上に配置された第1信号伝送線路と、誘電体基板の第1表面上に前記第1信号伝送線路に隣接して配置された一対の第1接地端子電極と、第1接地端子電極の下部に配置された第1VIAホールと、誘電体基板の第1表面と反対側の第2表面に配置され、第1接地端子電極に対して第1VIAホールを介して接続された裏面接地電極とを備える。第1信号伝送線路には高周波プローブの信号端子が接続可能であり、一対の第1接地端子電極には、高周波プローブの一対の接地端子が接続可能である。

(もっと読む)

半導体集積回路

【課題】ウエハレベルパッケージにチップの欠けや樹脂の剥がれ等の欠陥があるかどうかを電気的に検出する。

【解決手段】外周配線14は、回路領域11とパッド電極P1〜P8の外の半導体基板10の4辺の外周に沿って配置されている。外周配線14は、パッド電極P1〜P8と同層又は上層の金属配線、もしくはポリシリコン配線により、半導体基板10上に形成される。外周配線14の第1の端に電源電位Vccが印加され、外周配線14の第2の端は抵抗R2を介して接地電位(Vss)が印加されている。検出回路15は、外周配線14と抵抗R2の接続点N1に接続され、該接続点N1の電位に基づいて、異常検出信号ERRFLGを発生するように構成されている。

(もっと読む)

半導体装置

【課題】半導体装置のプローブ試験で、プローブ針の数を必要最小限にすることと、半導体装置への電力供給マージンを提供する。

【解決手段】内部回路に電源を供給する隣り合う第1の電源パッド電極21及び第2の電源パッド電極22と、内部回路にグランドを供給する隣り合う第1のグランドパッド電極23及び第2のグランドパッド電極24と、前記第1及び第2の電源パッド電極のうち、一方の電源パッド電極はプローブ針4によって接続されていると共に、前記第1及び第2のグランドパッド電極のうち、一方のグランドパッド電極はプローブ針4によって接続されており、前記第1の電源パッド電極と前記第2の電源パッド電極はメタル配線10によって接続されて、同様に前記第1のグランドパッド電極と前記第2のグランドパッド電極はメタル配線10によって接続されていることを特徴とする。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】検査に用いるプローブの耐久性を向上できる半導体装置を提供する。

【解決手段】ウエハーのスクライブ線150上に配置された第1チェック素子1を具備する。第1チェック素子1は、第1配線絶縁膜5と、第1配線絶縁膜5の第1開口部に配置された第1チェック素子パッド10とを備える。第1チェック素子パッド10は、導電性の第1パッドメタル部12と、矩形の平面形状を有する絶縁性の第1ダミー部13とを含む。第1ダミー部13の平面形状は、スクライブ線150の長手方向と垂直な2つの第1長辺と、第1チェック素子パッド10の外周部近傍に配置される2つの第1短辺とを含む。

(もっと読む)

半導体装置の検査用素子及びその製造方法。

【課題】半導体装置の検査装置においては、非接触通信に適した構成を得ることが困難で、かつ高い信頼性を得ることが困難である。

【解決手段】本発明の半導体装置の検査用素子は、基材と、基材上に配置され検査回路と非接触結合回路を備えた回路層を有する検査回路基板と、検査回路基板との一の主面に接続され貫通電極を備えた支持基板とを有する。

(もっと読む)

半導体装置および半導体装置検査方法

【課題】半導体装置の検査をより容易にすること。

【解決手段】半導体チップ1と、半導体チップ1を封止するモールド樹脂3とを備えている。半導体チップ1は、複数の回路素子と、その複数の回路素子を電気的に接続する複数の配線とを備えている。モールド樹脂3は、その複数の配線のうちの1つの配線に電気的に接続される端子8−iを露出させる開口部14−iが形成されている。開口部14−iの口の径18は、端子8−iの径17より大きい。このような装置10は、平坦な面にこのような端子が形成される他の装置に比較して、プローブを開口部14−iに挿入することによりそのプローブをより容易に端子8−iに接触させることができ、より容易に検査されることができる。

(もっと読む)

半導体装置

【課題】一部のデータ入出力端子のみを用いて内蔵された複数の半導体チップを並列にテストすることのできる半導体装置を提供する。

【解決手段】複数の第1データ入出力端子と接続され、第1のテスト回路と、第1の記憶部とを有し、テスト動作時には、第1の記憶部から出力されるデータに応じて第1のテスト回路で第1のテスト結果を生成する第1の半導体チップと、複数の第2データ入出力端子と接続され、第2及び第3のテスト回路と、第2の記憶部とを有し、テスト動作時には、第2の記憶部から出力されるデータに応じて第2のテスト回路で第2のテスト結果を生成し、第2のテスト結果と第1の半導体チップの第1のテスト回路から供給される第1のテスト結果とに応じて第3のテスト回路で第3のテスト結果を生成し、第3のテスト結果を所定の第2データ入出力端子に出力する第2の半導体チップと、を備える。

(もっと読む)

半導体デバイス

【課題】データ入出力パッドとテストパッド間の経路や当該経路途中の回路の不良を検出することを可能とする方法を提供する。

【解決手段】半導体装置のテストのためのテストパッド(第2パッド22)と内部回路23との接続経路に、データ入出力のためのマイクロバンプパッド(第1パッド21)が配置されている。このため、前記第2パッド22を用いたテスト時に、前記内部回路23までの全経路の段線不良、回路不良が検出できる。

(もっと読む)

電子部品用パッケージ及びその実装方法

【課題】 金リボンなどの金属リボンを接続する平坦度の良い外部接続用端子を備え、加えて評価用リードも備える電子部品用パッケージを得る。

【解決手段】 セラミックベースと、前記セラミックベースの内側に設けられ、内部に電子部品が収納され、カバーで封止されたキャビティと、前記キャビティより外側へ突出した前記セラミックベースの上面に形成され、前記電子部品と接続された電極と、前記電極にろう付けされた評価用リードと、前記電極に接続され、前記電極に併置された導体パターンで形成された外部接続用端子とで構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】中間配線層までの配線が行われているマスターウェーハを使用しても、最終製品の歩留りを高い精度で予測することができる半導体装置およびその製造方法を提供する。

【解決手段】多層配線構造の中間配線層までを使用して機能動作を行うように設計された機能ブロック(SRAMマクロ11、ロジックブロック12、ロジックブロック13、IPブロック14)を搭載したマスターウェーハを使用するマスタースライス方式の半導体装置は、この中間配線層に試験用パッドTPを備え、この試験用パッドTPが、各機能ブロックに接続される。

(もっと読む)

1 - 20 / 103

[ Back to top ]