Fターム[2G132AK08]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 排他的論理和を用いるもの (69)

Fターム[2G132AK08]に分類される特許

1 - 20 / 69

自己診断機能付き装置

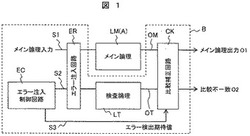

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

書込回路、半導体集積回路、及び書込方法

【課題】アンチヒューズ型のOTPメモリへの書き込み時間を短縮化すること。

【解決手段】書込回路は、OTPマクロに対して書き込むデータを記憶する記憶部と、前記書き込むデータの書き込みを前記OTPマクロに実行させる第一の信号を印加し、前記OTPマクロが記憶しているデータの読み出しを前記OTPマクロに実行させる第二の信号を印加する制御部と、前記第二の信号に応じて前記OTPマクロから読み出されたデータと、前記記憶部が記憶するデータとを比較し、比較結果を出力する比較部とを有し、前記制御部は、前記比較結果が一致を示す場合、前記書き込むデータに関する処理を終了し、前記比較結果が不一致を示す場合、前記第一の信号及び前記第二の信号の印加を再度行う。

(もっと読む)

集積回路および集積回路の接続不良検出方法

【課題】製品組立後の経年劣化による接続不良を含め、簡単な構成で被実装基板との接続不良を検出する。

【解決手段】集積回路に、同一の電位が与えられる2以上の比較電圧用パッドと、比較電圧用パッドにかかる電圧を比較して、その比較結果に基づいて被実装基板との接続不良の有無を示す信号を出力する比較判別回路とを設け、比較判別回路において、少なくとも2つの比較電圧用パッドにかかる電圧の電位差が所定の値を超えた場合に、接続不良を示す信号を出力させる。

(もっと読む)

故障箇所推定装置と方法並びにプログラム

【課題】スキャンテスト設計が施された機能ブロックと付加回路とを含む論理回路全体を故障診断を可能とし、診断処理時間を大幅に短縮可能とする装置、方法の提供。

【解決手段】論理回路内のスキャンフリップフロップで構成されるスキャンチェーンの構成情報、論理回路の設計情報を入力データ1として入力し、論理回路においてパラレル領域以外の回路部をシリアル領域として抽出することで、前記論理回路を前記パラレル領域とシリアル領域に分割する回路分割手段2と、正常回路における論理値を期待値として求める期待値計算手段3と、テストパタンに対する論理回路のテスト出力を入力データ1として入力し、テスト出力および、シリアル領域とパラレル領域の期待値を用いて、パラレル領域およびシリアル領域を故障診断し、出力部に出力する故障診断手段4とを備える。

(もっと読む)

半導体集積回路のテスト回路及び半導体集積回路のテストの制御方法

【課題】実動作周波数を用いて半導体集積回路をテストする際のテスト時間を短縮すること。

【解決手段】複数のテスト項目を含むテストにおけるテスト項目ごとの成否の判定結果について、所定数を単位とする複数のデータ群に組分けし、当該データ群内に判定結果がエラーを示すデータが含まれる場合、当該データ群内の全てのデータを当該エラー値に置換し、置換されたデータ群内の各データをシリアル出力する差分吸収部を備える半導体集積回路のテスト回路。

(もっと読む)

マルチステージ・テスト応答コンパクタ

【課題】より高い圧縮比を提供し得る圧縮スキームを提供する。

【解決手段】いわゆる「Xプレス」テスト応答コンパクタ110、152は、オーバードライブ・セクションとスキャンチェーン選択ロジックとを含む。実施形態は約1000倍の圧縮比を提供する。例示的な実施形態は、従来のスキャンベースのテストシナリオとほぼ同じカバレッジおよびほぼ同じ診断分解能を維持できる。スキャンチェーン選択スキームのいくつかの実施形態は、テスト応答で発生してコンパクタに入る未知状態を有意に減らすことができ、または完全に排除できる。また、オンチップ・コンパクタ回路の実施形態および選択回路をマスクする制御回路網を生成する方法も開示する。

(もっと読む)

故障診断システム、半導体集積回路及び故障診断方法

【課題】固定数の出力端子を用いて、複数の入力信号の中から故障の原因となる信号を特定して故障を診断すること。

【解決手段】第1の入力テスト信号と、当該第1の入力テスト信号の期待値である第1の期待値と、のいずれかを選択して出力する第1の選択回路と、第2の入力テスト信号と、第1の選択回路からの出力信号との一致判定結果を出力端子へ出力する第1の論理回路と、を有する第1の圧縮回路と、第1の選択回路により第1の入力テスト信号が選択された際の出力端子からの第1の出力結果がエラーを示す場合に、第1の選択回路に対して第1の期待値を選択させ、第1の出力結果がエラーを示すことに伴い第1の選択回路により第1の期待値が選択された際の出力端子からの第2の出力結果が正常を示す場合に、第1の入力テスト信号をエラーと特定し、第2の出力結果がエラーを示す場合に、第2の入力テスト信号をエラーと特定する選択制御回路とを備える。

(もっと読む)

半導体装置、半導体装置におけるメモリの試験方法および試験プログラム

【課題】複数のメモリを有効活用し、CPUの負担を軽減することでメモリの迅速な試験が可能な半導体装置、半導体装置におけるメモリの試験方法および試験プログラムを得ること。

【解決手段】半導体装置10のメモリのうちの異常のないメモリに試験データを書き込み、試験の対象の他のメモリにアドレスを順時指定してデータコピー手段14で試験データをコピーする。その後、両メモリの領域を順次切り替えながら対応する領域ごとにデータを読み出して排他的論理和手段16で排他的論理和をとり、全領域についてこれらの論理和が「0」のとき、試験の対象となるメモリを正常であると判別する。

(もっと読む)

検査装置、および集積回路

【課題】簡易な構成により、検査対象装置のシリアルインターフェースの検査を容易化する。

【解決手段】検査装置10は、第一ビット長のパラレル信号をシリアル信号に変換し、該シリアル信号を外部に出力するDUT(検査対象装置)20を検査するものであって、DUT20は、検査の際、後述する排他的論理和の各値から成るパターンが、第二ビット長を有する所定パターンとなるように構成されている検査用データを、シリアル信号に変換するものであり、検査用データが変換されたシリアル信号をDUT20から受信する信号受信部11と、該受信したシリアル信号を、任意のビット位置から順次、第二ビット長のパラレル信号に変換するシリアルパラレル変換部12と、整数個連続して変換された第二ビット長のパラレル信号のそれぞれにおける、同一ビット位置のビット値の排他的論理和を、全てのビット位置について算出する演算部14とを備える。

(もっと読む)

電源制御可能領域を有する半導体集積回路

【課題】電源制御可能領域を有する半導体集積回路において、電源制御動作のテストをできる半導体集積回路を提供する。

【解決手段】電源制御スイッチ310A、310Bは、複数のスイッチセル17で構成されるスイッチ系列310A、310Bを有する。電源制御可能領域300は、出力ノード330A、330Bをスイッチ系列ごとに備える。出力ノード330A、330Bは、電源制御スイッチの各スイッチ系列310A、310Bの最終段を通過した電源制御信号CTLを電源制御可能領域300の外部に出力する。チップは、出力ノード330A、330Bからの出力を外部に出力する出力端子340A,340Bを備える。スキャンパステストを挿入する場合、観測用フリップフロップを各出力ノードに対応して設ける。これら観測用フリップフロップがスキャンパスチェーンを構成するように接続する。

(もっと読む)

半導体装置

【課題】複数の入出力端子へ縮退データを入出力できる半導体装置を提供する。

【解決手段】半導体装置100は、第1の組に属する入出力パッド2Aと第2の組に属する入出力パッド2Bを備えている。また、入出力パッド2A、2Bには、それぞれインバータ回路3A、3Bが接続されている。テストモードにおける読み出し動作において、インバータ回路3Aに接続される信号線OUT0U/Dと、インバータ回路3Bに接続される信号線OUT1U/Dとに、互いに排他的な論理レベルの信号が入力されるテスト回路を有することを特徴とする。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】内蔵されたクロックジェネレータの出力クロック周波数の変動をLSIチップ外部でデジタルテスタにより容易に試験できる半導体集積回路を提供する。

【解決手段】半導体集積回路は、周波数が固定の第1のクロック信号を入力として時間とともに周波数が変動する第2のクロック信号を生成するクロック生成器と、前記第1のクロック信号と前記第2のクロック信号とに基づくデジタル論理演算により前記第1のクロック信号に対応する第1の周波数と前記第2のクロック信号に対応する第2の周波数との差に応じたデジタル信号を生成する試験回路と、前記試験回路が生成するデジタル信号を外部に出力する信号経路とを含むことを特徴とする。

(もっと読む)

テスト回路

【課題】従来の半導体装置では、複数の被テスト回路からのテスト結果の読み出しに大きな労力が必要になる問題があった。

【解決手段】本発明にかかるテスト回路は、第1の被テスト回路13aがテスト命令に従って出力する第1のテスト結果信号S1と、第2の被テスト回路13bがテスト命令に従って出力する第2のテスト結果信号S2と、を合成する合成回路15と、第1のテスト結果信号S1に対して第2のテスト結果信号S2を遅延させるブロック間遅延生成回路14と、合成回路15が出力する合成テスト結果信号を所定のタイミング毎に保持するテスト結果保持回路16と、を有するものである。

(もっと読む)

半導体集積回路、及び設計自動化システム

【課題】スキャンテスト実行時における瞬間電力を低減する。

【解決手段】スキャンチェーン回路1は、通常動作時には、組み合わせ論理回路2に入出力されるデータを一時保持する一方、スキャンテスト実行時には、複数個のフリップフロップF/Fをシフトレジスタとして機能させテストパターン信号SCANInをシリアル転送する。クロックゲーティング回路3は、クロックゲーティング信号CGSに従いクロック信号CLKのパルスの出力を制御する一方、スキャンイネーブル信号が立ち上がっている間クロックゲーティング信号CGSを無効化する。クロックゲーティング回路3bは、スキャンイネーブル信号SCANEnが立ち上がっている間クロックゲーティング信号CGSを無効化すると共にクロック信号CLKを反転させる。

(もっと読む)

イコライザのテスト回路および集積回路の評価システム

【課題】量産テストでの使用に適したイコライザのテスト回路および集積回路の評価システムを提供する。

【解決手段】テスト回路1は、擬似乱数データ生成部11が、擬似乱数データを生成し、重み付け係数生成部12が、符号間干渉の干渉強度設定用の重み付け係数を生成し、擬似符号間干渉データ生成部13が、擬似乱数データのビット系列に応じて擬似乱数データに擬似的な符号間干渉を発生させ、重み付け係数により振幅を変化させた擬似符号間干渉データを生成し、ドライバ14が、生成された擬似符号間干渉データを差動信号として出力する。比較部15は、イコライザ100の出力をサンプリング回路200によりサンプリングしたデータを、符号間干渉発生前の元の擬似乱数データと比較し、カウント部16が、比較部15により検出された不一致の数をカウントする。

(もっと読む)

モニタ回路及び電力低減システム

【課題】LSIテスト時においても選別用のモニタリングを行うことができると共に、小さな面積で簡便な構成によりモニタ可能なモニタ回路を提供すること。

【解決手段】モニタ回路は、クロック信号39に同期して入力信号を取り込むフリップフロップ回路32と、クロック信号40に同期して入力信号を取り込むフリップフロップ回路34と、フリップフロップ回路34の出力信号を受ける論理回路37と、クロック信号40に同期して論理回路37の出力信号を取り込むフリップフロップ回路35とを含み、クロック信号40の立ち上がりエッジ位置を調整し、フリップフロップ回路32の出力信号とフリップフロップ回路35の出力信号とが所定の組合せとなったときの、調整したクロック信号40の立ち上がりエッジ位置とクロック信号39の立ち上がりエッジ位置とに基づいてチップの性能を判別する。

(もっと読む)

半導体集積回路

【課題】本発明は、スキャンシフト動作時におけるデータ遷移による電力消費を削減した半導体集積回路を提供することを目的とする。

【解決手段】半導体集積回路は、第1のスキャンフリップフロップ及び第2のスキャンフリップフロップを含みスキャンチェーンを構成する複数のスキャンフリップフロップと、該第1のスキャンフリップフロップのスキャン出力を第1の入力として受け取り、該第2のスキャンフリップフロップのスキャン出力を第2の入力として受け取り、該第1の入力及び該第2の入力の排他的論理和の論理値と該第1の入力の論理値との何れか一方の論理値を、制御信号に応じて選択的に該第2のスキャンフリップフロップのスキャン入力に供給する論理回路とを含む。

(もっと読む)

テスト回路

【課題】従来のテスト回路は、テスト端子の削減が十分にできない問題があった。

【解決手段】本発明のテスト回路は、同一の回路構成及び同一の機能を有する複数の回路ブロックと、複数の回路ブロックのそれぞれに対応して設けられる複数のテスト回路と、複数のテスト回路が出力するテスト結果TDOa〜TDOcの論理和演算結果を第1の結果信号Xとして出力する論理和回路11と、複数のテスト回路が出力するテスト結果TDOa〜TDOcの論理積演算結果を第2の結果信号Yとして出力する論理積回路12と、第1の結果信号X及び第2の結果信号Yの一致比較結果を最終結果信号Zとして出力する判定回路13と、を有するものである。

(もっと読む)

半導体装置

【課題】本発明は、実動作中の回路誤動作を認識することができ、また回路誤動作の箇所を特定できる半導体装置や、誤動作を修復する際に次段の回路において誤動作を誘因させることのない半導体装置を提供することを目的とする。

【解決手段】本発明は、複数の論理回路と、論理回路からのデータに基づき誤動作判定を行う複数の判定回路とを備える半導体装置である。そして、判定回路は、第1レジスタ(R1)と、遅延手段(バッファ1)と、第2レジスタ(R2)と、比較器3と、スキャン化手段とを備えている。スキャン化手段は、比較器3の比較結果を保持させつつ、第2レジスタ(R2)をシフトレジスタ化して第2レジスタ(R2)で保持したエラー信号を次段へ伝搬させる。

(もっと読む)

テスト構成の半導体集積回路

【課題】部分ローテート型スキャン回路を用いたテスト構成の半導体集積回路において、面積オーバーヘッドを大幅に削減することが可能な構造を得る。

【解決手段】組合せ回路(3)と、複数のスキャン用フリップフロップ(5)をチェーン接続して構成したスキャンチェーン(2)とを備えるテスト構成の半導体集積回路において、スキャンチェーン(2)は複数の部分スキャンチェーン(20a〜20n)に分割され、各部分スキャンチェーン(20a〜20n)は部分ローテート型スキャン(PRS)機能とテスト応答圧縮(MISR)機能とを備える。PRSとして設定する部分スキャンチェーンとMISRとして設定する部分スキャンチェーンの組合せを変えて、複数のステップでスキャンテストを実行することによって、スキャンチェーンとは別にテスト応答圧縮器を設けることなくテストを行うことができるので、面積オーバーヘッドが削減される。

(もっと読む)

1 - 20 / 69

[ Back to top ]