Fターム[2G132AK09]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 比較判定回路を用いるもの (193)

Fターム[2G132AK09]に分類される特許

1 - 20 / 193

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

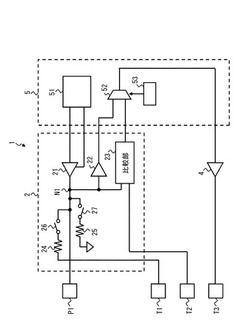

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

半導体集積回路および半導体集積回路のテスト方法

【課題】小さな回路規模で複数のパラレルシリアル変換回路を確実にテストすることが可能な半導体集積回路等を提供する。

【解決手段】第1および第2のパラレルシリアル変換回路と、第1および第2のテスト用パラレルデータ列を生成するテスト用パラレルデータ列生成回路と、第1および第2のパラレルシリアル変換回路が変換した第1および第2のシリアルデータビットの一致/不一致を検出する検出回路とを備えた半導体集積回路において、テスト用のパラレルデータ列生成回路が共通のテスト用パラレルデータ列を構成するそれぞれのパラレルデータのビットを第1のビット数だけシフトして第2のテスト用パラレルデータ列を生成するパラレルビットシフト回路を含み、検出回路が第1のシリアルデータと第2のシリアルデータとの一方のビットをシフトして比較回路に入力されるタイミングをそろえるシリアルビットシフト回路とを含む。

(もっと読む)

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

半導体装置、試験プログラム、試験方法、および試験装置

【課題】特定パスの動作確認を容易化し、不具合箇所の特定を容易化すること。

【解決手段】選択回路101は、入力信号が入力端子120から受け渡される半導体装置110内の特定パス上の観測箇所Aと観測箇所Bとが選択信号に応じて順に選択される。カウンタ102は、選択された観測箇所ごとに観測箇所でのエッジ数をカウントする。第1のレジスタ103は、カウンタ102によりカウントされた観測箇所Aでの第1のエッジ数を保持する。第2のレジスタ104は、カウンタ102によりカウントされた観測箇所Bでの第2のエッジ数を保持する。比較回路105は、第1のレジスタ103に保持された第1のエッジ数と第2のレジスタ104に保持された第2のエッジ数とを比較し、出力端子106は、比較回路105による比較結果を出力する。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において、入力端子のオープン異常を、素子の追加量を抑えつつ且つ入力特性に影響を与えずに、検出可能にする。

【解決手段】マイコン21は、センサ信号を入力するための入力端子23が、プリント基板11の信号配線16に接続される。また、マイコン21において、電源電圧(5V)のラインとグランドラインとの各々と、入力端子23との間には、寄生ダイオードD1,D2がサージ電圧保護用のクランプダイオードとして機能するトランジスタ(MOSFET)T1,T2が接続されている。そして、マイコン21は、例えばトランジスタT2の方をハーフオン状態に駆動する駆動回路29を有しており、トランジスタT2をオフさせているときの入力端子23の電圧と、トランジスタT2をハーフオン状態に駆動したときの入力端子23の電圧とに基づいて、入力端子23が信号配線16と非接続になった異常(オープン異常)の有無を判定する。

(もっと読む)

半導体集積回路装置およびテストモード設定方法

【課題】簡易な回路で、よりセキュリティ性を向上させる。

【解決手段】半導体集積回路装置(100)は、複数の機能ブロック(125−127)と、取り込み部(131)と、検出部(132)と、判定部(150)とを具備し、動作パターンが所定の規則に従って変化したときにテストモードに移行する。複数の機能ブロック(125−127)は、制御装置(200)からの指示に応答して動作する。取り込み部(131)は、複数の機能ブロック(125−127)のそれぞれの動作状態を示す信号を取り込む。検出部(132)は、複数の機能ブロック(125−127)のうちの少なくとも1つの機能ブロックの動作状態の変化を検出する。判定部(150)は、取り込まれた動作状態を示す信号によって示される動作パターンが所定の規則に従って変化するか否かを判定する。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム。

【課題】内部信号線の寄生抵抗値を測定できるようにする。

【解決手段】インターフェースチップとコアチップとを電気的に接続する1又は複数の内部信号線101を備え、インターフェースチップは、内部配線に電流を出力する第1の回路111を有し、コアチップは、第1の内部信号線101に電流を出力する第2の回路121を有し、インターフェースチップは、第1の回路111が出力する電流が流れる上記内部配線に接続される第1の入力端子151aと、第1の内部信号線101のインターフェースチップ内の端部101aに接続される第2の入力端子151bとを有し、第1の入力端子151aの電圧と第2の入力端子151bの電圧との電位差に応じた電圧を出力する判定回路150を有する。

(もっと読む)

スキャンパス内蔵半導体集積回路

【課題】既存のテスト回路を用いて簡単な回路や制御を追加することでセキュリティ性を高める。

【解決手段】スキャンレジスタ方式の回路を保持したLSIにおいて、スキャン入力端子181〜183から入力したパスワードを、パスワード入力レジスタ101〜103に保持する。パスワード入力レジスタ101〜103とマスター・パスワード131〜133とをそれぞれ比較器111〜113で比較し、結果をパスワード判定回路100に送る。比較結果が全て一致していたら、スキャンパス・チェーン191〜193と出力バッファ151〜153との間の経路をスルーにする。逆に比較結果に不一致がある場合は、スキャンパス・チェーン191〜193と出力バッファ151〜153との間の経路を遮断する。

(もっと読む)

プログラム可能論理デバイス及びその試験方法

【課題】内蔵の記憶装置の試験回路を自動的に作成し、その試験回路を用いて記憶装置の試験を自動的に行うことで、記憶装置の試験にかかる時間を短縮することが可能なプログラム可能論理デバイスを提供する。

【解決手段】データを記憶する記憶部1を備える。論理回路記憶部2は、記憶部1への書き込み及び読み出しを伴うデータ処理を行う論理回路である内部回路を格納する。部品回路記憶部5は、記憶部1の試験のための部品回路を予め記憶しておく。ピン情報記憶部3は、記憶部1のピン情報を取得する。試験部4は、ピン情報及び部品回路を基にメモリ試験回路を生成し論理回路記憶部2に格納させ、メモリ試験回路を用いて記憶部1の試験を行う。

(もっと読む)

検査装置、および集積回路

【課題】簡易な構成により、検査対象装置のシリアルインターフェースの検査を容易化する。

【解決手段】検査装置10は、第一ビット長のパラレル信号をシリアル信号に変換し、該シリアル信号を外部に出力するDUT(検査対象装置)20を検査するものであって、DUT20は、検査の際、後述する排他的論理和の各値から成るパターンが、第二ビット長を有する所定パターンとなるように構成されている検査用データを、シリアル信号に変換するものであり、検査用データが変換されたシリアル信号をDUT20から受信する信号受信部11と、該受信したシリアル信号を、任意のビット位置から順次、第二ビット長のパラレル信号に変換するシリアルパラレル変換部12と、整数個連続して変換された第二ビット長のパラレル信号のそれぞれにおける、同一ビット位置のビット値の排他的論理和を、全てのビット位置について算出する演算部14とを備える。

(もっと読む)

半導体集積デバイスのテスト回路、テスト方法及びプログラム

【課題】複数のI/Oバッファ間における相対的な差を測定し、I/Oバッファの複数信号の相対的な差が許容範囲にあれば正常な半導体集積デバイスと判定し、いままでは不良のデバイスであると判定されていたものを救済する。

【解決手段】半導体集積デバイスにおいて、ドライバ、複数のレシーバ、インバータによって発振回路を構成し、この発振回路の出力をクロック入力とする2個以上のカウンタと、カウント値を比較するコンパレータの比較結果により半導体集積デバイスの良否を判定する。

(もっと読む)

テストモード付きフラッシュメモリ及びその接続試験方法

【課題】フラッシュメモリとその周辺回路との接続性試験を上位アドレス線を含めて適確に行なう。

【解決手段】コマンドデコーダ603は、外部ピンからの入力信号が特定のアドレスに対する特定の値の書き込みであることを検出する。ステートデコーダ602は、ステートマシン307の状態が所定のモードであるCFIクエリモードであるかを判定する。判定回路604は、ステートデコーダ602がCFIクエリモード配下でコマンドデコーダ603の検出出力とに基づいてテストモードになったことを判定する。データ保持回路605は、判定回路604の判定出力をセットし、テストモードになったことを示すテストモード表示信号403を保持する。テストモードにおいては、例えばアドレス線の上位側をデータ線に出力する。

(もっと読む)

回路試験装置

【課題】簡易な構成で論理回路を用いたシステムを停止させることなく論理回路の試験を行なう回路試験装置を得ること。

【解決手段】システムの動作の一部を実行する試験対象部と同じ機能を有した論理回路をFPGAを用いて再構成する試験対象機能代替部11を備え、試験対象入力選択部15は、試験対象部10の試験が行なわれる際には試験データ準備部16からの試験情報を選択して試験対象部10に出力し、且つ試験対象部がシステムの動作の一部を実行する際にはシステム前段P1からの入力情報を選択して試験対象部10に出力し、有効回路選択部14は、試験対象部の試験が行なわれる際には再構成後の試験対象機能代替部11による処理結果を選択してシステム後段Q1側へ出力し、且つ試験対象部10がシステムの動作の一部を実行する際には試験対象部10による処理結果を選択してシステム後段Q1側へ出力する。

(もっと読む)

故障検出方法、半導体装置、マイクロコンピュータ応用システム

【課題】故障検出の対象とされる回路のアナログ量を変化させて故障検出を行うことにより、故障検出精度を向上させる。

【解決手段】チューニング回路(104A)によって、所定の条件下で上記被故障検出回路(104B)のアナログ量を変更し、上記被故障検出回路におけるアナログ量の変化に基づく上記被故障検出回路の状態変化を、故障検出回路(103)によって判別して上記被故障検出回路の故障を検出する。これにより、故障検出回路(103)の出力を半導体装置の外部でモニタすることなく、上記被故障検出回路の故障を検出することができる。しかも、上記被故障検出回路におけるアナログ量の変化に基づく上記被故障検出回路の実際の状態変化を故障検出回路によって判別するようにしているため、故障検出の精度の向上を図ることができる。

(もっと読む)

アナログ電圧調整回路、及びアナログ電圧調整方法

【課題】検査工程と調整工程をほぼ同時に実行可能な、アナログ電圧調整回路を提供する。

【解決手段】アナログ電圧調整回路1は、外部装置から、目標電圧を示す目標電圧信号を入力する、目標電圧入力端子12と、目標電圧信号に基づいて生成された目標電圧を示すデータを取り込み、期待値データとして格納する、期待値データ格納回路7と、トリミングデータを格納し、トリミングデータに応じたトリミング信号を出力する、トリミングデータ格納回路11と、トリミング信号を取得し、トリミングデータに応じた電圧レベルで、アナログ出力信号を出力する、アナログ信号出力回路2と、アナログ出力信号の電圧レベルを示す測定データと、格納された前記期待値データとを比較し、比較結果を示す比較結果信号を生成する比較回路8と、比較結果信号に基いて、トリミングデータを変更するか否かを決定する、制御回路10とを具備する。

(もっと読む)

自己診断システム及び検査回路判定方法

【課題】テスト対象回路の診断を実行する検査回路の正常性を判定することができる自己診断システム及び検査回路判定方法を提供すること

【解決手段】本発明にかかる自己診断システムは、テスト対象回路10におけるテストパタンの実行結果を用いて、テスト対象回路10の正常性を判定する診断コントローラ31及び32を有する検査回路30と、診断コントローラ31から出力されるテスト対象回路10の正常性判定結果と、診断コントローラ32から出力されるテスト対象回路10の正常性判定結果とを比較して、検査回路30の正常性を判定する検査回路判定部20と、を備えるものである。

(もっと読む)

半導体集積回路装置

【課題】特定のモニタ回路が動作不良であったり、モニタ回路内のリングオシレータを構成する一部の素子の特性に異常があったりした場合、最も動作速度の遅いモニタの結果に基づいて電圧制御をおこなうと、必要電圧を過大に見積もる恐れがある。その結果、消費電力の増加を招き、また、複数モニタの検出結果の平均値をとる際にも精度が低下する。

【解決手段】複数のモニタ回路を設け、それらの検出結果の内、所定の範囲から外れたものについては検出結果を無視して残りのモニタ結果の平均値を最終的なモニタ検出値とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップのテスト時間を短縮可能な半導体装置の製造方法を提供する。

【解決手段】半導体ウエハ10a,10bに、パッドとを有し、且つパッドが半導体チップ11a,11bの主面に形成されたパッド16a,16bと半導体チップの主面と相対向する半導体ウエハの主面に形成されてパッドと電気的接続されたパッド17a,17bとを有するテスト回路を内蔵した半導体チップを複数、形成する工程と、複数の半導体ウエハを、隣接する半導体ウエハにおける半導体チップの入力パッドの各々を互いに接触させて検査装置40のステージ上に載置する工程と、載置された複数の半導体ウエハのうち外側の半導体ウエハにおける半導体チップのパッドに検査装置40のプローブ針43を接触し、半導体チップの各々を一括でテストする工程とを備えることを特徴とする半導体装置。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】検査用回路を備えた半導体装置において、所望のタイミングで検査対象回路部の動作を確認することができない

【解決手段】本発明の半導体装置は、検査対象回路部と、検査回路部を有し、検査回路部は、信号入力部と、比較部と、制御回路部を備え、制御回路部は、信号入力部と比較部と検査対象回路部に接続され、信号入力部は、検査用信号または検査期待値を取得し、検査用信号を制御回路部に送出し、制御回路部は、検査用信号を検査対象回路部に送出し、検査用信号に基づいて検査対象回路部が出力する動作信号を取得して比較部に送出し、比較部は、同期信号に基づいて検査期待値と動作信号を比較した比較結果を出力する。

(もっと読む)

1 - 20 / 193

[ Back to top ]